一种减少重掺杂8英寸衬底外延片背面晶点缺陷的外延方法与流程

本发明涉及半导体材料制造领域,具体涉及一种减少重掺杂8英寸衬底外延片背面晶点缺陷的外延方法。

背景技术:

1、在外延片生长工艺中,对于重掺杂as(砷)、p(磷)的衬底,在高温下其掺杂元素十分容易扩散,而外延生长的过程持续保持高温,因此在生产中需要防止掺杂元素的扩散。目前的常用工艺为:最终抛光前,在衬底背面淀积一层背封膜,该背封膜层的材料通常为氧化硅、氮化硅、多晶硅。

2、在背封过程中,若衬底背面边缘处薄膜不均匀或移除边缘薄膜不完全,薄膜较薄处或没有被薄膜覆盖处将出现衬底裸露的情况,在生长外延层的时候,将沿着裸露部分进行生长,而其余区域由于背封膜的存在无法沉积,因此会在外延片边缘形成一圈背面晶点缺陷,影响外延片的质量。

技术实现思路

1、发明目的:本发明的目的是提供一种能够显著减少重掺杂8英寸衬底外延片背面晶点缺陷的外延方法。

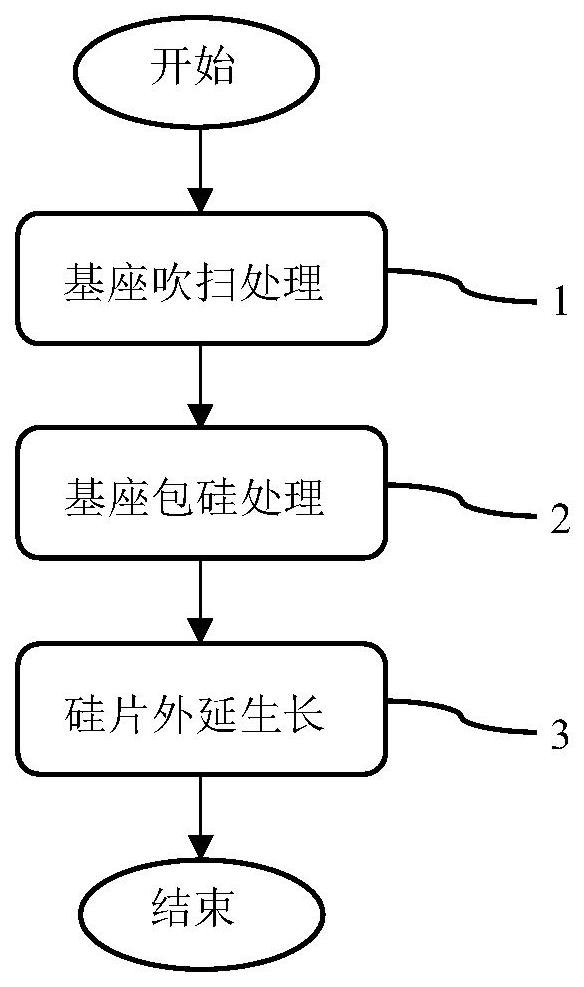

2、技术方案:一种减少重掺杂8英寸衬底外延片背面晶点缺陷的外延方法,包括以下步骤:

3、(1)反应腔内通入hcl,对基座进行吹扫处理;

4、(2)基座吹扫处理后,向反应腔内通入sihcl3和h2,进行基座包硅处理,在基座表面生长薄层硅;

5、(3)基座包硅处理后,放入硅片衬底,进行外延片的外延生长。

6、优选的,步骤(1)中,温度设置为1160~1170℃。

7、优选的,步骤(1)中,hcl流量为20slm。

8、优选的,步骤(1)中,吹扫处理时间为25~35s。

9、优选的,步骤(2)中,sihcl3流量为6~12g/min。

10、优选的,步骤(2)中,h2流量为60~80slm。

11、优选的,步骤(2)中,基座包硅处理的时间为5~10s,包硅处理得到的薄层硅厚度为0.3~0.6μm。

12、优选的,步骤(3)中所述掺杂as的8英寸硅片衬底,其电阻率为0.002~0.003ω·cm。

13、优选的,步骤(3)中,外延生长的温度设置为1080~1100℃。

14、优选的,步骤(3)中,外延片的生长速率设置为3.5~3.8μm/min。

15、有益效果:与现有技术相比,本发明的显著效果是:通过预先进行基座包硅处理,对衬底背面起到保护作用,在外延过程中减少了反应气体的渗入,从而在重掺杂衬底基础上进行外延生长时,显著减少外延片背面晶点缺陷数量。

技术特征:

1.一种减少重掺杂8英寸衬底外延片背面晶点缺陷的外延方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的外延方法,其特征在于:步骤(1)中,温度设置为1160~1170℃。

3.根据权利要求2所述的外延方法,其特征在于:步骤(1)中,hcl流量为20slm。

4.根据权利要求3所述的外延方法,其特征在于:步骤(1)中,吹扫处理时间为25~35s。

5.根据权利要求1所述的外延方法,其特征在于:步骤(2)中,sihcl3流量为6~12g/min。

6.根据权利要求5所述的外延方法,其特征在于:步骤(2)中,h2流量为60~80slm。

7.根据权利要求6所述的外延方法,其特征在于:步骤(2)中,基座包硅处理的时间为5~10s;包硅处理得到的薄层硅厚度为0.3~0.6μm。

8.根据权利要求1所述的外延方法,其特征在于:步骤(3)中所述掺杂as的8英寸硅片衬底,其电阻率为0.002~0.003ω·cm。

9.根据权利要求8所述的外延方法,其特征在于:步骤(3)中,外延生长的温度设置为1080~1100℃。

10.根据权利要求9所述的外延方法,其特征在于:步骤(3)中,外延片的生长速率设置为3.5~3.8μm/min。

技术总结

本发明提供一种减少重掺杂8英寸衬底外延片背面晶点缺陷的外延方法。通过在外延生长前对反应腔内基座进行预先包硅处理,在基座表面生长薄层硅,对重掺杂8英寸衬底背面起到保护作用,在外延过程中减少了反应气体的渗入,有效的改善了带有背封膜结构的重掺杂8英寸衬底在外延生长时形成背面晶点缺陷的问题,且生产出的外延片参数均匀性有一定提升。

技术研发人员:郭佳龙,谢进,邓雪华,刘哲洋

受保护的技术使用者:南京国盛电子有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!