一种片上集成偏置电路光电探测器的制备方法与流程

本发明涉及光电探测,具体地说是一种片上集成偏置电路光电探测器的制备方法。

背景技术:

1、在未来的大容量光纤通信系统中,能够提供高速、高响应性和高饱和输出的光电探测器模块是非常必要的。这是因为,如果光电二极管的输出功率足够高,当用光放大的强信号进行光照射时,就不需要宽带电子放大器,那么光电接收器的结构就可以大大简化。其中,采用面入射方案传统光电探测器,受到响应度和响应带宽的相互制约,因此芯片带宽和最大输出功率受限。采用边入射波导结构方案的新型器件设计,可以提高饱和功率的同时还可以提升光探测器的带宽,而提高带宽需要光纤和芯片边入射波导之间高效耦合。

2、目前波导型的光电探测器越来越受到关注,但是对于光电探测器模块来说,需要对光电探测器进行封装,为了降低封装寄生参数对探测器芯片本征参数的影响,需要对封装的外围偏置电路进行详细设计。但受限于目前的制作工艺,很难将电阻电容参数做得很小,哪怕把电阻电容参数和尺寸做到很小后,对于额外的贴片打线又是难题,封装严重限制了芯片的带宽。

技术实现思路

1、为了解决上述技术问题,本发明提供一种片上集成偏置电路光电探测器的制备方法,以解决背景技术中存在的问题。

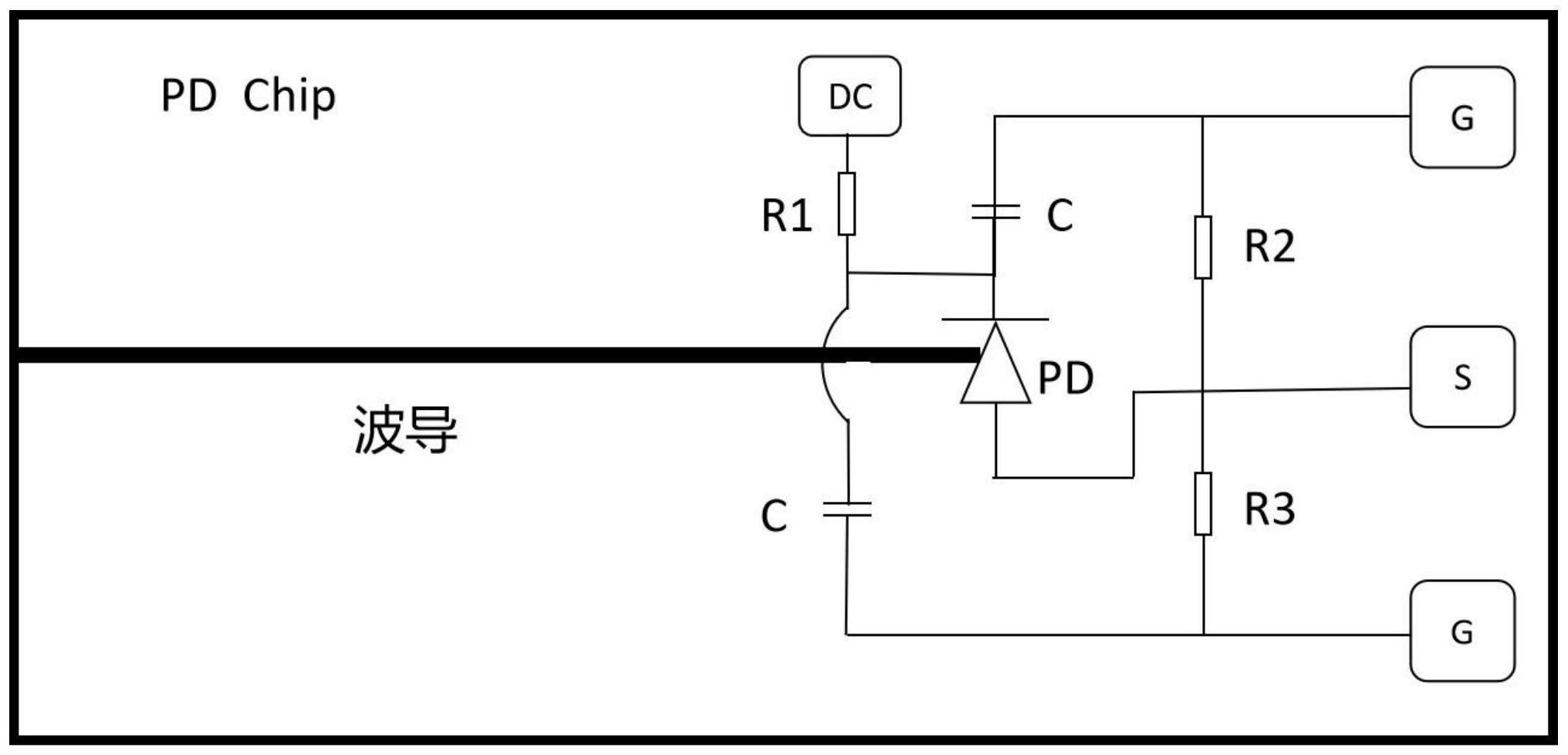

2、一种片上集成偏置电路光电探测器的制备方法,包括光电半导体二极管n极两侧分别串联20pf电容,为光电探测器串联2个隔直流信号的电容,所述光电探测器cpw共面电极上并联2个100ω薄膜电阻,正压的直流信号沿dc bisa端经过匹配电阻r1进入到光电探测器n极,p极通过cpw的s端后经电阻r2和r3和共面电极cpw的g端接地;

3、还包括在半绝缘衬底上设置外延层的光电探测器,所述外延层包括波导层、n接触层、漂移层、崖层、吸收层、阻挡层、p接触层,同时采用光刻工艺获取探测器台面,并在获取台面上采用深紫外光刻工艺或电子束曝光工艺确定金属层所对应的图像,制备电极以及电阻,电容。

4、优选的,所述直流信号起始端dc bisa电极与薄膜电阻和片上集成电容的下电极相连,所述电容的下电极连接到光电探测器n接触层上,所述光电探测器p电极引出cpw共面电极的s信号线,所述s信号线通过100ω电阻与cpw的g信号线连接。

5、优选的,所述光电探测器衬底为高电阻率的inp半绝缘衬底,电阻率大于1e7ωcm,通过mbe或者mocvd生长外延层,依次生长波导层、n接触层、漂移层、吸收层、p电极层。

6、优选的,所述吸收层厚度为200nm,掺杂浓度呈梯度掺杂。

7、优选的,所述光电探测器通过干法icp刻蚀工艺以及光刻工艺获取p型台面,n型台面,其p台面深度800nm,n台面深度400nm。

8、优选的,所述n台面上采用光刻工艺和抬离工艺,制备n电极,所述的n电极也作为偏置电路中薄膜电容的下极。

9、优选的,所述n台面电极和光电探测器有源区下方沉积tan作为薄膜电阻,所述的薄膜电阻的方阻为100ω。

10、优选的,所述光电探测器台面使用sio2钝化,钝化厚度200~800nm,并开孔预留cpw和dc偏置打线电极的区域,制备cpw和dc偏置的打线电极。

11、与现有技术相比,本发明具有如下有益效果:

12、本发明通过将电阻和电容等偏置电路中的电子元器件做到芯片上,不仅电子器件的参数可以做小,而且尺寸也做的更小,且免去了封装中的贴片和打线这些外围封装工序,剔除了封装寄生参数对芯片本征参数的影响,光电探测器中n电极做的较大,用于作为电容的下极板,采用sio2作为中间绝缘层,cpw作为电容上电极,制备成与光电探测器串联的电容,电阻则沉积在电容的下极板上,并将sio2绝缘层开孔,将cpw电极覆盖在薄膜电阻上,制备偏置电路中的电阻。

技术特征:

1.一种片上集成偏置电路光电探测器的制备方法,其特征在于:包括光电半导体二极管n极两侧分别串联20pf电容,为光电探测器串联2个隔直流信号的电容,所述光电探测器cpw共面电极上并联2个100ω薄膜电阻,正压的直流信号沿dc bisa端经过匹配电阻r1进入到光电探测器n极,p极通过cpw的s端后经电阻r2和r3和共面电极cpw的g端接地;

2.如权利要求1所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述直流信号起始端dc bisa电极与薄膜电阻和片上集成电容的下电极相连,所述电容的下电极连接到光电探测器n接触层上,所述光电探测器p电极引出cpw共面电极的s信号线,所述s信号线通过100ω电阻与cpw的g信号线连接。

3.如权利要求1所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述光电探测器衬底为高电阻率的inp半绝缘衬底,电阻率大于1e7ωcm,通过mbe或者mocvd生长外延层,依次生长波导层、n接触层、漂移层、吸收层、p电极层。

4.如权利要求3所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述吸收层厚度为200nm,掺杂浓度呈梯度掺杂。

5.如权利要求1所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述光电探测器通过干法icp刻蚀工艺以及光刻工艺获取p型台面,n型台面,其p台面深度800nm,n台面深度400nm。

6.如权利要求5所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述n台面上采用光刻工艺和抬离工艺,制备n电极,所述的n电极也作为偏置电路中薄膜电容的下极。

7.如权利要求6所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述n台面电极和光电探测器有源区下方沉积tan作为薄膜电阻,所述的薄膜电阻的方阻为100ω。

8.如权利要求1所述一种片上集成偏置电路光电探测器的制备方法,其特征在于:所述光电探测器台面使用sio2钝化,钝化厚度200~800nm,并开孔预留cpw和dc偏置打线电极的区域,制备cpw和dc偏置的打线电极。

技术总结

本发明涉及光电探测技术领域,提供了一种片上集成偏置电路光电探测器的制备方法,目的在于使用片上集成偏置电路,提供一种降低封装寄生参数的高性能光电探测器;本发明通过在光电半导体二极管N极两侧处分别串联20pF电容,并在光电探测器CPW共面电极上并联2个100Ω薄膜电阻;通过金属有机气相沉积或分子束外延在半绝缘衬底上依次生长外延层,同时采用I CP工艺获得P型台面,并按上述方法获得N型台面以及波导台阶,采用电子束蒸发或者磁控溅射沉底N台面金属和沉底P台面金属,分别作为片上集成偏置电路中电容的下极板和上极板,采用光刻工艺制作方阻为100Ω的薄膜电阻,用二氧化硅作为钝化层,同时作为电容的绝缘层,采用抬离工艺完成金属制作。

技术研发人员:付孟博,王文亭,刘志忠,王梦宾,张薇,祝宁华

受保护的技术使用者:雄安创新研究院

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!