叠层平面布局功率模块结构和功率器件

本发明涉及功率半导体,具体涉及一种叠层平面布局功率模块结构和功率器件。

背景技术:

1、sic功率器件具有更高的开关频率、更低的功率损耗、更高的耐受结温、能有效的提升电力电子装备的变换频率和功率密度,在新能源发电系统、电动汽车以及电力传动领域具有不可替代的作用。同时,sic mosfet在关断过程中没有拖尾电流,可有效降低开关损耗并提高开关速度。为了适应sic功率器件的优异性能,急需低感、低热阻和高可靠性的先进封装技术。双面散热封装具有平面化的封装结构、多通道的散热路径和更平衡的应力分布,是sic功率模块的发展趋势。

2、由于制造工艺和成本的限制,单个sic mosfet芯片的通流能力只有几十安培。而传统的平面型封装模块互联方式比较单一,仅存在顶层和底层两层电流传输路径,限制了电流通流能力和并联芯片数量。传统平面型封装模块多芯片并联布局通常使用上下两层dbc基板、多个芯片、连接端子来进行布局。然而,这种布局方式会带来占用过多的平铺面积、设计尺寸较大、结构较松散和设计自由度低等问题。

3、因此需要一种方案来解决实现sic mosfet的多芯片并联封装占用过多的平铺面积、设计尺寸较大、结构较松散和设计自由度低的问题。

技术实现思路

1、基于上述问题,本发明提供一种功率模块结构和功率器件,以解决现有技术的功率模块布局占用过多的平铺面积、尺寸较大、结构较松散、设计自由度低的问题。

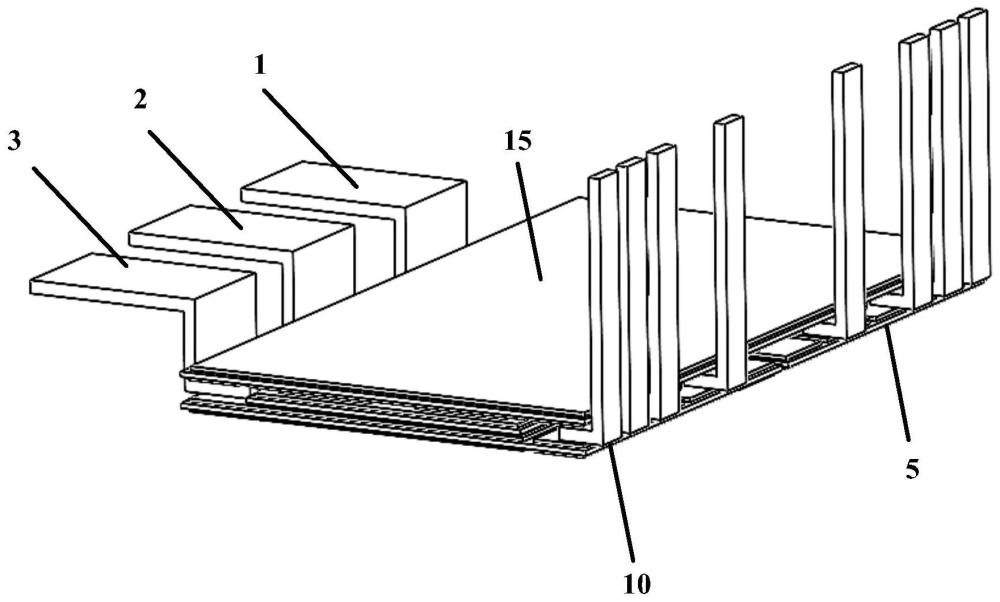

2、本发明提供一种叠层平面布局功率模块结构,包括:同层并列排布的下管单元和上管单元,以及连接所述下管单元和所述上管单元的桥接铜片;所述下管单元设置直流负极端子和交流端子,所述上管单元设置直流正极端子;所述下管单元设置直流负极端子和交流端子;所述下管单元包括下管底层dbc基板,所述下管底层dbc基板上阵列设置有并联的下管sic功率芯片;所述上管单元包括上管底层dbc基板,所述上管底层dbc基板上阵列设置有并联的上管sic功率芯片;还包括:上层dbc基板,所述上层dbc基板同时完全覆盖所述上管单元和所述下管单元,且所述上层dbc基板电连接所述下管单元和所述直流负极端子;所述下管单元还设置有下管连接dbc基板,所述下管sic功率芯片通过所述下管连接dbc基板连接所述上层dbc基板和位于所述上管单元的所述直流负极端子;所述上管单元还设置有上管连接dbc基板,所述桥接铜片连接所述下管底层dbc基板和所述上管连接dbc基板;所述上管sic功率芯片通过所述上管连接dbc基板连接所述下管单元的所述交流端子和各所述下管sic功率芯片。

3、可选的,所述上层dbc基板底面与所述下管单元和所述直流负极端子直接电连接且与所述上管单元无直接电连接。

4、可选的,所述下管单元还设置有下管芯片连接钼片和下管连接铜片;所述下管芯片连接钼片与所述下管sic功率芯片一一对应设置;所述下管连接铜片设置于所述下管连接钼片和所述上层dbc基板之间,且直接电连接所述上层dbc基板,使各所述下管sic功率芯片通过所述下管芯片连接钼片和所述下管连接铜片电连接所述上层dbc基板。

5、可选的,所述下管连接dbc基板叠设于所述下管底层dbc基板上;所述下管连接dbc基板具有镂空区,所述下管sic功率芯片阵列设置于所述镂空区中。

6、可选的,所述上管连接dbc基板叠设于所述上管底层dbc基板上;所述上管连接dbc基板具有镂空区,所述上管sic功率芯片阵列设置于所述镂空区中。

7、可选的,所述交流端子设置于所述下管底层dbc基板,所述直流正极端子和所述直流负极端子设置于所述上管底层dbc基板,且所述直流正极端子、所述直流负极端子和所述交流端子位于所述叠层平面布局功率模块的同一侧。

8、可选的,所述上管单元还设置有上管芯片连接钼片和上管连接铜片;所述上管芯片连接钼片与所述上管sic功率芯片一一对应设置;所述上管连接铜片设置于所述上管连接钼片和所述上层dbc基板之间,分别连接各所述上管芯片连接钼片和所述上管连接dbc基板,使各所述上管sic功率芯片通过所述上管连接dbc基板和所述桥接铜片电连接所述下管底层dbc基板。

9、可选的,所述下管单元还包括:下管ntc测试端子对,设置于所述下管底层dbc基板,且位于所述交流端子相对一侧;下管源极端子和下管门极端子,设置于所述下管连接dbc基板,且位于所述交流端子相对一侧。

10、可选的,所述上管单元还包括:上管ntc测试端子对,设置于所述上管底层dbc基板,且位于所述直流正极端子和所述直流负极端子相对一侧;上管源极端子和上管门极端子,设置于所述上管连接dbc基板,且位于所述直流正极端子和所述直流负极端子相对一侧。

11、本发明还提供一种功率器件,包括如本发明所提供的叠层平面布局功率模块结构。

12、本发明的有益效果如下:

13、本发明提供的叠层平面布局功率模块结构,相对于传统平面型封装的功率模块结构仅可具有顶层和底层两层电流传输路径,相同数量的sic功率芯片若使用传统平面型封装的功率模块结构则在相同大电流条件下需要占据更大的面积。本发明通过加入上管连接dbc基板和下管连接dbc基板,使得可以实现三层电流传输路径,使得功率模块布局更加紧凑。通过多个dbc基板配合叠层dbc基板连接的形式,实现原本平铺设置dbc基板才能实现的大面积多个功率芯片设置区中多个功率芯片的并联连接,可以使得功率模块结构更加紧凑,有利于缩小功率模块体积。从而解决现有技术的功率模块布局占用过多的平铺面积、尺寸较大、结构较松散的问题。

技术特征:

1.一种叠层平面布局功率模块结构,其特征在于,包括:

2.根据权利要求1所述的叠层平面布局功率模块结构,其特征在于,

3.根据权利要求2所述的叠层平面布局功率模块结构,其特征在于,

4.根据权利要求2所述的叠层平面布局功率模块结构,其特征在于,

5.根据权利要求4所述的叠层平面布局功率模块结构,其特征在于,

6.根据权利要求5所述的叠层平面布局功率模块结构,其特征在于,

7.根据权利要求6所述的叠层平面布局功率模块结构,其特征在于,

8.根据权利要求6所述的叠层平面布局功率模块结构,其特征在于,

9.根据权利要求6所述的叠层平面布局功率模块结构,其特征在于,

10.一种功率器件,其特征在于,

技术总结

本发明涉及功率半导体技术领域。具体涉及一种叠层平面布局功率模块结构和功率器件。叠层平面布局功率模块结构包括:同层并列排布的下管单元和上管单元;下管单元设置交流端子,上管单元设置直流正极端子和直流负极端子;下管单元包括下管底层DBC基板,下管底层DBC基板上阵列设置有并联的下管SiC功率芯片,下管中间层DBC基板及下管上层DBC基板;上管单元包括上管底层DBC基板,上管底层DBC基板上阵列设置有并联的上管SiC功率芯片,上管中间层DBC基板及上管上层DBC基板;下管单元下管SiC功率芯片通过上管连接DBC基板连接上管单元的各端子和各上管SiC功率芯片。上管SiC功率芯片通过下管连接DBC基板连接下管单元的各端子和各下管SiC功率芯片。

技术研发人员:康玉慧,宁圃奇,回晓双,李东润,范涛,王凯

受保护的技术使用者:中国科学院电工研究所

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!