一种自适应超结沟槽式MOSFET器件及其制备方法与流程

本发明属于电子元器件、半导体、集成电路领域,特别涉及一种自适应超结沟槽式mosfet器件及其制备方法。

背景技术:

1、超结mosfet(super junction metal-oxide-semiconductor field-effecttransisto)是一种广泛用于电机驱动、开关电源和各类功率变换的半导体器件,尤其适用于高功率、高效率的应用。如图1所示的传统超结mosfet结构的工作原理是通过控制半导体器件的栅极-源极电位差来控制该器件的开关以及通过内置的npnpn结型耐压层实现高电压的耐受。一般情况下,高电压需要低浓度的漂移区,而传统漂移区杂质浓度过低则会导致比导通电阻增大从而增加mosfet的导通损耗,因此,超结结构是一种解决上述难题的有效技术方案,是功率半导体器件里程碑式的发明。但是传统的超结结构虽然其纵向器件的布置耐压效果很好,但受制于超结n区的掺杂浓度不够高,比导通电阻仍存在下降空间。而且传统的超结mosfet里面的超结结构是固定的,无法随着外部电压的变化而变化,当器件处于开态的时候,如图2所示,电流从n-杂质区流向源极n+注入区,此时n-杂质区与栅氧层之间存在较大的导通电阻,且受限于超结区中n-杂质区的掺杂浓度,存在一个极限值,无法自适应于外部电压的变化。

技术实现思路

1、为了解决上述技术问题,本发明提供一种自适应超结沟槽式mosfet器件及其制备方法,可以随着外部电压的变化而自适应改变超结结构,不仅可以保证器件关态时的耐压性能,而且可以使器件开态时获得更低的比导通电阻,实现更低的导通损耗。

2、本发明中主要采用的技术方案为:

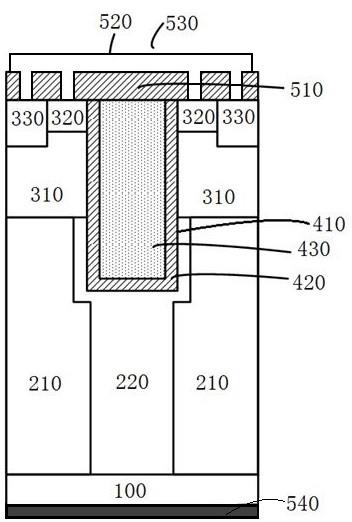

3、一种自适应超结沟槽式mosfet器件,包括:

4、第一导电类型衬底;

5、超结区,形成于所述第一导电类型衬底的上表面,包括一个第二导电类型杂质区和两个对称设置在第二导电类型杂质区两侧的第一导电类型杂质区,且所述第二导电类型杂质区的上端向两侧的第一导电类型杂质区扩展,形成t型结构的第二导电类型杂质区;

6、表面结构层,形成于所述超结区的上表面;

7、沟槽栅结构,设置在所述表面结构层内,并延伸至超结区中的第二导电类型杂质区上端内;

8、以及电极结构,形成于所述表面结构层的上表面。

9、优选地,所述沟槽栅结构包括沟槽、栅氧化层和栅极多晶硅,所述沟槽形成于表面结构层,且向下延伸至第二导电类型杂质区上端内,所述栅氧化层生长在沟槽表面,所述栅极多晶硅填充在沟槽内,且所述栅氧化层包覆所述栅极多晶硅的两侧面和底面。

10、优选地,所述表面结构层包括:

11、第二导电类型阱区,形成于所述超结区的上表面,且在第二导电类型阱区内部刻蚀有一个延伸至第二导电类型杂质区内部的沟槽;

12、两个源极第一导电类型注入区,制作在所述第二导电类型阱区的表面,且两个所述源极第一导电类型注入区对称设置在沟槽两侧,且与沟槽内的栅氧化层相切;

13、两个背栅第二导电类型注入区,制作在所述第二导电类型阱区的表面,且两个所述背栅第二导电类型注入区对称设置在沟槽两侧,且分别与位于同侧的源极第一导电类型注入区相切;

14、所述背栅第二导电类型注入区的结深大于源极第一导电类型注入区。

15、优选地,位于所述第二导电类型杂质区内的沟槽两侧分别与两个第一导电类型杂质区在水平方向上保持相同的距离。

16、优选地,所述第二导电类型杂质区的上端向两侧的第一导电类型杂质区扩展的宽度 l为0.1-1μm。

17、优选地,所述第二导电类型杂质区上端的扩展区底部到沟槽底部的h为0.1-1μm。

18、优选地,所述电极结构包括:

19、场氧化层,所述场氧化层制作在所述表面结构层的上表面;

20、源极金属,所述源极金属制作在所述场氧化层的上表面,且通过接触孔穿过场氧化层分别与每个背栅第二导电类型注入区和源极第一导电类型注入区接触;

21、栅极金属,所述栅极多晶硅通过侧面打孔的方式制作连接至结构外部的栅极金属;

22、漏极金属,所述第一导电类型衬底通过侧面打孔的方式制作连接至结构外部的漏极金属。

23、优选地,所述第一导电类型为n型,所述第二导电类型为p型;或,所述第一导电类型为p型,所述第二导电类型为n型。

24、一种自适应超结沟槽式mosfet器件的制备方法,具体包括以下步骤:

25、s1:准备第一导电类型衬底;

26、s2:采用光刻工艺在第一导电类型衬底上分别注入两个第一导电类型注入区和一个第二导电类型注入区,并进行第一次外延工艺形成两个第一导电类型杂质区ⅰ和一个第二导电类型杂质区ⅰ,其中,两个第一导电类型杂质区ⅰ位于第二导电类型杂质区ⅰ两侧;

27、s3:重复步骤s2n-1次,在前一步骤相同的位置上方继续采用光刻工艺注入相对应的两个第一导电类型注入区和一个第二导电类型注入区,并进行第n-1次外延工艺形成第一导电类型杂质区n-1和一个第二导电类型杂质区n-1;

28、s4:改变掩模版增加顶层第二导电类型杂质区的曝光面积,采用光刻工艺注入两个顶层第一导电类型注入区和一个顶层第二导电类型注入区,并进行外延形成两个顶层第一导电类型杂质区和一个顶层第二导电类型杂质区,完成超结区的制作;

29、s5:在超结区的上表面注入第二导电类型杂质,并进行外延形成第二导电类型阱区;

30、s6:在第二导电类型阱区内部刻蚀一个延伸至顶层第二导电类型注入区内的沟槽,并在沟槽内表面形成栅氧化层,并在沟槽内填充栅极多晶硅,完成沟槽栅结构的制作;

31、s7:后续的工艺制程和常规制程相同,完成表面层结构和电极结构的制作。

32、有益效果:本发明提供一种自适应超结沟槽式mosfet器件及其制备方法,与现有技术相比,具有如下优点:

33、(1)本发明通过调整超结第一导电类型杂质区的二维布置,让器件耐压层在关态时仍然保持超结的作用,利用超结结构pnpn两两耗尽增强该区域的耗尽程度,保证器件关态时的耐压性能。

34、(2)本发明通过调整沟道栅的位置以及第二导电类型杂质区的上端结构,使得沟道栅在第二导电类型杂质区中可以形成场效应,在器件开启时,可以在第二导电类型杂质区形成一层反型电子沟道,让该电子沟道与第二导电类型杂质区在开态时连在一起,从而获得更低的比导通电阻,实现更低的导通损耗。

技术特征:

1.一种自适应超结沟槽式mosfet器件,其特征在于,包括:

2.根据权利要求1所述的自适应超结沟槽式mosfet器件,其特征在于,所述沟槽栅结构包括沟槽(410)、栅氧化层(420)和栅极多晶硅(430),所述沟槽(410)形成于表面结构层,且向下延伸至第二导电类型杂质区上端内,所述栅氧化层(420)生长在沟槽(410)表面,所述栅极多晶硅(430)填充在沟槽(410)内,且所述栅氧化层(420)包覆所述栅极多晶硅(430)的两侧面和底面。

3.根据权利要求2所述的自适应超结沟槽式mosfet器件,其特征在于,所述表面结构层包括:

4.根据权利要求2所述的自适应超结沟槽式mosfet器件,其特征在于,位于所述第二导电类型杂质区内的沟槽(410)两侧分别与两个第一导电类型杂质区在水平方向上保持相同的距离。

5.根据权利要求1所述的自适应超结沟槽式mosfet器件,其特征在于,所述第二导电类型杂质区的上端向两侧的第一导电类型杂质区扩展的宽度l为0.1-1μm。

6.根据权利要求1所述的自适应超结沟槽式mosfet器件,其特征在于,所述第二导电类型杂质区上端的扩展区底部到沟槽(410)底部的高度h为0.1-1μm。

7.根据权利要求1-6任一所述的自适应超结沟槽式mosfet器件,其特征在于,所述电极结构包括:

8.根据权利要求1所述的自适应超结沟槽式mosfet器件的制备方法,其特征在于,所述第一导电类型为n型,所述第二导电类型为p型;或,所述第一导电类型为p型,所述第二导电类型为n型。

9.一种自适应超结沟槽式mosfet器件的制备方法,其特征在于,具体包括以下步骤:

技术总结

本发明公开了一种自适应超结沟槽式MOSFET器件及其制备方法,包括:第一导电类型衬底;超结区,形成于第一导电类型衬底的上表面,包括一个第二导电类型杂质区和两个对称设置在第二导电类型杂质区两侧的第一导电类型杂质区,且第二导电类型杂质区的上端向两侧的第一导电类型杂质区扩展,形成T型结构的第二导电类型杂质区;表面结构层,形成于超结区的上表面;沟槽栅结构,设置在表面结构层内,并延伸至超结区中的第二导电类型杂质区上端内;以及电极结构,形成于表面结构层的上表面。本发明可以随着外部电压的变化而自适应改变超结结构,不仅可以保证器件关态时的耐压性能,而且可以使器件开态时获得更低的比导通电阻,实现更低的导通损耗。

技术研发人员:孙明光,李振道,朱伟东

受保护的技术使用者:江苏应能微电子股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!