一种半导体衬底及其制备方法、半导体器件与流程

本申请涉及半导体器件的,具体涉及一种半导体衬底及其制备方法、半导体器件。

背景技术:

1、目前,绝缘体上硅(silicon-on-insulator,简称soi)因为具有良好的射频性能(如更好的隔离性,更低的衬底耦合,更低的寄生电容,没有闩锁效应等),成为射频开关以及低噪声放大器的首选。但是在数字逻辑器件的应用中,相较于体硅没有明显的优势。

2、相关技术中,半导体衬底多是单独的绝缘体上硅衬底或者体硅衬底,分别适用于射频器件和数字逻辑器件。体硅和绝缘体上硅不能混合,难以同时适配射频器件和数字逻辑器件。

技术实现思路

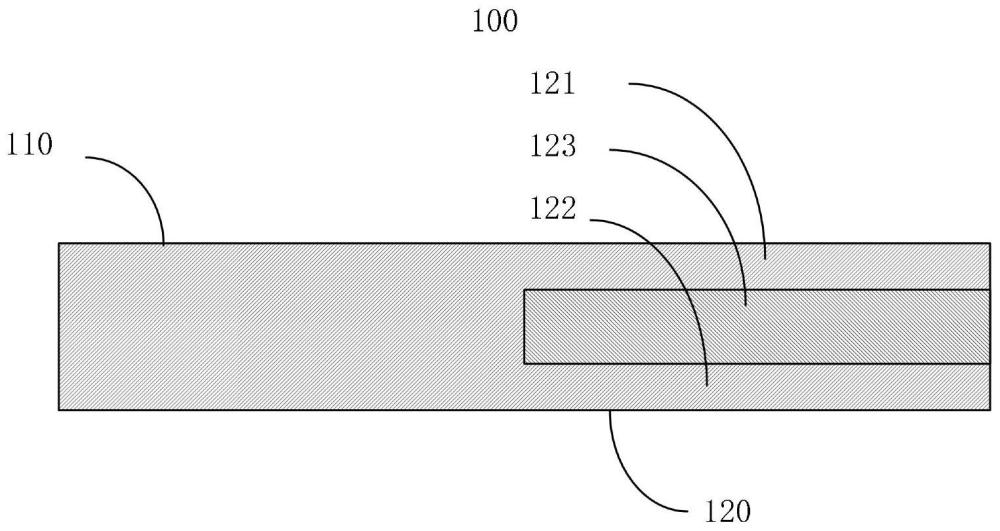

1、为了解决上述问题而提出了本申请,根据本申请的一方面,提供了一种半导体衬底,所述衬底包括体硅区域和位于所述体硅区域外侧的绝缘体上硅区域,所述绝缘体上硅区域包括底层硅和顶层硅,以及设置在底层硅和顶层硅之间的绝缘层;其中,所述体硅区域用于制备数字逻辑器件,所述绝缘体上硅区域用于制备射频器件。

2、示例性地,所述衬底包括第一衬底和第二衬底;其中,在所述第一衬底的部分区域内形成有第一绝缘层,所述第一绝缘层自所述第一衬底的第一表面向内延伸;在所述第二衬底的部分区域内形成有第二绝缘层,所述第二绝缘层自所述第二衬底的第一表面向内延伸,所述第一衬底的第一表面和所述第二衬底的第一表面相键合,且所述第一绝缘层和所述第二绝缘层相结合构成所述绝缘层;或者,仅在所述第一衬底的部分区域内形成有所述绝缘层,所述绝缘层自所述第一衬底的第一表面向内延伸,所述第一衬底的第一表面和所述第二衬底的第一表面相键合;或者,仅在所述第二衬底的部分区域内形成有所述绝缘层,所述绝缘层自所述第二衬底的第一表面向内延伸,所述第一衬底的第一表面和所述第二衬底的第一表面相键合。

3、根据本申请的另一方面,提供了一种半导体衬底的制备方法,所述方法包括:提供第一衬底和第二衬底;自所述第一衬底和/或所述第二衬底的第一表面的部分区域向内形成绝缘层;对所述第一衬底的第一表面与所述第二衬底的第一表面进行键合,得到所述半导体衬底,其中,当所述第一衬底和所述第二衬底均形成有所述绝缘层时,在所述键合时,所述第一衬底上的绝缘层和所述第二衬底上的绝缘层相键合。

4、示例性地,所述自所述第一衬底和/或所述第二衬底的第一表面的部分区域向内形成绝缘层,包括:在所述第一衬底的第一表面和所述第二衬底的第一表面均形成隔离层;在所述第一衬底和所述第二衬底上覆盖图形化掩膜层,以所述图形化掩膜层为掩膜刻蚀所述隔离层以暴露部分所述第一表面;自被暴露的所述第一衬底的第一表面向内延伸形成第一绝缘层;自被暴露的所述第二衬底的第一表面向内延伸形成第二绝缘层;或者,所述自所述第一衬底或所述第二衬底的第一表面的部分区域向内形成绝缘层,包括:在所述第一衬底的第一表面形成隔离层;在所述第一衬底上覆盖图形化掩膜层,以所述图形化掩膜层为掩膜刻蚀所述隔离层以暴露部分所述第一表面;自被暴露的所述第一衬底的第一表面向内延伸形成所述绝缘层;或者,所述自所述第一衬底和/或所述第二衬底的第一表面的部分区域向内形成绝缘层,包括:在所述第二衬底的第一表面形成隔离层;在所述第二衬底上覆盖图形化掩膜层,以所述图形化掩膜层为掩膜刻蚀所述隔离层以暴露部分所述第一表面;自被暴露的所述第二衬底的第一表面向内延伸形成所述绝缘层。

5、示例性地,所述对所述第一衬底的第一表面以及所述第二衬底的第一表面进行键合之前,所述方法还包括:去除第一衬底和/或所述第二衬底的第一表面上剩余的所述隔离层;对所述第一衬底和所述第二衬底进行平坦化处理。

6、示例性地,所述隔离层包括第一隔离层和第二隔离层,所述在所述第一衬底的第一表面和所述第二衬底的第一表面均形成隔离层,包括:在所述第一衬底的第一表面和所述第二衬底的第一表面均形成所述第二隔离层;在所述第二隔离层上均形成所述第一隔离层;其中,所述第一隔离层为氮化硅,所述第二隔离层为氧化硅。

7、示例性地,所述隔离层包括第一隔离层和第二隔离层,所述在所述第一衬底的第一表面形成所述隔离层,包括:所述第一衬底的第一表面形成所述第二隔离层;在所述第二隔离层上形成所述第一隔离层;所述在所述第二衬底的第一表面形成所述隔离层,包括:在所述第二衬底的第二表面形成所述第二隔离层;在所述第二隔离层上形成所述第一隔离层;其中,所述第一隔离层为氮化硅,所述第二隔离层为氧化硅。

8、根据本申请的又一方面,提供了另一种半导体衬底的制备方法,所述方法包括:提供体硅衬底,所述体硅衬底包括第一区域和第二区域;在所述第二区域的指定位置形成绝缘层,以使所述第二区域成为绝缘体上硅区域,得到所述半导体衬底。

9、示例性地,所述绝缘层为氧化硅,所述在所述第二区域的指定位置形成绝缘层,包括:向所述第二区域的指定位置注入氧原子并使氧原子和硅反应而形成所述绝缘层。

10、根据本申请的再一方面,提供了一种半导体器件,所述半导体器件包括上述的半导体衬底,所述半导体器件包括数字逻辑器件和射频器件,所述数字逻辑器件位于所述半导体衬底的体硅区域,所述射频器件位于所述半导体衬底的绝缘体上硅区域。

11、本申请中的半导体衬底,包括体硅区域和绝缘体上硅区域,将体硅和绝缘体上硅进行混合得到了混合衬底,射频器件可以制备于绝缘体上硅区域,从而凭借绝缘体上硅良好的射频性能提高射频器件的性能;数字逻辑器件可以制备于体硅区域,减少对衬底面积的占用。本申请中的半导体衬底同时具备绝缘体上硅衬底和体硅衬底的优势,显著提高半导体器件的性能。

技术特征:

1.一种半导体衬底,其特征在于,所述衬底包括体硅区域和位于所述体硅区域外侧的绝缘体上硅区域,所述绝缘体上硅区域包括底层硅和顶层硅,以及设置在底层硅和顶层硅之间的绝缘层;

2.根据权利要求1所述的半导体衬底,其特征在于,所述衬底包括第一衬底和第二衬底;

3.一种半导体衬底的制备方法,其特征在于,所述方法包括:

4.根据权利要求3所述的方法,其特征在于,所述自所述第一衬底和/或所述第二衬底的第一表面的部分区域向内形成绝缘层,包括:

5.根据权利要求4所述的方法,其特征在于,所述对所述第一衬底的第一表面以及所述第二衬底的第一表面进行键合之前,所述方法还包括:

6.根据权利要求4所述的方法,其特征在于,所述隔离层包括第一隔离层和第二隔离层,所述在所述第一衬底的第一表面和所述第二衬底的第一表面均形成隔离层,包括:

7.根据权利要求4所述的方法,其特征在于,所述隔离层包括第一隔离层和第二隔离层,所述在所述第一衬底的第一表面形成所述隔离层,包括:

8.一种半导体衬底的制备方法,其特征在于,所述方法包括:

9.根据权利要求8所述的方法,其特征在于,所述绝缘层为氧化硅,所述在所述第二区域的指定位置形成绝缘层,包括:

10.一种半导体器件,其特征在于,所述半导体器件包括权利要求1-2中的任一项所述的半导体衬底,所述半导体器件包括数字逻辑器件和射频器件,所述数字逻辑器件位于所述半导体衬底的体硅区域,所述射频器件位于所述半导体衬底的绝缘体上硅区域。

技术总结

本申请涉及一种半导体衬底及其制备方法、半导体器件,所述衬底包括体硅区域和位于所述体硅区域外侧的绝缘体上硅区域,所述绝缘体上硅区域包括底层硅和顶层硅,以及设置在底层硅和顶层硅之间的绝缘层;其中,所述体硅区域用于制备数字逻辑器件,所述绝缘体上硅区域用于制备射频器件。本申请的半导体衬底将体硅和绝缘体上硅混合在一起,可以分别用于制备数字逻辑器件以及射频器件,提高半导体器件的性能。

技术研发人员:张俊龙,方潇功,王琛

受保护的技术使用者:绍兴中芯集成电路制造股份有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!