复合栅介质层及其制造方法、包括复合栅介质层的耗尽型MISHEMT器件与流程

本申请涉及半导体领域,尤其涉及一种复合栅介质层及其制造方法、包括复合栅介质层的耗尽型mishemt器件。

背景技术:

1、本部分的描述仅提供与本申请公开相关的背景信息,而不构成现有技术。

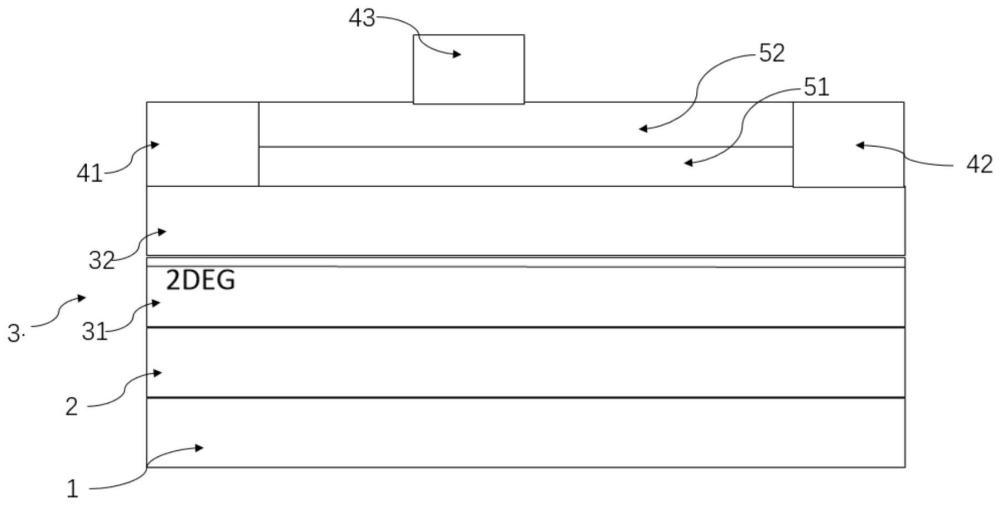

2、图1示出了现有技术中的耗尽型mishemt器件的结构示意图。该耗尽型mishemt器件包括:衬底1、形成在衬底1上的缓冲2、形成在缓冲2上的异质结3(用于产生2deg沟道)、形成在异质结3上的单层栅介质层50、形成在栅介质层上的栅极42、形成在所述异质结3上的源极41以及形成在所述异质结3上的漏极43。其中,金属栅极42-栅介质-质结三层材料形成mis结构(金属-绝缘体-半导体)。

3、对于mishemt而言,栅介质层的质量对于器件可靠性尤为重要。mishemt中的栅介质通常采用cvd的生长方式制备,例如pecvd,lpcvd,icpcvd,mocvd,ald等设备。栅介质层通常为一层介质实现,介质材料包括sin,sio2,al2o3,aln,hfo2等中的一种。栅介质材料往往只由单一设备生长单一介质材料实现。换言之,均为单层栅介质层50。例如,目前量产采用最多的技术为mocvd原位sin介质,以及lpcvd sin介质材料。这往往会产生一个问题,单一介质材料中的应力等问题会在介质材料中产生针孔(pinhole)等缺陷,这些缺陷可能是局部存在的,也可能是贯穿整个栅介质的,如上图所示。当这些缺陷正好位于栅极42金属正下方时,会严重影响栅极42的可靠性和寿命。

4、目前产业界采用的消除这类介质缺陷的方法是通过chip test(cp),final test(ft),burn in等测试筛选方法筛掉这类缺陷。这类筛选方法存在以下问题,一是过度的栅极42应力筛选会退化器件的性能和寿命,二者缺陷是存在不同程度的,测试只能筛选掉部分缺陷,不能根治。因此从问题的源头来看,需要从介质的本身去寻求优化方案,改善这类失效问题。

5、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、基于前述的现有技术缺陷,本申请中复合栅介质层及其制造方法、包括复合栅介质层的耗尽型mishemt器件,其能从源头上规避栅介质层存在贯穿针孔的问题。

2、为了实现上述目的,本申请提供了如下的技术方案:一种复合栅介质层,包括:通过mocvd与异质结一并形成的in-situ sin层,以及通过lpcvd在in-situ sin层上表面形成的lpcvd sin层,从而使所述in-situ sin层的上表面和所述lpcvd sin层的下表面之间形成用于错开针孔的界面。

3、本申请公开了一种复合栅介质层,包括:至少两个层叠设置的硅氮层,其中,至少两个相邻的所述硅氮层中si:n比不同,从而在这两个相邻的硅氮层之间形成用于错开针孔的界面。

4、优选地,多个所述硅氮层中si:n根据实际应力设定。

5、本申请公开了一种复合栅介质层,包括至少两个栅介层、设置在相邻的两个所述栅介层之间的插入层,所述栅介层和所述插入层由不相同的材料制成。

6、优选地,所述插入层的材料为al2o3,aln,sion中的一种或多种。

7、本申请公开了一种复合栅介质层的制造方法,包括以下步骤:

8、通过mocvd与异质结一并形成的in-situ sin层;

9、通过lpcvd在in-situ sin层上表面形成的lpcvd sin层。

10、本申请公开了一种复合栅介质层的制造方法,包括以下步骤:

11、通过调控参数的方式实现,从而在异质结上形成多个硅氮层,其中,任两个相邻的所述硅氮层中si:n比不同。

12、优选地,步骤“通过调控参数的方式实现,从而在异质结上形成多个硅氮层,其中,任两个相邻的所述硅氮层中si:n比不同”通过lpcvd或pecvd设备,以控制生长反应气体流量来进行作业。

13、本申请公开了一种复合栅介质层的制造方法,包括以下步骤:

14、在异质结上形成栅介层;

15、在栅介层上形成插入层;

16、在插入层上形成另一个栅介层。

17、优选地,步骤“在栅介层上形成插入层,在插入层上形成另一个栅介层”多次循环直至达到要求。

18、本申请公开了一种耗尽型mishemt器件,包括:

19、用于形成在衬底上的缓冲层;

20、形成在缓冲层上的异质结;

21、形成在所述异质结上的漏极和源极;

22、如上述的复合栅介质层,所述复合栅介质层形成在所述异质结上;

23、形成在所述复合栅介质层上的栅极。

24、本申请公开了一种复合栅介质层,包括至少两个层叠设置的单元层,其中,至少两个相邻的所述单元层的材料或形成方式不同,从而使相邻的两个所述单元层的针孔不贯穿这两个所述单元层。

25、优选地,相邻的两个所述单元层的针孔不存在交叉部分。

26、优选地,相邻的两个所述单元层的针孔相互错开。。

27、借由以上的技术方案,本申请实施例中的栅介质层中的应力明显改善,缺陷减少,器件可靠性和寿命提升。栅介质层中贯穿pinhole明显减少,器件早期失效率下降,良率提升。本方案容易实现,易于量产。

28、参照后文的说明和附图,详细公开了本申请的特定实施例,指明了本申请的原理可以被采用的方式。应该理解,本申请的实施例在范围上并不因而受到限制。在所附权利要求的精神和条款的范围内,本申请的实施例包括许多改变、修改和等同。

29、针对一种实施例描述和/或示出的特征可以以相同或类似的方式在一个或更多个其它实施例中使用,与其它实施例中的特征相组合,或替代其它实施例中的特征。

30、应该强调,术语“包括/包括”在本文使用时指特征、整件、步骤或组件的存在,但并不排除一个或更多个其它特征、整件、步骤或组件的存在或附加。

技术特征:

1.一种复合栅介质层,其特征在于,包括:通过mocvd与异质结一并形成的in-situ sin层,以及通过lpcvd在in-situ sin层上表面形成的lpcvd sin层,从而使所述in-situ sin层的上表面和所述lpcvd sin层的下表面之间形成用于错开针孔的界面。

2.一种复合栅介质层,其特征在于,包括:至少两个层叠设置的硅氮层,其中,至少两个相邻的所述硅氮层中si:n比不同,从而在这两个相邻的硅氮层之间形成用于错开针孔的界面。

3.根据权利要求2所述的复合栅介质层,其特征在于,多个所述硅氮层中si:n根据实际应力设定。

4.一种复合栅介质层,其特征在于,包括至少两个栅介层、设置在相邻的两个所述栅介层之间的插入层,所述栅介层和所述插入层由不相同的材料制成。

5.根据权利要求4所的复合栅介质层,其特征在于,所述插入层的材料为al2o3,aln,sion中的一种或多种。

6.一种复合栅介质层的制造方法,其特征在于,包括以下步骤:

7.一种复合栅介质层的制造方法,其特征在于,包括以下步骤:

8.根据权利要求7所述的复合栅介质层的制造方法,其特征在于,步骤“通过调控参数的方式实现,从而在异质结上形成多个硅氮层,其中,任两个相邻的所述硅氮层中si:n比不同”通过lpcvd或pecvd设备,以控制生长反应气体流量来进行作业。

9.一种复合栅介质层的制造方法,其特征在于,包括以下步骤:

10.根据权利要求9所述的复合栅介质层的制造方法,其特征在于,步骤“在栅介层上形成插入层,在插入层上形成另一个栅介层”多次循环直至达到要求。

11.一种耗尽型mishemt器件,其特征在于,包括:

12.一种复合栅介质层,其特征在于,包括至少两个层叠设置的单元层,其中,至少两个相邻的所述单元层的材料或形成方式不同,从而使相邻的两个所述单元层的针孔不贯穿这两个所述单元层。

13.根据权利要求12所述的复合栅介质层,其特征在于,相邻的两个所述单元层的针孔不存在交叉部分。

14.根据权利要求13所述的复合栅介质层,其特征在于,相邻的两个所述单元层的针孔相互错开。

技术总结

本申请提供了一种复合栅介质层,包括:通过MOCVD与异质结一并形成的In‑situ SiN层,以及通过LPCVD在In‑situ SiN层上表面形成的LPCVD SiN层,从而使所述In‑situ SiN层的上表面和所述LPCVD SiN层的下表面之间形成用于错开针孔的界面。本申请还公开了一种复合栅介质层,包括:至少两个层叠设置的硅氮层,其中,至少两个相邻的所述硅氮层中Si:N比不同,从而在这两个相邻的硅氮层之间形成用于错开针孔的界面。本申请还公开了一种复合栅介质层,包括至少两个栅介层、设置在相邻的两个所述栅介层之间的插入层,所述栅介层和所述插入层由不相同的材料制成。本申请实施例中的栅介质层中的应力明显改善,缺陷减少,器件可靠性和寿命提升。栅介质层中贯穿pinhole明显减少,器件早期失效率下降,良率提升。本方案容易实现,易于量产。

技术研发人员:姜涛

受保护的技术使用者:深圳镓楠半导体科技有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!