一种抑制空穴大注入的DSRD结构及制备方法

本发明涉及半导体工艺,具体涉及一种抑制空穴大注入的dsrd结构及制备方法。

背景技术:

1、漂移阶跃恢复二极管(drift step recovery diodes,简称dsrd)是一种半导体开关二极管,由俄罗斯约飞物理技术研究所提出,一般应用于超宽带(ultra wide band,简称uwb)系统中,在多种脉冲信号源中被作为关键器件使用,可以达到纳秒甚至皮秒级的开关时间,且具有高峰值功率、高脉冲重复频率以及高时间稳定度等特点。

2、由于硅材料的理论极限,硅基dsrd已无法满足多数几千伏甚至是几十千伏的高压脉冲系统的要求。在同等电压等级要求的脉冲系统中,碳化硅基dsrd的串联数量远小于硅基dsrd,极大的节省了系统的体积。同时漂移区厚度的降低和饱和漂移速度的提升能够降低器件的关断时间,使得碳化硅基dsrd可以工作在高频、高速的应用场景中。

3、但是,由于目前碳化硅材料的载流子寿命和迁移率较低和杂质不完全离化效应的影响,使得常规碳化硅基dsrd在脉冲放电的反向泵浦阶段局部偏离电中性,影响载流子抽取速度,从而导致电压脉冲前沿时间长、电压脉冲峰值低、器件功耗大,难以充分发挥碳化硅材料的优势,限制了器件的性能。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种抑制空穴大注入的dsrd结构及制备方法。本发明要解决的技术问题通过以下技术方案实现:

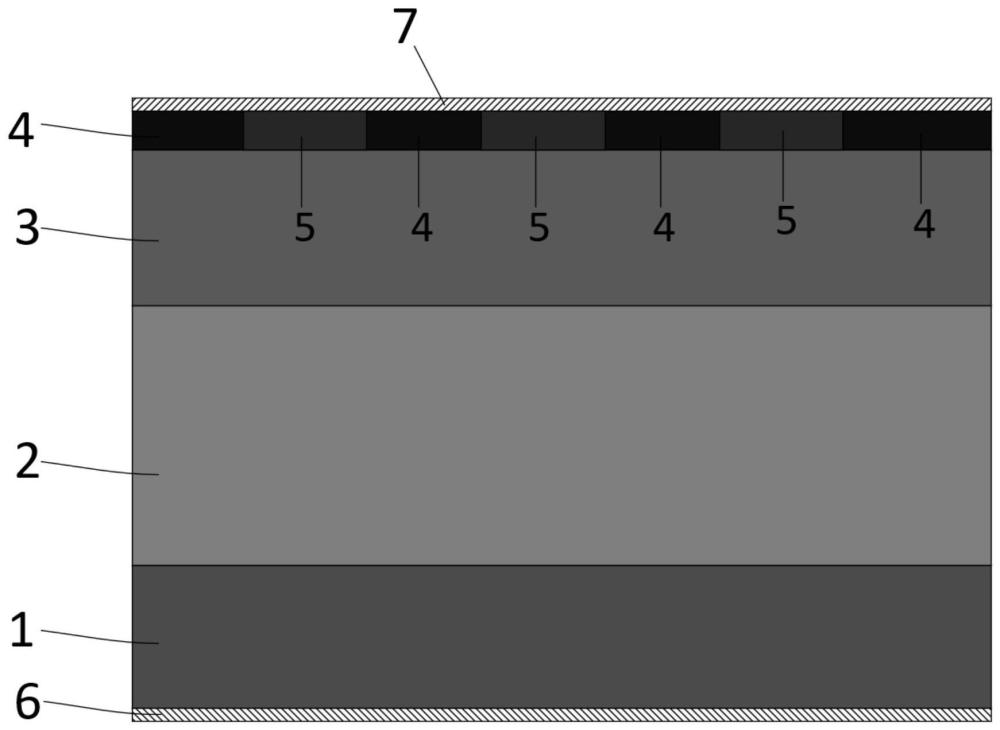

2、一种抑制空穴大注入的dsrd结构,所述dsrd结构从下至上包括依次层叠设置的阴极、n+衬底层、n-漂移区、p-漂移区、结合区和阳极,其中,

3、所述结合区包括多个p+区和多个n+区,所述多个p+区间隔设置在所述p-漂移区上,两个相邻的所述p+区之间设置一所述n+区,且相邻的所述p+区和所述n+区相互接触,所述p+区和所述n+区的厚度相等;

4、所述阴极与所述n+衬底层之间为欧姆接触,所述阳极与所述p+区和所述n+区之间为欧姆接触。

5、在本发明的一个实施例中,所述p+区和所述n+区的掺杂浓度相等。

6、在本发明的一个实施例中,所述p+区和所述n+区的掺杂浓度大于所述p-漂移区和所述n-漂移区的掺杂浓度。

7、在本发明的一个实施例中,所述p-漂移区的掺杂浓度大于所述n-漂移区的掺杂浓度。

8、在本发明的一个实施例中,所述p+区和所述n+区的掺杂浓度大于所述n+衬底层的掺杂浓度,所述n+衬底层的掺杂浓度大于所述p-漂移区的掺杂浓度。

9、在本发明的一个实施例中,所述n+衬底层的掺杂浓度为5×1018cm-3,所述n-漂移区的掺杂浓度为1×1014cm-3-1×1017cm-3,所述p-漂移区的掺杂浓度为1×1014cm-3-1×1018cm-3,所述p+区和所述n+区的掺杂浓度为1×1019cm-3-1×1020cm-3。

10、在本发明的一个实施例中,所述n+衬底层、所述n-漂移区和所述n+区的掺杂离子相同。

11、在本发明的一个实施例中,所述p-漂移区和所述p+区的掺杂离子相同。

12、在本发明的一个实施例中,所述n-漂移区的厚度大于所述p-漂移区的厚度,所述p-漂移区的厚度大于所述p+区和所述n+区的厚度。

13、本发明一个实施例还提供一种抑制空穴大注入的dsrd结构的制备方法,所述dsrd结构包括:

14、选取n+衬底层;

15、在所述n+衬底层上制备n-漂移区;

16、在所述n-漂移区上制备p-漂移区;

17、在所述p-漂移区上制备结合区,所述结合区包括多个p+区和多个n+区,所述多个p+区间隔设置在所述p-漂移区上,两个相邻的所述p+区之间设置一所述n+区,且相邻的所述p+区和所述n+区相互接触,所述p+区和所述n+区的厚度相等;

18、在所述p+区和所述n+区上制备阳极,所述阳极与所述p+区和所述n+区之间为欧姆接触;

19、在所述n+衬底层的下表面制备阴极,所述阴极与所述n+衬底层为欧姆接触。

20、与现有技术相比,本发明的有益效果在于:

21、本实施例在p-漂移区上设置了一由多个p+区和多个n+区组成的结合区,且多个p+区和多个n+区间隔交替设置,由此使得结合区形成了由p+区和n+区交叉的掺杂区域,由此,在正向电流注入阶段,由于n+区设置在两个p+区之间,减少了p+区的有效面积,因此可以有效地减少注入到dsrd的n-漂移区中的空穴,降低n-漂移区大注入的程度,降低器件的平台区电压,从而降低了该阶段的器件功耗。在器件快速关断阶段,由于此结构设计降低了n-漂移区大注入的程度,继而有效缓解了关断过程中n-漂移区呈现的“软恢复”现象,可以有效的提高多数载流子的漂移速度,加快空间电荷区的扩展速度,降低器件的上升时间从而提高器件的开关速度。

22、在反向泵浦的少子抽取阶段,由于本发明的dsrd结构的p+n+/p-结附近的p-漂移区内部的掺杂浓度低,由此完全离化程度高,有效地降低了p-漂移区局部偏离电中性的程度,降低了器件的平台区电压,从而降低了该阶段的器件功耗。

23、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:

1.一种抑制空穴大注入的dsrd结构,其特征在于,所述dsrd结构从下至上包括依次层叠设置的阴极、n+衬底层、n-漂移区、p-漂移区、结合区和阳极,其中,

2.根据权利要求1所述的抑制空穴大注入的dsrd结构,其特征在于,所述p+区和所述n+区的掺杂浓度相等。

3.根据权利要求2所述的抑制空穴大注入的dsrd结构,其特征在于,所述p+区和所述n+区的掺杂浓度大于所述p-漂移区和所述n-漂移区的掺杂浓度。

4.根据权利要求3所述的抑制空穴大注入的dsrd结构,其特征在于,所述p-漂移区的掺杂浓度大于所述n-漂移区的掺杂浓度。

5.根据权利要求4所述的抑制空穴大注入的dsrd结构,其特征在于,所述p+区和所述n+区的掺杂浓度大于所述n+衬底层的掺杂浓度,所述n+衬底层的掺杂浓度大于所述p-漂移区的掺杂浓度。

6.根据权利要求5所述的抑制空穴大注入的dsrd结构,其特征在于,所述n+衬底层的掺杂浓度为5×1018cm-3,所述n-漂移区的掺杂浓度为1×1014cm-3-1×1017cm-3,所述p-漂移区的掺杂浓度为1×1014cm-3-1×1018cm-3,所述p+区和所述n+区的掺杂浓度为1×1019cm-3-1×1020cm-3。

7.根据权利要求6所述的抑制空穴大注入的dsrd结构,其特征在于,所述n+衬底层、所述n-漂移区和所述n+区的掺杂离子相同。

8.根据权利要求6所述的抑制空穴大注入的dsrd结构,其特征在于,所述p-漂移区和所述p+区的掺杂离子相同。

9.根据权利要求1所述的抑制n区大注入的dsrd结构,其特征在于,所述n-漂移区的厚度大于所述p-漂移区的厚度,所述p-漂移区的厚度大于所述p+区和所述n+区的厚度。

10.一种抑制空穴大注入的dsrd结构的制备方法,其特征在于,所述dsrd结构包括:

技术总结

本发明涉及一种抑制空穴大注入的DSRD结构及制备方法,所述DSRD结构从下至上包括依次层叠设置的阴极、N+衬底层、N‑漂移区、P‑漂移区、结合区和阳极,其中,所述结合区包括多个P+区和多个N+区,所述多个P+区间隔设置在所述P‑漂移区上,两个相邻的所述P+区之间设置一所述N+区,且相邻的所述P+区和所述N+区相互接触,所述P+区和所述N+区的厚度相等;所述阴极与所述N+衬底层之间为欧姆接触,所述阳极与所述P+区和所述N+区之间为欧姆接触。本发明可以有效地减少注入到DSRD的N‑漂移区中的空穴,降低N‑漂移区大注入的程度,降低器件的平台区电压,从而降低了该阶段的器件功耗。

技术研发人员:周瑜,王晨光,宋庆文,汤晓燕,袁昊,杜丰羽,张玉明

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!