半导体器件及半导体器件的制作方法与流程

本发明实施例涉及半导体,尤其涉及一种半导体器件及半导体器件的制作方法。

背景技术:

1、随着半导体技术的发展,人们对半导体器件的要求越来越高。现有的氮化镓功率器件,包括连续性场板,但现有的半导体器件的场板一般由一次沉积形成,无法满足场板多样性的耐压等需求的应用场景,影响半导体器件的耐压效果。

技术实现思路

1、本发明实施例提供一种半导体器件及半导体器件的制作方法,以解决半导体器件的场板无法满足多样性的耐压等需求的应用场景,降低半导体器件的耐压效果的问题。

2、为实现上述技术问题,本发明采用以下技术方案:

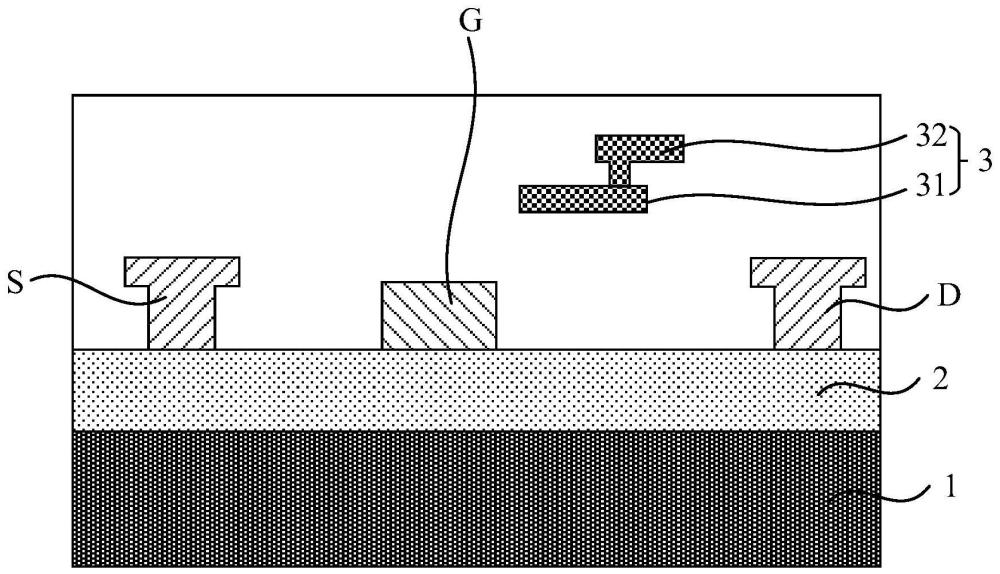

3、本发明实施例提供了一种半导体器件,包括:

4、衬底;

5、设置于衬底一侧的半导体掺杂层;

6、设置于半导体掺杂层远离衬底一侧的栅极、源极和漏极;

7、设置于栅极远离衬底一侧的场板;

8、场板包括至少两层子场板;各子场板通过过孔连接;至少一层子场板在衬底的正投影与相邻子场板在衬底的正投影至少部分交叠。

9、可选的,所述场板在所述衬底的正投影与所述栅极在所述衬底的正投影错开;

10、所述场板在所述衬底的正投影与所述源极在所述衬底的正投影错开;

11、所述场板在所述衬底的正投影与所述漏极在所述衬底的正投影错开。

12、可选的,至少两层子场板的材料不同;或者,

13、至少两层子场板的厚度不同。

14、可选的,半导体器件,还包括:

15、第一绝缘层,第一绝缘层设置于栅极和场板之间;

16、场板包括:第一子场板和第二子场板;

17、第一子场板设置于第一绝缘层远离衬底的一侧;

18、第二子场板设置于第一子场板远离衬底的一侧;

19、第二子场板与第一子场板连接,第二子场板在衬底的正投影至少部分覆盖第一子场板在衬底的正投影。

20、可选的,场板,还包括:

21、第三子场板,第三子场板设置于第二子场板远离衬底的一侧;

22、第三子场板在衬底的正投影至少部分覆盖第二子场板在衬底的正投影;

23、沿平行于所述衬底方向,且沿由所述栅极向所述漏极的方向,所述第一子场板的长度与所述第二子场板长度以及所述第三子场板的长度相同。

24、可选的,半导体器件,还包括:

25、导电结构,导电结构设置于第一子场板远离衬底的一侧;所述导电结构与所述第一子场板连接,所述第一子场板用于通过所述导电结构接零电位;

26、导电结构在衬底的正投影与第二子场板在衬底的正投影不交叠。

27、根据本发明的另一方面,本实施例提供一种半导体器件的制作方法,包括:

28、提供衬底;

29、在所述衬底一侧形成半导体掺杂层;

30、在所述半导体掺杂层远离所述衬底一侧形成栅极、源极和漏极;

31、在所述栅极远离所述衬底一侧形成场板;其中,所述场板包括至少两层子场板;各所述子场板通过过孔连接;至少一层所述子场板在所述衬底的正投影与相邻所述子场板在所述衬底的正投影至少部分交叠。

32、可选的,在所述栅极远离所述衬底一侧形成场板之前,还包括:

33、在所述栅极远离所述衬底的一侧形成第一绝缘层;

34、所述在所述栅极远离所述衬底一侧形成场板,包括:

35、在第一绝缘层远离所述衬底的一侧形成第一子场板;

36、在所述第一子场板远离所述衬底的一侧形成第二子场板;

37、在所述第二子场板远离所述衬底的一侧形成第三子场板。

38、可选的,所述在所述第一绝缘层远离所述衬底的一侧形成所述第一子场板,包括:

39、在所述第一绝缘层远离所述衬底的一侧沉积第一材料层,对所述第一材料层光刻和刻蚀形成第一子场板。

40、可选的,所述在所述第一子场板远离所述衬底的一侧形成第二子场板,包括:

41、在所述第一子场板远离所述衬底的一侧,形成第二绝缘层;

42、光刻和刻蚀所述第二绝缘层,形成第一通孔;

43、在所述第二绝缘层远离所述衬底的一侧沉积第二材料层,所述第二材料层填充所述第一通孔;

44、对所述第二材料层光刻和刻蚀形成第二子场板。

45、可选的,所述在所述第二子场板远离所述衬底的一侧形成第三子场板,包括:

46、在所述第二子场板远离所述衬底的一侧,形成第三绝缘层;

47、光刻和刻蚀所述第三绝缘层,形成第二通孔;

48、在所述第三绝缘层远离所述衬底的一侧沉积第三材料层,所述第三材料层填充所述第二通孔;

49、对所述第三材料层光刻和刻蚀形成第三子场板。

50、本发明实施例提供的半导体器件通过在栅极远离衬底一侧设置场板,场板包括至少两层子场板,各子场板通过过孔连接,至少一层子场板在衬底的正投影与相邻子场板在衬底的正投影至少部分交叠,提高了场板的设置灵活性。这样设置,实现了灵活设置各子场板的长度、厚度、材料等,较好的提高各子场板的耐压能力,进而改善半导体器件的耐压能力。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述半导体器件,其特征在于,

3.根据权利要求1所述半导体器件,其特征在于,

4.根据权利要求1所述半导体器件,其特征在于,所述半导体器件,还包括:

5.根据权利要求4所述半导体器件,其特征在于,所述场板,还包括:

6.根据权利要求5所述半导体器件,其特征在于,所述半导体器件,还包括:

7.一种半导体器件的制作方法,其特征在于,包括:

8.根据权利要求7所述的方法,其特征在于,在所述栅极远离所述衬底一侧形成场板之前,还包括:

9.根据权利要求8所述的方法,其特征在于,

10.根据权利要求9所述的方法,其特征在于,所述在所述第二子场板远离所述衬底的一侧形成第三子场板,包括:

技术总结

本发明实施例公开一种半导体器件及半导体器件的制作方法。该半导体器件包括衬底;设置于衬底一侧的半导体掺杂层;设置于半导体掺杂层远离衬底一侧的栅极、源极和漏极;设置于栅极远离衬底一侧的场板;场板包括至少两层子场板;各子场板通过过孔连接;至少一层子场板在衬底的正投影与相邻子场板在衬底的正投影至少部分交叠。本实施例提供的技术方案解决解决半导体器件的场板无法满足多样性的耐压等需求的应用场景,降低半导体器件的耐压效果的问题。

技术研发人员:杨航,饶剑,马俊辉

受保护的技术使用者:英诺赛科(珠海)科技有限公司

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!