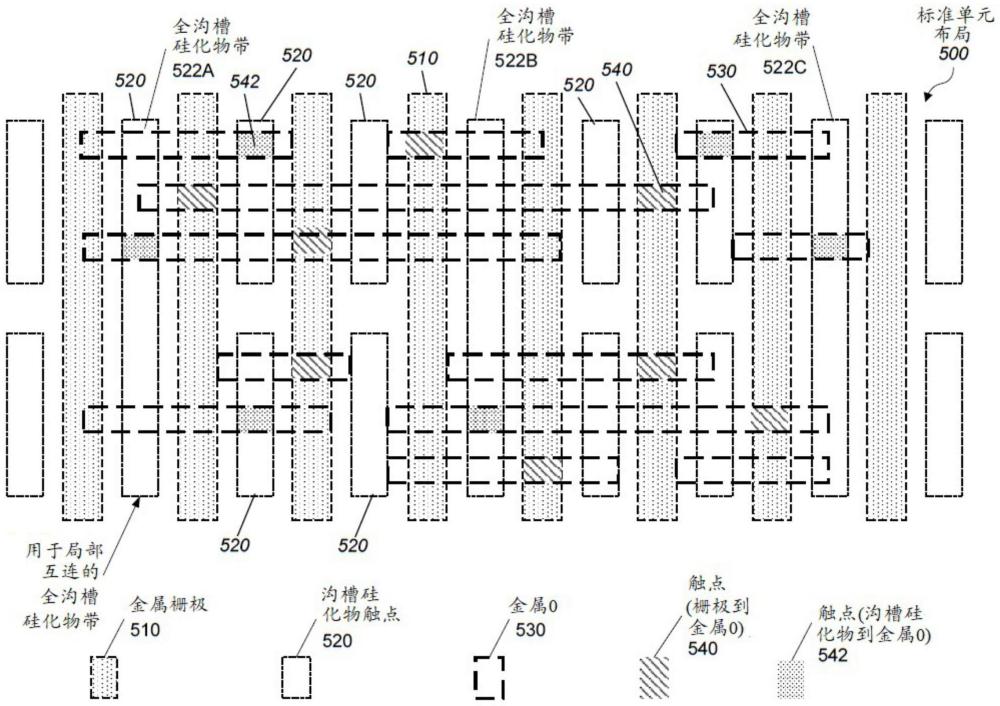

用于5纳米及以上的标准单元布局架构和绘图样式的制作方法

背景技术:

1、相关技术说明

2、随着半导体制造工艺的进步和管芯上几何尺寸的减小,半导体芯片在消耗更少空间的同时提供更多的功能和性能。尽管已经取得了许多进展,但是现代处理技术和集成电路设计中的设计问题仍然存在,这限制了潜在的益处。例如,电容耦合、电迁移、泄漏电流和处理产率是影响装置的布置和跨半导体芯片的整个管芯的信号的布线的一些问题。因此,这些问题可能延迟设计的完成并影响上市时间。

3、为了缩短半导体芯片的设计周期,尽可能用自动化取代手动全定制设计。设计人员用高级描述语言(诸如verilog、vhdl等)提供功能单元或复杂栅极的描述。合成工具接收逻辑描述并提供逻辑网表。布置和布线(pnr)工具使用逻辑网表来提供物理布局。布置和布线工具使用单元布局库来提供物理布局。

4、单元布局库包括多个标准单元布局,用于提供由半导体芯片使用的各种功能。在一些情况下,标准单元布局是手动创建的。因此,每个新的标准单元布局或每个正在修改的原始标准单元布局都是手动创建的。在其他情况下,调整由布置和布线工具使用的规则以使单元创建自动化。然而,自动化过程有时并不满足针对性能、功耗、信号完整性、过程良率、本地和外部信号布线(包括内部交叉耦合连接)、匹配其他单元的高度和宽度单元尺寸、引脚接入、电源轨设计等的每一个规则。因此,设计人员手动地创建这些单元以实现对于多个特性的更好结果或者重写用于布置和布线工具的规则。

5、鉴于上述情况,需要用于布置标准单元的有效方法和系统。

技术实现思路

技术特征:

1.一种单元布局,其包括:

2.根据权利要求1所述的单元布局,其中,所述两个单独晶体管中的每一个包括各自的源极区和沟道区。

3.根据权利要求2所述的单元布局,其中所述一个或多个全沟槽硅化物带中的每一个为单向带。

4.根据权利要求1所述的单元布局,其中,所述单元布局中的每个信号路线是单向路线。

5.根据权利要求1所述的单元布局,其中,所述布局还包括第一晶体管的漏极触点与第二晶体管的栅极触点之间的交叉耦合路线。

6.根据权利要求1所述的单元布局,其中,所述布局还包括从所述单元布局的顶部延伸到底部的一个或多个输出引脚。

7.根据权利要求6所述的单元布局,其中用于所述一个或多个输出引脚中的每一个的最高金属层是金属1。

8.根据权利要求6所述的单元布局,其中所述一个或多个输出引脚中的至少一个以单向方式从所述标准单元的所述顶部布线到所述底部。

9.一种方法,包括:

10.根据权利要求9所述的方法,其中,所述两个单独晶体管中的每一个包括各自的源极区和沟道区。

11.根据权利要求10所述的方法,其中所述一个或多个全沟槽硅化物带中的每一个为单向带。

12.根据权利要求9所述的方法,其中,每个信号路线是单向路线。

13.根据权利要求9所述的方法,还包括第一晶体管的漏极触点与第二晶体管的栅极触点之间的交叉耦合路线。

14.根据权利要求9所述的方法,其中用于所述一个或多个输出引脚中的每一个的最高金属层是金属1。

15.根据权利要求14所述的方法,其中所述一个或多个输出引脚中的至少一个以单向方式布线。

16.一种存储多个指令的非暂时性计算机可读存储介质,所述多个指令在被执行时生成集成电路布局,所述集成电路布局包括:

17.根据权利要求16所述的非暂时性计算机可读存储介质,其中,所述两个单独晶体管中的每一个包括各自的源极区和沟道区。。

18.根据权利要求17所述的非暂时性计算机可读存储介质,其中所述一个或多个全沟槽硅化物带中的每一个为单向带。

19.根据权利要求16所述的非暂时性计算机可读存储介质,其中,每个信号路线是单向路线。

20.根据权利要求16所述的非暂时性计算机可读存储介质,其中,所述布局还包括第一晶体管的漏极触点与第二晶体管的栅极触点之间的交叉耦合路线。

技术总结

描述了一种用于有效地创建标准单元的布局的系统和方法。用于集成电路的标准单元使用全沟槽硅化物带作为pmos晶体管和nmos晶体管的漏极区域。金属0中的多条单向路线跨标准单元布置,其中每个路线都连接到沟槽硅化物触点。电源连接和接地连接利用引脚而不是标准单元中的端到端轨。另外,中间节点以单向路线在标准单元中布线。

技术研发人员:理查德·T·舒尔茨

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!