一种晶圆级非TSV3D堆叠封装结构及方法与流程

本发明属于半导体封装,特别涉及一种晶圆级非tsv 3d堆叠封装结构及方法。

背景技术:

1、传统无硅通孔 3d( 非tsv 3d、non-tsv 3d)堆叠封装技术是一种将多个芯片或组件在垂直方向上堆叠起来的技术。这种技术通过在芯片之间使用电气连接和机械连接来实现信号和电源的传输,同时保持紧凑的封装尺寸。

2、传统非tsv 3d堆叠封装用金属线键合或者倒装技术或者两者结合的方式通过基板进行堆叠,大颗栅格阵列封装(lga)/球栅阵列封装(bga)基板作业都是单颗进行,作业效率没有晶圆级作业高。同时,由于将多个芯片需要借助基板在垂直方向上堆叠,封装后的芯片具有较大的厚度,基本都在80um以上,这可能会导致信号传输距离较长,从而增加信号传输延迟和功耗。

3、同时,传统非tsv 3d堆叠封装技术的制造成本较高。由于需要将多个芯片或组件在垂直方向上堆叠在一起,因此需要使用高精度的组装工艺和昂贵的封装材料。此外,需要使引脚或端子等连接器来实现电气连接,这也会增加封装的成本。

技术实现思路

1、为了解决上述问题,本发明提供了一种晶圆级非tsv 3d堆叠封装结构及方法,成本低廉、作业效率高,可以使得芯片厚度减薄,电性能损耗更小。

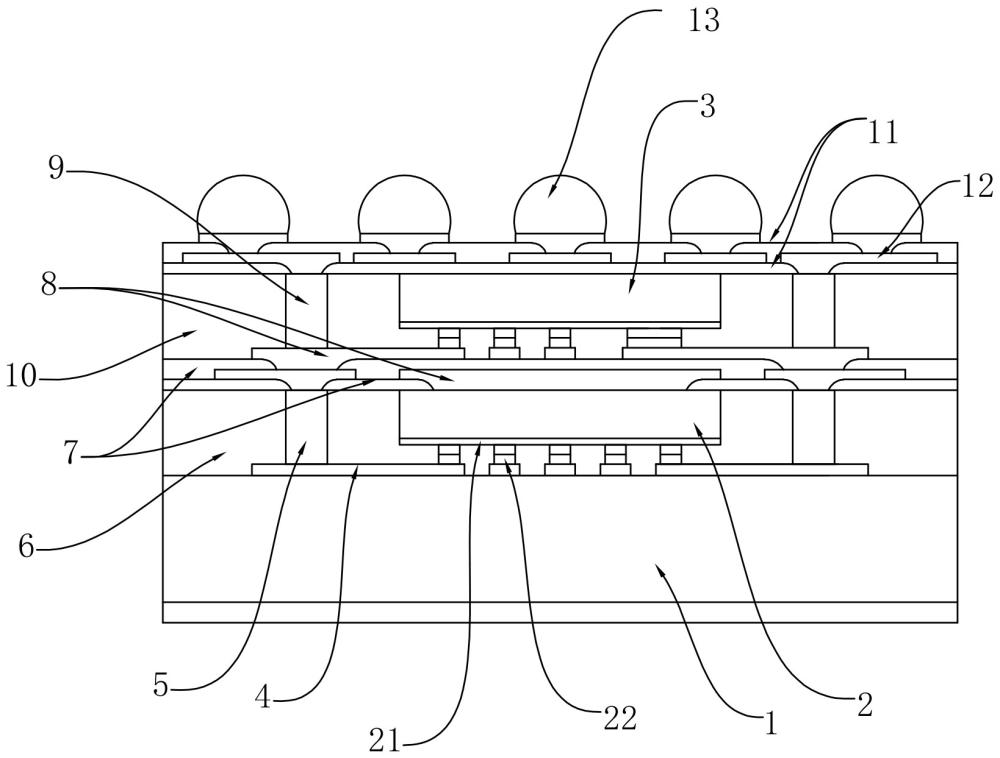

2、为此,本发明的技术方案是:一种晶圆级非tsv 3d堆叠封装结构,包括基板和若干堆叠设置的芯片单元层,所有芯片单元层互相堆叠在一起,置于基板上;所述芯片单元层包括至少一个倒置的芯片单元,芯片单元外侧设有塑封层,相邻芯片单元层之间设有重布线层,各芯片单元正面通过重布线层与侧面铜柱导通。

3、在上述方案的基础上并作为上述方案的优选方案:所述芯片单元包括芯片本体,芯片本体正面设有焊料凸点,焊料凸点通过重布线层与侧面铜柱电性连接。

4、在上述方案的基础上并作为上述方案的优选方案:第一芯片单元层下方设有第一重布线层,第一重布线层上设有第一铜柱;所述第一芯片单元层包括至少一个第一芯片单元,第一芯片单元倒置在第一重布线层上,第一塑封层覆盖第一芯片单元和第一铜柱,且第一塑封层、第一芯片单元背面、第一铜柱同步减薄。

5、在上述方案的基础上并作为上述方案的优选方案:第二芯片单元层下方设有第二重布线层,第二重布线层上设有第二铜柱;所述第二芯片单元层包括至少一个第二芯片单元,第二芯片单元倒置在第二重布线层上;所述第二芯片单元外侧设有第二塑封层,第二塑封层覆盖第二芯片单元和第二铜柱,第二塑封层、第二芯片单元背面、第二铜柱同步减薄。

6、在上述方案的基础上并作为上述方案的优选方案:最顶层的芯片单元层上设有第三重布线层,第三重布线层上设有焊点,焊点由植球或电镀形成。

7、在上述方案的基础上并作为上述方案的优选方案:相邻芯片单元层之间设有多层第二重布线层,相邻第二重布线层之间设有介电层。

8、本发明的另一个技术方案是:一种晶圆级非tsv 3d堆叠封装方法,包括以下步骤:

9、1)制备多个芯片单元:在硅晶片正面完成晶圆级封装,制作出焊料凸点,并对硅晶片进行磨片、划片,得到芯片单元;

10、2)制备基板:在基板正面制作第一重布线层和第一铜柱;

11、3)将至少一个第一芯片单元倒置在基板的第一重布线层上,第一芯片单元正面通过第一重布线层与第一铜柱导通;

12、4)对第一芯片单元进行塑封,塑封层覆盖第一芯片单元和第一铜柱;

13、5)对基板正面进行磨片,裸露出第一铜柱和第一芯片单元的背面,形成第一芯片单元层;

14、6)在第一芯片单元层上方设置第二重布线层和第二铜柱;

15、7)将至少一个第二芯片单元倒置在第二重布线层上,第二芯片单元正面通过第二重布线层与第二铜柱导通;

16、8)重复步骤4)~6),形成第二芯片单元层;

17、9)重复步骤7)~8),堆叠设置多个芯片单元层;

18、10)当堆叠数量达到需求后,在最顶层芯片单元层上方进行植球或电镀工艺;

19、11)对步骤10)得到的封装体进行后处理,得到合格品芯片。

20、在上述方案的基础上并作为上述方案的优选方案:所述步骤1)中,所有芯片单元可为相同类型芯片或不同类型芯片。

21、在上述方案的基础上并作为上述方案的优选方案:所述步骤5)磨片后,芯片单元减薄至20~25μm。

22、在上述方案的基础上并作为上述方案的优选方案:所述步骤6)中,若芯片单元背面设有电极,电极可通过第二重布线层导出。

23、与现有技术相比,本发明的有益效果是:

24、采用非tsv的晶圆级封装,相邻芯片单元之间不需要设置基板,使用pi/rdl的工艺实现互联,使得芯片厚度更薄电性能损耗更小;

25、芯片单元倒装后,采用晶圆级底部填充工艺,实现芯片单元背面的完整填充;芯片单元背面可直接覆盖布线绝缘材料,无需环氧树脂类型的emc材料;同时,可以实现芯片单元背面导通,如果芯片单元背面是电极,可以通过rdl导通出去;

26、采用标准工艺芯片厚度进行倒装,芯片背面与侧边的铜柱同步减薄,实现超薄结构,使得芯片最小厚度可至20um水平,从而可控制整体封装厚度,或者说在同等厚度下,可堆叠更多的芯片单元,实现更多功能;

27、可基于产品要求堆叠多层芯片单元,同一层芯片单元层可平铺多个芯片单元,且芯片单元可选用相同芯片,也可以选择不同类型芯片,实现多样化功能设计,满足更多使用需求,通用性强。

技术特征:

1.一种晶圆级非tsv 3d堆叠封装结构,其特征在于:包括基板和若干堆叠设置的芯片单元层,所有芯片单元层互相堆叠在一起,置于基板上;所述芯片单元层包括至少一个倒置的芯片单元,芯片单元外侧设有塑封层,相邻芯片单元层之间设有重布线层,各芯片单元正面通过重布线层与侧面铜柱导通。

2.如权利要求1所述的一种晶圆级非tsv 3d堆叠封装结构,其特征在于:所述芯片单元包括芯片本体,芯片本体正面设有焊料凸点,焊料凸点通过重布线层与侧面铜柱电性连接。

3.如权利要求1所述的一种晶圆级非tsv 3d堆叠封装结构,其特征在于:第一芯片单元层下方设有第一重布线层,第一重布线层上设有第一铜柱;所述第一芯片单元层包括至少一个第一芯片单元,第一芯片单元倒置在第一重布线层上,第一塑封层覆盖第一芯片单元和第一铜柱,且第一塑封层、第一芯片单元背面、第一铜柱同步减薄。

4.如权利要求3所述的一种晶圆级非tsv 3d堆叠封装结构,其特征在于:第二芯片单元层下方设有第二重布线层,第二重布线层上设有第二铜柱;所述第二芯片单元层包括至少一个第二芯片单元,第二芯片单元倒置在第二重布线层上;所述第二芯片单元外侧设有第二塑封层,第二塑封层覆盖第二芯片单元和第二铜柱,第二塑封层、第二芯片单元背面、第二铜柱同步减薄。

5.如权利要求1所述的一种晶圆级非tsv 3d堆叠封装结构,其特征在于:最顶层的芯片单元层上设有第三重布线层,第三重布线层上设有焊点,焊点由植球或电镀形成。

6. 如权利要求1所述的一种晶圆级非tsv 3d堆叠封装结构,其特征在于:相邻芯片单元层之间设有多层第二重布线层,相邻第二重布线层之间设有介电层。

7.一种晶圆级非tsv 3d堆叠封装方法,其特征在于:包括以下步骤:

8.如权利要求7所述的一种晶圆级非tsv 3d堆叠封装方法,其特征在于:所述步骤1)中,所有芯片单元可为相同类型芯片或不同类型芯片。

9.如权利要求7所述的一种晶圆级非tsv 3d堆叠封装方法,其特征在于:所述步骤5)磨片后,芯片单元减薄至20~25μm。

10.如权利要求7所述的一种晶圆级非tsv 3d堆叠封装方法,其特征在于:所述步骤6)中,若芯片单元背面设有电极,电极可通过第二重布线层导出。

技术总结

本发明公开了一种晶圆级非TSV 3D堆叠封装结构及方法,包括基板和若干堆叠设置的芯片单元层,所有芯片单元层互相堆叠在一起,置于基板上;所述芯片单元层包括至少一个倒置的芯片单元,芯片单元外侧设有塑封层,相邻芯片单元层之间设有重布线层,各芯片单元正面通过重布线层与侧面铜柱导通。本发明采用非TSV的晶圆级封装,相邻芯片单元之间不需要设置基板,使用PI/RDL的工艺实现互联,使得芯片厚度更薄电性能损耗更小;芯片背面与侧边的铜柱同步减薄,实现超薄结构,使得芯片最小厚度可至20um水平,从而可控制整体封装厚度。

技术研发人员:张黎,张宇锋,龚嘉明

受保护的技术使用者:浙江禾芯集成电路有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!