半导体封装结构的制作方法

本公开涉及半导体封装,尤其涉及一种半导体封装结构。

背景技术:

1、中介层(interposer)可以与半导体器件、封装基板电连接,进而实现半导体器件与封装基板之间的信息交换。将半导体器件设于中介层上后,需要进行封装,即在半导体器件与中介层之间形成填充物,将半导体器件与中介层隔离,并且在半导体器件的表面以及中介层的表面上形成封装层。

2、在形成填充物时,相邻的半导体器件之间的间隙处的填充物容易出现尖角的沟槽,即填充物的对应于间隙的部位不完整,在进行包封时,封装层在填充物的沟槽区域填充困难,导致分层,影响封装可靠性,进而影响半导体封装结构的良率。

3、在所述背景技术部分公开的上述信息仅用于加强对本公开的背景的理解,因此它可以包括不构成对本领域普通技术人员已知的相关技术的信息。

技术实现思路

1、本公开实施例提供了一种半导体封装结构,能够提高封装的可靠性以及良率。

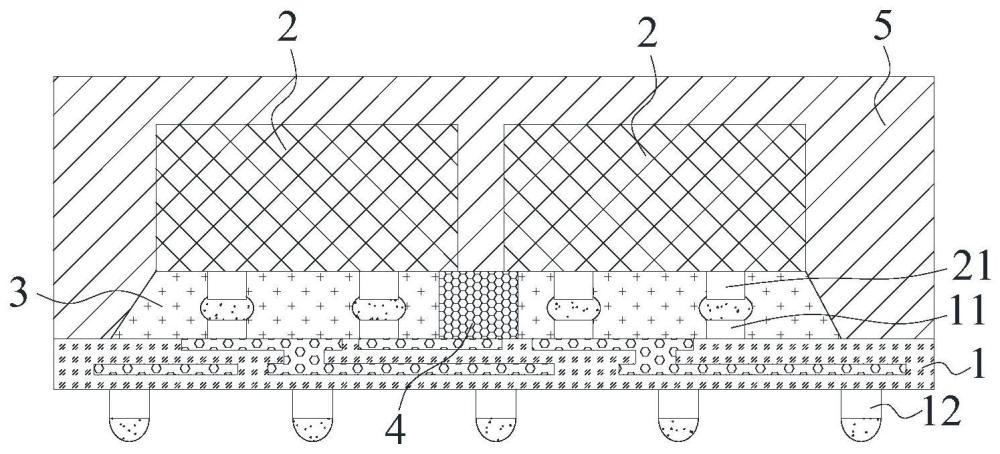

2、本公开实施例提供的半导体封装结构,包括中介层、多个半导体器件、底部填充层、挡墙层和包封层。其中,多个半导体器件位于所述中介层上并与所述中介层电连接,相邻的所述半导体器件之间具有间隙;底部填充层位于所述多个半导体器件和所述中介层之间;挡墙层位于所述中介层上且至少部分对应于相邻的所述半导体器件之间的所述间隙,所述挡墙层夹设于所述底部填充层中;包封层位于所述中介层、所述底部填充层和所述挡墙层上,且所述包封层包覆所述多个半导体器件。

3、在本公开的一些实施例中,所述挡墙层的高度尺寸等于或小于所述中介层与所述半导体器件之间的距离。

4、在本公开的一些实施例中,所述挡墙层的宽度尺寸大于相邻的所述半导体器件之间的所述间隙的尺寸,且所述挡墙层横跨相邻的两个所述半导体器件之间的所述间隙并至少部分支撑相邻的两个所述半导体器件。

5、在本公开的一些实施例中,所述挡墙层的宽度尺寸等于或小于相邻的所述半导体器件之间的所述间隙尺寸,且所述挡墙层位于所述中介层的对应于相邻的所述半导体器件之间的所述间隙的位置处。

6、在本公开的一些实施例中,所述挡墙层的宽度尺寸相同,或所述挡墙层的宽度尺寸自所述中介层向靠近所述半导体器件的方向逐渐减小。

7、在本公开的一些实施例中,所述挡墙层的高度尺寸为10~20μm。

8、在本公开的一些实施例中,所述挡墙层的宽度尺寸为50~100μm。

9、在本公开的一些实施例中,所述挡墙层包括聚氨酯层、硅层和铜层中的至少一种。

10、在本公开的一些实施例中,所述多个半导体器件之间具有多个所述间隙,所述挡墙层具有多个,每个所述挡墙层位于所述中介层上并至少部分对应于每个所述间隙,且所述挡墙层沿所述间隙的延伸方向延伸。

11、在本公开的一些实施例中,所述底部填充层包括第一树脂和掺杂于所述第一树脂中的颗粒状的第一填料,所述包封层包括第二树脂和掺杂于所述第二树脂中的颗粒状的第二填料;其中,所述第二填料的粒径大于所述第一填料的粒径,所述第二填料的占比大于所述第一填料的占比。

12、上述技术方案可知,本公开实施例的半导体封装结构具备以下优点和积极效果中的至少之一:

13、本公开实施例中,挡墙层位于中介层上且至少部分对应于相邻的半导体器件之间的间隙,且挡墙层夹设于底部填充层中,因此,挡墙层位于在底部填充层中容易出现沟槽的部位,使得中介层与半导体器件之间的填充物更加完整,避免包封层与底部填充层、挡墙层之间出现分层,提高封装的可靠性以及半导体封装结构的良率。

技术特征:

1.一种半导体封装结构,其特征在于,包括:

2.根据权利要求1所述的半导体封装结构,其特征在于,所述挡墙层的高度尺寸等于或小于所述中介层与所述半导体器件之间的距离。

3.根据权利要求2所述的半导体封装结构,其特征在于,所述挡墙层的宽度尺寸大于相邻的所述半导体器件之间的所述间隙的尺寸,且所述挡墙层横跨相邻的两个所述半导体器件之间的所述间隙并至少部分支撑相邻的两个所述半导体器件。

4.根据权利要求2所述的半导体封装结构,其特征在于,所述挡墙层的宽度尺寸等于或小于相邻的所述半导体器件之间的所述间隙尺寸,且所述挡墙层位于所述中介层的对应于相邻的所述半导体器件之间的所述间隙的位置处。

5.根据权利要求1至4中任一项所述的半导体封装结构,其特征在于,所述挡墙层的宽度尺寸相同,或所述挡墙层的宽度尺寸自所述中介层向靠近所述半导体器件的方向逐渐减小。

6.根据权利要求1所述的半导体封装结构,其特征在于,所述挡墙层的高度尺寸为10~20μm。

7.根据权利要求1所述的半导体封装结构,其特征在于,所述挡墙层的宽度尺寸为50~100μm。

8.根据权利要求1所述的半导体封装结构,其特征在于,所述挡墙层包括聚氨酯层、硅层和铜层中的至少一种。

9.根据权利要求1所述的半导体封装结构,其特征在于,所述多个半导体器件之间具有多个所述间隙,所述挡墙层具有多个,每个所述挡墙层位于所述中介层上并至少部分对应于每个所述间隙,且所述挡墙层沿所述间隙的延伸方向延伸。

10.根据权利要求1所述的半导体封装结构,其特征在于,所述底部填充层包括第一树脂和掺杂于所述第一树脂中的颗粒状的第一填料,所述包封层包括第二树脂和掺杂于所述第二树脂中的颗粒状的第二填料;

技术总结

本公开提供一种半导体封装结构。该半导体封装结构包括中介层、多个半导体器件、底部填充层、挡墙层和包封层。其中,多个半导体器件位于中介层上并与中介层电连接,相邻的半导体器件之间具有间隙;底部填充层位于多个半导体器件和中介层之间;挡墙层位于中介层上且至少部分对应于相邻的半导体器件之间的间隙,挡墙层夹设于底部填充层中;包封层位于中介层、底部填充层和挡墙层上,且包封层包覆多个半导体器件。本公开实施例的半导体封装结构,避免包封层与底部填充层、挡墙层之间出现分层,提高封装的可靠性以及半导体封装结构的良率。

技术研发人员:范增焰,王彪

受保护的技术使用者:长鑫科技集团股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!