半导体结构及其制造方法与流程

本公开实施例涉及半导体,尤其涉及一种半导体结构及其制造方法。

背景技术:

1、为了提高芯片内单位面积的集成度,可以将芯片的存储阵列(array)和外围电路(cmos)分别在两片晶圆上完成加工,然后进行晶圆到晶圆(wafer to wafer)的键合,以形成三维芯片。

2、目前,键合形成的三维芯片中仍然存在诸多问题有待解决。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其制造方法。

2、为达到上述目的,本公开的技术方案是这样实现的:

3、第一方面,本公开实施例提供一种半导体结构,所述半导体结构包括:

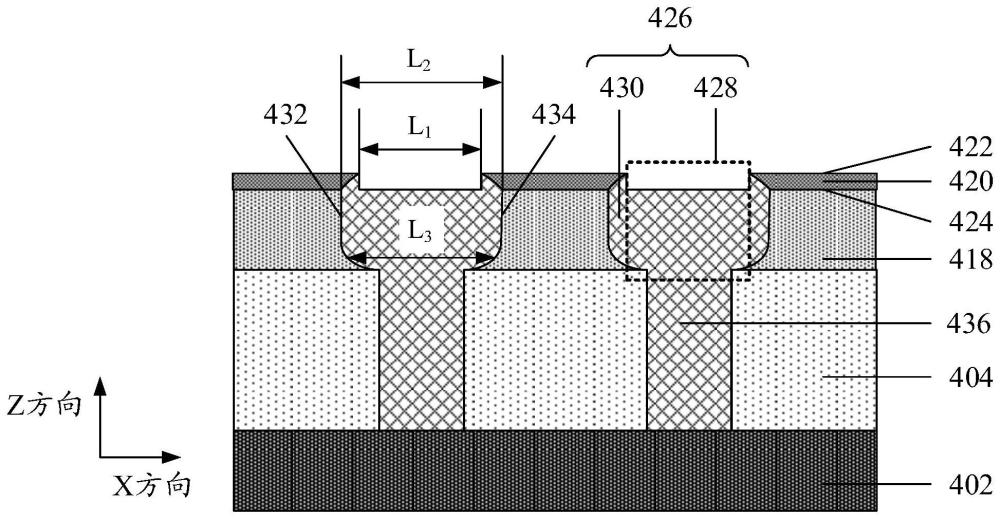

4、第一衬底,设置在所述第一衬底上的第一介质层以及设置在所述第一介质层中的第一互连结构;其中,所述第一介质层具有第一表面,所述第一互连结构具有第一中心区域和围绕所述第一中心区域的第一边缘区域,所述第一边缘区域被所述第一介质层的第一表面覆盖,所述第一介质层的第一表面不覆盖所述第一中心区域。

5、在一些实施例中,所述第一介质层还具有与所述第一表面相对的第二表面,所述第一边缘区域在第一方向上具有相对的第一侧壁和第二侧壁,在所述第一表面,所述第一侧壁和所述第二侧壁之间具有第一水平距离,在所述第二表面,所述第一侧壁和所述第二侧壁之间具有第二水平距离,所述第一水平距离不大于所述第二水平距离,其中,所述第一方向为所述第一互连结构的水平延伸方向。

6、在一些实施例中,所述第一衬底上还包括第二介质层,所述第一边缘区域和所述第一中心区域还包括掩埋在所述第二介质层中的部分。

7、在一些实施例中,所述第二介质层与所述第二表面接触,掩埋在所述第二介质层的第一侧壁和第二侧壁之间具有第三水平距离,所述第三水平距离不大于所述第二水平距离。

8、在一些实施例中,所述半导体结构还包括第二衬底,所述第二衬底上包括第三介质层以及设置在所述第三介质层中的第二互连结构,所述第三介质层和所述第一介质层不使用粘接剂直接粘合,所述第一互连结构和所述第二互连结构不使用粘接剂直接粘合。

9、在一些实施例中,所述第二互连结构具有与所述第一中心区域接合的第二中心区域和被所述第三介质层掩埋的第二边缘区域。

10、在一些实施例中,所述第二边缘区域与所述第一边缘区域在第一方向上存在预定偏移量,所述预定偏移量为0nm至50nm,其中,所述第一方向为所述第一互连结构的水平延伸方向。

11、第二方面,本公开实施例提供一种半导体结构的制造方法,所述方法包括:

12、提供第一衬底和位于所述第一衬底上的第二介质材料层,所述第二介质材料层内具有第一沟槽;

13、在所述第一沟槽内填充导电材料,所述导电材料具有突出于所述第二介质材料层的表面;

14、在所述第二介质材料层以及所述导电材料的突出表面沉积第一介质材料层;

15、对所述第一介质材料层、所述第二介质材料层以及所述导电材料进行表面处理,形成具有第一表面的第一介质层和第一互连结构,所述第一互连结构具有第一中心区域和围绕所述第一中心区域的第一边缘区域,其中,形成的第一介质层的第一表面覆盖所述第一边缘区域,所述第一表面不覆盖所述第一中心区域。

16、在一些实施例中,所述提供第一衬底和位于所述第一衬底上的第二介质材料层,所述第二介质材料层内具有第一沟槽,包括:

17、采用刻蚀工艺在所述第二介质材料层中形成所述第一沟槽,蚀刻完成后,所述第一沟槽在第一方向上具有相对的第一侧壁和第二侧壁,第一侧壁和第二侧壁之间具有不同的水平距离,所述第一方向为所述第一互连结构的水平延伸方向。

18、在一些实施例中,所述方法还包括:

19、提供第二衬底,所述第二衬底具有第三介质层和设置在所述第三介质层中的第二互连结构,将所述第二衬底与所述第一衬底对准,以将所述第三介质层和所述第一介质层不使用粘接剂直接粘合,所述第一互连结构和所述第二互连结构不使用粘接剂直接粘合。

20、本公开实施例提供一种半导体结构及其制造方法。本公开实施例中,第一互连结构具有第一中心区域和围绕第一中心区域的第一边缘区域,第一介质层的第一表面覆盖第一边缘区域且暴露第一中心区域,如此在后续键合过程中,第一互连结构受热膨胀时第一边缘区域和第一介质层相互挤压,以促进第一中心区域膨胀进而促进键合过程。

技术特征:

1.一种半导体结构,其特征在于,所述半导体结构包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一介质层还具有与所述第一表面相对的第二表面,所述第一边缘区域在第一方向上具有相对的第一侧壁和第二侧壁,在所述第一表面,所述第一侧壁和所述第二侧壁之间具有第一水平距离,在所述第二表面,所述第一侧壁和所述第二侧壁之间具有第二水平距离,所述第一水平距离不大于所述第二水平距离,其中,所述第一方向为所述第一互连结构的水平延伸方向。

3.根据权利要求2所述的半导体结构,其特征在于,所述第一衬底上还包括第二介质层,所述第一边缘区域和所述第一中心区域还包括掩埋在所述第二介质层中的部分。

4.根据权利要求3所述的半导体结构,其特征在于,所述第二介质层与所述第二表面接触,掩埋在所述第二介质层的第一侧壁和第二侧壁之间具有第三水平距离,所述第三水平距离不大于所述第二水平距离。

5.根据权利要求1至4中任一项所述的半导体结构,其特征在于,所述半导体结构还包括第二衬底,所述第二衬底上包括第三介质层以及设置在所述第三介质层中的第二互连结构,所述第三介质层和所述第一介质层不使用粘接剂直接粘合,所述第一互连结构和所述第二互连结构不使用粘接剂直接粘合。

6.根据权利要求5所述的半导体结构,其特征在于,所述第二互连结构具有与所述第一中心区域接合的第二中心区域和被所述第三介质层掩埋的第二边缘区域。

7.根据权利要求6所述的半导体结构,其特征在于,所述第二边缘区域与所述第一边缘区域在第一方向上存在预定偏移量,所述预定偏移量为0nm至50nm,其中,所述第一方向为所述第一互连结构的水平延伸方向。

8.一种半导体结构的制造方法,其特征在于,所述方法包括:

9.根据权利要求8所述的制造方法,其特征在于,所述提供第一衬底和位于所述第一衬底上的第二介质材料层,所述第二介质材料层内具有第一沟槽,包括:

10.根据权利要求8所述的制造方法,其特征在于,所述方法还包括:

技术总结

本公开实施例提供一种半导体结构及其制造方法。所述半导体结构包括:第一衬底,设置在所述第一衬底上的第一介质层以及设置在所述第一介质层中的第一互连结构;其中,所述第一介质层具有第一表面,所述第一互连结构具有第一中心区域和围绕所述第一中心区域的第一边缘区域,所述第一边缘区域被所述第一介质层的第一表面覆盖,所述第一介质层的第一表面不覆盖所述第一中心区域。

技术研发人员:汪秀山,张志伟

受保护的技术使用者:长鑫科技集团股份有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!