量子点封装件及其制作方法、芯片及其制作方法及封装器件与流程

本发明涉及显示器件的,尤其涉及一种量子点封装件及其制作方法、芯片及其制作方法及封装器件。

背景技术:

1、近年来,随着用户对显示设备性能体验的要求不断提高,高色域显示设备愈加受到消费者的喜爱。作为在业界被广泛用来衡量显示设备色彩性能的指标,ntsc色域值越高,显示的色彩效果就越丰富突出,可获得更加真实的色彩还原这其中,由于量子点技术在显示领域的应用可以实现超高色域,因此其应用方式得到了行业的极大关注。

2、量子点会首先封装在玻璃中以形成量子点封装件,然后再将量子点封装件应用至芯片或者封装器件中。目前,量子点封装件在对量子点进行封装时通常仅采用硅胶或树脂包覆量子点封装件的表面以密封量子点,隔绝水氧。由于硅胶或树脂为有机物,分子链较大,容易出现皲裂的问题,造成水氧隔绝性不佳,影响量子点封装件的气密性,进而对显示设备的显示效果产生影响。

技术实现思路

1、本发明的目的在于提供一种量子点封装件及其制作方法、芯片及其制作方法及封装器件,旨在解决现有技术中量子点封装件水氧隔绝性能差,影响气密性和显示效果的问题。

2、本发明第一方面提供一种量子点封装件,其包括:

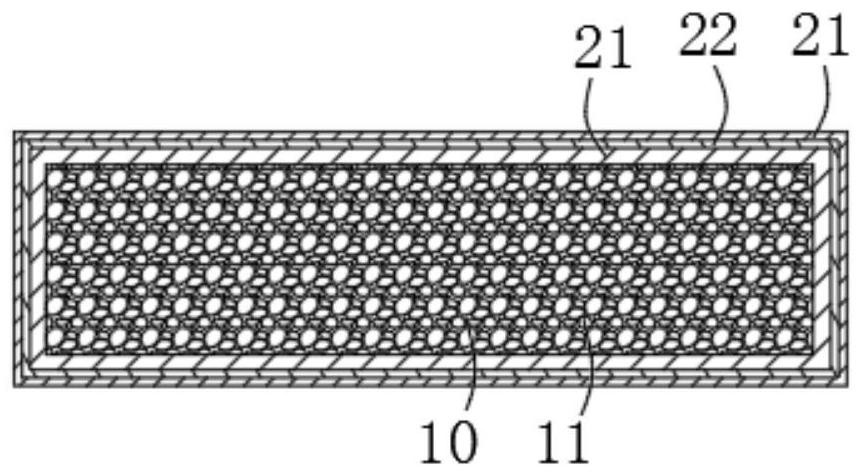

3、载体,所述载体为透光的固态材质制成,且所述载体的表面或表面及内部有多个微孔,所述微孔内装载有量子点;以及

4、镀膜层,所述镀膜层为透光材质制成,所述镀膜层包覆于所述载体的外表面,所述镀膜层包括至少两层有机层和至少一层无机层,所述有机层和所述无机层在所述镀膜层的厚度方向上由内至外依次交替设置。

5、在其中一个实施例中,所述镀膜层的层数设为奇数层,位于所述镀膜层的厚度方向的最内一层和最外一层均设为有机层,且位于最内一层的所述有机层与所述载体直接接触。

6、在其中一个实施例中,位于最内一层的所述有机层的厚度大于等于100nm,其余层的所述有机层和所述无机层的厚度范围均为:40nm~50nm。

7、在其中一个实施例中,所述有机层的材质为丙烯酸,所述无机层的材质为aln、al2o3、si4n3、sio2其中的任意一种,所述载体为玻璃。

8、本发明第二方面提供一种量子点封装件的制作方法,其包括如下步骤:

9、选用透光的固态材质作为载体,并在所述载体表面或表面及内部加工出多个微孔结构;

10、将所述载体浸泡于由量子点材料与特定溶剂充分混合形成的量子点溶液中预设时长;

11、浸泡结束,将所述载体取出并进行干燥处理;

12、将装载有量子点的所述载体置入镀膜设备进行镀膜层加工,所述镀膜层为透光材质制成,所述镀膜层包覆于所述载体的外表面,所述镀膜层包括至少两层有机层和至少一层无机层,所述有机层和所述无机层在所述镀膜层的厚度方向上由内至外依次交替设置;

13、镀膜加工结束,得到加工成型的量子点封装件。

14、本发明第三方面提供一种芯片,其包括电极和如上所述的量子点封装件,所述电极设于所述芯片的一侧,所述量子点封装件设于所述芯片上与所述电极相对的另一侧。

15、在其中一个实施例中,所述芯片还包括键合层和外延层,所述键合层的一侧与所述量子点封装件键合连接,另一侧与所述外延层连接,所述外延层包括n型半导体层和p型半导体层,以及设于所述n型半导体层与所述p型半导体层之间的多量子阱层,所述电极设于所述外延层的最外侧,且所述电极包括与所述n型半导体层电连接的第一电极和与所述p型半导体层连接的第二电极,所述外延层侧面包覆有挡光胶层。

16、本发明第四方面提供一种芯片的制作方法,其包括如下步骤:

17、步骤a:提供衬底,在衬底上进行外延层生长,所述外延层包括n型半导体层与p型半导体层,和设于n型半导体层与p型半导体层之间的多量子阱层;在所述外延层上覆盖键合层;

18、步骤b:将权利要求1至4任一项所述的量子点封装件或权利要求5所述的量子点封装件的制作方法制造的量子点封装件与所述键合层进行键合连接;

19、步骤c:去除衬底,并在外延层上制作电极,形成芯片雏形;

20、步骤d:在芯片雏形的外延层侧面设置挡光胶层,得到完整的芯片。

21、在其中一个实施例中,在步骤b中,先分别对键合层与量子点封装件相互键合的表面进行表面清洗、化学机械抛光和活化处理,然后在高温高压下将所述量子点封装件与所述键合层键合成为一体;

22、在步骤c中,先用激光去除衬底,然后用光刻工艺去掉部分外延层,露出n型半导体层与p型半导体层的至少部分表面,再在外延层表面溅射金属膜层形成分别与n型半导体层电连接的第一电极和与p型半导体层连接的第二电极。

23、在步骤d中,先将多个芯片雏形,在一平面上沿第一方向和第二方向上整齐排列,形成芯片阵列,其中,各芯片之间存在间隙;第一方向和第二方向相互垂直;然后在各芯片之间的间隙中填充挡光胶,再沿着各芯片的间隙切割芯片阵列,得到完成的芯片。

24、本发明第五方面提供一种封装器件,其包括封装体和封装于所述封装体内的芯片,所述芯片为上述的芯片,或者为采用上述的芯片的制作方法制造的芯片。

25、实施本发明实施例,将具有如下有益效果:

26、本方案的量子点封装件,通过在载体上加工出多个微孔,从而使微孔能容纳量子点,以实现载体装载量子点,进一步的在载体的外部加工包覆镀膜层,能实现将量子点封装,且由于本申请中镀膜层采用至少两层有机层和至少一层无机层的多层结构设计,有机层和无机层在镀膜层的厚度方向由内至外依次交替设置,相较于现有技术中采用树脂或硅胶的封装方式而言,无机层对水氧的隔绝效果比树脂和硅胶好,但是无机层也存在容易皲裂的问题,故在无机层周围进一步设置有机层作为保护,有机层具有一定的韧性,可以弥补无机层容易皲裂的问题;而有机层气密性不足且容易黄变,故需要在有机层外部包覆无机层,改善有机层气密性不足和容易黄变的问题,故本申请中,无机层的分子较小,容易进入有机层的大分子链之间,水氧隔绝性佳,有机层和无机层相互结合,优势互补,给量子点封装件提供全方位气密性保障,有助于保证采用了该量子点封装件的显示设备的显示效果。

技术特征:

1.一种量子点封装件,其特征在于,包括:

2.根据权利要求1所述的量子点封装件,其特征在于,所述镀膜层的层数设为奇数层,位于所述镀膜层的厚度方向的最内一层和最外一层均设为有机层,且位于最内一层的所述有机层与所述载体直接接触。

3.根据权利要求2所述的量子点封装件,其特征在于,位于最内一层的所述有机层的厚度大于等于100nm,其余层的所述有机层和所述无机层的厚度范围均为:40nm~50nm。

4.根据权利要求1至3任一项所述的量子点封装件,其特征在于,所述有机层的材质为丙烯酸,所述无机层的材质为aln、al 2o 3、si4n 3、sio2其中的任意一种;所述载体为玻璃。

5.一种量子点封装件的制作方法,其特征在于,包括如下步骤:

6.一种芯片,其特征在于,包括电极和如权利要求1至4任一项所述的量子点封装件,所述电极设于所述芯片的一侧,所述量子点封装件设于所述芯片上与所述电极相对的另一侧。

7.根据权利要求6所述的芯片,其特征在于,所述芯片还包括键合层和外延层,所述键合层的一侧与所述量子点封装件键合连接,另一侧与所述外延层连接,所述外延层包括n型半导体层和p型半导体层,以及设于所述n型半导体层与所述p型半导体层之间的多量子阱层,所述电极设于所述外延层的最外侧,且所述电极包括与所述n型半导体层电连接的第一电极和与所述p型半导体层连接的第二电极,所述外延层侧面包覆有挡光胶层。

8.一种芯片的制作方法,其特征在于,包括如下步骤:

9.根据权利要求8所述的芯片的制作方法,其特征在于,

10.一种封装器件,其特征在于,包括封装体和封装于所述封装体内的芯片,所述芯片为权利要求6或7所述的芯片,或者为采用权利要求8或9所述的芯片的制作方法制造的芯片。

技术总结

本发明涉及一种量子点封装件及其制作方法、芯片及其制作方法及封装器件。量子点封装件包括载体,所述载体为透光的固态材质制成,所述载体的表面或表面及内部有多个微孔,所述微孔内装载有量子点;以及镀膜层,所述镀膜层为透光材质制成,所述镀膜层包覆于所述载体的外表面,所述镀膜层包括至少两层有机层和至少一层无机层,所述有机层和所述无机层在所述镀膜层的厚度方向上由内至外依次交替设置。本申请中,无机层的分子较小,容易进入有机层的大分子链之间,水氧隔绝性佳,有机层和无机层相互结合,优势互补,给量子点封装件提供全方位气密性保障,有助于保证采用了该量子点封装件的显示设备的显示效果。

技术研发人员:马文波,孙平如,邢美正

受保护的技术使用者:惠州市聚飞光电有限公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!