半导体器件的制作方法

本公开涉及半导体器件,具体地,涉及一种包括导电结构的半导体器件。

背景技术:

1、半导体器件包括由金属氧化物半导体场效应晶体管(mos-fet)组成的集成电路。为了满足对具有小图案尺寸的半导体器件的渐增需求,mos-fet的尺寸正在减小。mos-fet的尺度缩小可以导致半导体器件的操作性能劣化。正在进行各种研究来克服与半导体器件的尺度缩小相关联的技术限制并且实现高性能的半导体器件。

技术实现思路

1、介于半导体器件的模制层和导电层之间的衬垫能够有助于稳定地形成防止在其中形成接缝(seam)的导电层。在一些实现方式中,使用目前公开的工艺的半导体器件不太可能在化学机械抛光(cmp)期间经历熔融和残留物问题,因此表现出提高的可靠性。

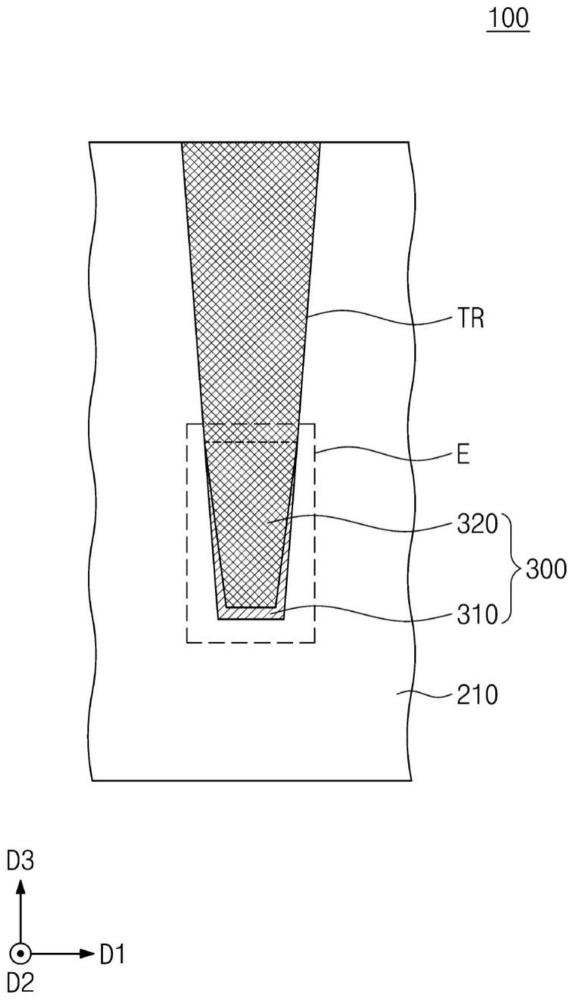

2、一般而言,本说明书中描述的主题的创新方面能够被体现在一种半导体器件中,所述半导体器件包括:模制层,所述模制层限定沟槽;以及导电结构,所述导电结构设置在所述沟槽上。所述导电结构可以包括导电层和衬垫,并且所述导电层可以包括上部和下部。所述衬垫可以包括基体部和位于所述基体部上的侧壁部,并且所述导电层的上部可以设置在比所述衬垫的所述侧壁部高的高度(level)。所述衬垫的所述侧壁部可以介于所述导电层的所述下部与所述模制层之间,并且所述衬垫的所述基体部的顶表面可以与所述导电层的所述下部的底表面接触。所述衬垫的所述侧壁部的宽度随着高度增大而减小。

3、另一总体方面能够被体现在一种半导体器件中,所述半导体器件包括:模制层,所述模制层限定沟槽;以及导电结构,所述导电结构设置在所述沟槽上。所述导电结构可以包括导电层和衬垫,并且所述导电层可以包括上部和下部。所述衬垫可以包括基体部和位于所述基体部上的侧壁部,并且所述侧壁部可以介于所述导电层的所述下部与所述模制层之间。所述侧壁部可以包括与所述导电层的所述下部接触的内侧壁和与所述模制层接触的外侧壁。所述侧壁部的所述外侧壁与所述基体部的底表面之间的角度可以小于所述侧壁部的所述内侧壁与所述基体部的顶表面之间的角度。

4、另一总体方面能够被体现在一种半导体器件中,所述半导体器件包括:模制层,所述模制层限定沟槽;以及导电结构,所述导电结构设置在所述沟槽上。所述导电结构可以包括导电层和衬垫,并且所述衬垫可以介于所述模制层与所述导电层之间。所述导电层和所述衬垫可以包括钼(mo),并且所述衬垫还可以包括氧(o)。

技术特征:

1.一种半导体器件,所述半导体器件包括:

2.根据权利要求1所述的半导体器件,其中,所述导电层和所述衬垫包括钼,并且所述衬垫还包括氧。

3.根据权利要求1所述的半导体器件,其中,所述导电层包括钼,并且所述衬垫包括氮化钛。

4.根据权利要求1所述的半导体器件,其中,所述导电层和所述衬垫包括氯,并且所述导电层的氯浓度高于所述衬垫的氯浓度。

5.根据权利要求1所述的半导体器件,所述半导体器件还包括包含硅的衬底,其中,所述模制层和所述导电结构设置在所述衬底上。

6.根据权利要求1所述的半导体器件,所述半导体器件还包括被所述模制层包围的材料层,

7.根据权利要求6所述的半导体器件,其中,所述材料层包括金属材料。

8.根据权利要求6所述的半导体器件,其中,所述材料层包括硅。

9.根据权利要求1所述的半导体器件,其中,所述导电结构的底表面的宽度等于或小于20nm。

10.根据权利要求1所述的半导体器件,其中,所述导电结构的高度在100nm至1000nm的范围内。

11.一种半导体器件,所述半导体器件包括:

12.根据权利要求11所述的半导体器件,其中,所述导电层和所述衬垫包括钼和氯,

13.根据权利要求11所述的半导体器件,其中,所述导电结构还包括形成在所述导电层的所述下部中的接缝。

14.根据权利要求11所述的半导体器件,所述半导体器件还包括介于所述模制层与所述导电结构之间的绝缘层,

15.根据权利要求11所述的半导体器件,其中,所述导电层和所述衬垫包括钼和氧,并且

16.根据权利要求11所述的半导体器件,其中,所述模制层包括氮化物材料。

17.根据权利要求11所述的半导体器件,其中,所述导电层的所述上部包括与所述模制层接触的侧壁,并且

18.一种半导体器件,所述半导体器件包括:

19.根据权利要求18所述的半导体器件,其中,所述导电层包括上部和下部,

20.根据权利要求18所述的半导体器件,其中,所述模制层包括氧化物材料。

技术总结

一种半导体器件包括:模制层,所述模制层限定沟槽;以及导电结构,所述导电结构设置在所述沟槽上。所述导电结构包括导电层和衬垫,并且所述导电层包括上部和下部。所述衬垫包括基体部和位于所述基体部上的侧壁部,并且所述导电层的所述上部设置在比所述衬垫的所述侧壁部高的高度。所述衬垫的所述侧壁部介于所述导电层的所述下部与所述模制层之间,并且所述衬垫的所述基体部的顶表面与所述导电层的所述下部的底表面接触。所述衬垫的所述侧壁部的宽度随着高度增大而减小。

技术研发人员:柳东坤,李宣姃,黄桢元,孔榠浒,河龙湖

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/11/7

- 还没有人留言评论。精彩留言会获得点赞!