一种具有低欧姆接触电阻率的GaN基HEMT器件及其制备方法与流程

本发明涉及半导体器件,具体涉及一种具有低欧姆接触电阻率的gan基hemt器件及其制备方法。

背景技术:

1、高电子迁移率晶体管(high electron mobility transistor,hemt)具有高频、高压、高温等优点,是固态微波功率器件和功率电子器件未来的发展方向。gan基hemt具有禁带宽度大、击穿场强高、饱和电子漂移速率高和化学稳定性好等优点,成为实现高频、大功率、高效应用场景的核心器件。

2、高性能gan hemt器件的关键在于提升器件的饱和电流密度(idmax)以及降低膝点电压(vknee),两者都可以通过降低源漏串联电阻实现。源漏串联电阻包括通道电阻和源漏欧姆接触电阻rc,为降低串联电阻,一方面可以通过合理的外延结构和器件结构设计降低通道电阻,另一个重要方面就是降低源漏欧姆接触电阻,尤其是在器件尺寸微缩的情况下,源漏欧姆接触更是成为决定器件性能的关键因素。

3、近年来,采用二次外延在源漏欧姆接触区生长n型重掺gan层成为降低gan基hemt欧姆接触电阻的重要技术,该工艺利用重掺杂gan与金属接触,这样形成的金半接触势垒宽度很窄,有助于电子隧穿产生大电流,即使采用未退火的欧姆金属层也能实现小于0.1ω·mm的极低欧姆接触电阻。

4、n型gan二次外延可以通过分子束外延(mbe)和金属有机化学气相沉积(mocvd)技术实现,采用硅或锗作为n型掺杂源,在gan二次外延的过程中,高温生长很容易造成原子分离和扩散,导致已有的异质界面极化效应减弱,造成二维电子气(2deg)特性退化。此外,高剂量的si或ge原子并入还会引起gan晶格发生畸变,导致gan晶体质量及表面形貌出现退化。

5、综上所述,现有hemt器件工艺技术难以兼顾低欧姆接触以及良好的2deg特性和材料表面形貌,基于此,本发明提供了一种具有低欧姆接触电阻率的gan基hemt器件及其制备方法。

技术实现思路

1、基于上述表述,本发明提供了一种具有低欧姆接触电阻率的gan基hemt器件及其制备方法,以使制备得到的gan基hemt器件能够兼顾低欧姆接触以及良好的2deg特性。

2、本发明解决上述技术问题的技术方案如下:

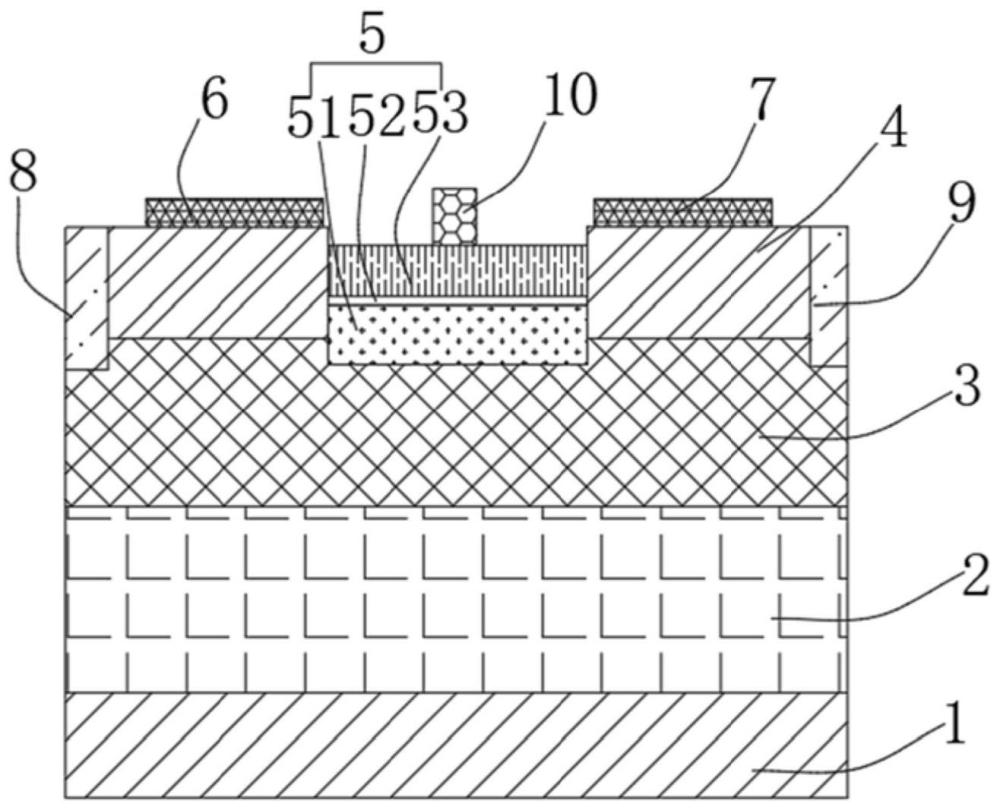

3、第一方面,本发明提供一种具有低欧姆接触电阻率的gan基hemt器件,包括:衬底、缓冲层、非掺杂u-gan层、重掺杂n+gan层及异质结;

4、所述缓冲层设于所述衬底上;

5、所述非掺杂u-gan层设于所述缓冲层上;

6、所述重掺杂n+gan层设于所述非掺杂u-gan层上,所述重掺杂n+gan层的中部设有凹槽;

7、所述异质结设于所述凹槽中,且所述异质结的底部与所述非掺杂u-gan层的上表面接触。

8、在上述技术方案的基础上,本发明还可以做如下改进。

9、进一步的,所述具有低欧姆接触电阻率的gan基hemt器件还包括源极和漏极;

10、所述源极和所述漏极间隔布设于所述非掺杂u-gan层上,且分别位于所述异质结的两侧。

11、进一步的,所述具有低欧姆接触电阻率的gan基hemt器件还包括第一隔离层和第二隔离层;

12、所述第一隔离层和所述第二隔离层分别采用离子注入的方式设于所述重掺杂n+gan层的两侧。

13、进一步的,所述具有低欧姆接触电阻率的gan基hemt器件还包括栅极;

14、所述栅极设于所述异质结的上表面。

15、进一步的,所述异质结包括沟道层、插入层和势垒层;

16、所述沟道层设于位于所述凹槽处的非掺杂u-gan的上表面;

17、所述插入层设于所述沟道层上;

18、所述势垒层设于所述插入层上。

19、进一步的,所述沟道层为gan沟道层;

20、所述插入层为aln插入层;

21、所述势垒层为algan、inaln、inalgan或aln势垒层。

22、第二方面,本发明还提供一种用于制作如第一方面所述的具有低欧姆接触电阻率的gan基hemt器件的制备方法,包括:

23、在衬底上自下而上依次生长缓冲层、非掺杂u-gan层和重掺杂n+gan层,得到gan基hemt基底材料;

24、在gan基hemt基底材料表面生长一层sio2薄膜作为掩膜层;

25、对所述掩膜层和所述重掺杂n+gan层进行干法刻蚀,形成带有沟槽结构的图形化外延片;

26、将所述图形化外延片载入外延生长腔体,生长异质结;

27、去除所述掩膜层,形成gan基hemt外延结构。

28、在上述技术方案的基础上,本发明还可以做如下改进。

29、进一步的,在形成gan基hemt外延结构之后,还包括:

30、对所述gan基hemt外延结构依次进行光刻、欧姆金属蒸镀和金属剥离,形成源极和漏极;

31、依次采用光刻、离子注入以及去胶工艺,以使hemt器件之间形成器件隔离。

32、进一步的,在形成器件隔离之后,还包括:

33、依次采用光刻、栅金属蒸镀以及金属剥离,在所述源极和所述漏极间的异质结上形成栅极。

34、进一步的,所述生长异质结,具体包括:

35、在所述图形化外延片的沟槽区域依次生长沟道层、插入层和势垒层。

36、与现有技术相比,本申请的技术方案具有以下有益技术效果:

37、本发明提供的具有低欧姆接触电阻率的gan基hemt器件通过设置衬底、缓冲层、非掺杂u-gan层、重掺杂n+gan层及异质结;缓冲层设于衬底上;非掺杂u-gan层设于缓冲层上;重掺杂n+gan层设于非掺杂u-gan层上,重掺杂n+gan层的中部设有凹槽;异质结设于凹槽中,且异质结的底部与非掺杂u-gan层的上表面接触。

38、相较于现有技术,本发明提供的具有低欧姆接触电阻率的gan基hemt器件及其制备方法,具有如下优点:

39、1.采用预先外延形成重掺杂gan外延薄层,有利于获得高掺杂浓度和良好的表面形貌,从而降低欧姆接触电阻,改善器件的传输特性和频率特性,降低功率损耗。

40、2.预先外延生长n+gan,这样生长的gan中si掺杂浓度与器件版图和光罩设计无相关性,外延工艺一致性较好。

41、3.通过二次外延引入gan基异质结形成二维电子气导电通道,与常规重掺n+gan源漏二次外延技术相比,可以避免再生长导致的异质界面原子分离和扩散,从而保持良好的二维电子气传输特性。

技术特征:

1.一种具有低欧姆接触电阻率的gan基hemt器件,其特征在于,包括:衬底、缓冲层、非掺杂u-gan层、重掺杂n+gan层及异质结;

2.根据权利要求1所述的具有低欧姆接触电阻率的gan基hemt器件,其特征在于,所述具有低欧姆接触电阻率的gan基hemt器件还包括源极和漏极;

3.根据权利要求1所述的具有低欧姆接触电阻率的gan基hemt器件,其特征在于,所述具有低欧姆接触电阻率的gan基hemt器件还包括第一隔离层和第二隔离层;

4.根据权利要求1所述的具有低欧姆接触电阻率的gan基hemt器件,其特征在于,所述具有低欧姆接触电阻率的gan基hemt器件还包括栅极;

5.根据权利要求1所述的具有低欧姆接触电阻率的gan基hemt器件,其特征在于,所述异质结包括沟道层、插入层和势垒层;

6.根据权利要求5所述的具有低欧姆接触电阻率的gan基hemt器件,其特征在于,所述沟道层为gan沟道层;

7.一种用于制作如权利要求1至6任一项所述的具有低欧姆接触电阻率的gan基hemt器件的制备方法,其特征在于,包括:

8.根据权利要求7所述的制备方法,其特征在于,在形成gan基hemt外延结构之后,还包括:

9.根据权利要求8所述的制备方法,其特征在于,在形成器件隔离之后,还包括:

10.根据权利要求7所述的制备方法,其特征在于,所述生长异质结,具体包括:

技术总结

本发明提供一种具有低欧姆接触电阻率的GaN基HEMT器件及其制备方法,上述GaN基HEMT器件包括衬底、缓冲层、非掺杂u‑GaN层、重掺杂n+GaN层及异质结;缓冲层设于衬底上;非掺杂u‑GaN层设于缓冲层上;重掺杂n+GaN层设于非掺杂u‑GaN层上,重掺杂n+GaN层的中部设有凹槽;异质结设于凹槽中,且异质结的底部与非掺杂u‑GaN层的上表面接触。该器件预先外延生长n+GaN层,这样生长的GaN中Si掺杂浓度与器件版图和光罩设计无相关性,外延工艺一致性较好;通过二次外延引入GaN基异质结形成二维电子气导电通道,与常规重掺n+GaN源漏二次外延技术相比,可以避免再生长导致的异质界面原子分离和扩散,从而保持良好的二维电子气传输特性。

技术研发人员:潘磊,卢双赞,柳俊

受保护的技术使用者:湖北九峰山实验室

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!