一种集成异质结二极管的MOSFET器件及制备方法与流程

本发明涉及半导体,尤其是指一种集成异质结二极管的mosfet器件及制备方法。

背景技术:

1、mosfet(metal-oxide-semiconductor field-effect transistor)金属氧化物半导体场效应管是一种常用半导体器件,其用于在电子电路中控制电流流动,实现放大、开关和调制电流功能;第三代半导体碳化硅凭借较宽的禁带宽度、高临界击穿电场和高饱和漂移速率等特点,突破硅基器件的限制,被广泛应用于电力电子系统。

2、sic mosfet由于较宽的禁带宽度,使用中存在双极性退化的问题;在寄生体二极管作为续流二极管时因承受高电流,双极退化效应更加严重,增大了器件的导通电阻,动态损耗增大,可靠性降低;现有技术中反并联肖特基二极管作为续流二极管,但会在电路中引入额外的电感和电容。

技术实现思路

1、为此,本发明所要解决的技术问题在于克服现有技术中mosfet器件寄生体二极管作为续流二极管时双极退化效应严重的技术难点,提供一种集成异质结二极管的mosfet器件及制备方法,在沟槽栅拐角处集成异质结二极管,改善寄生体二极管的特性,降低开关损耗。

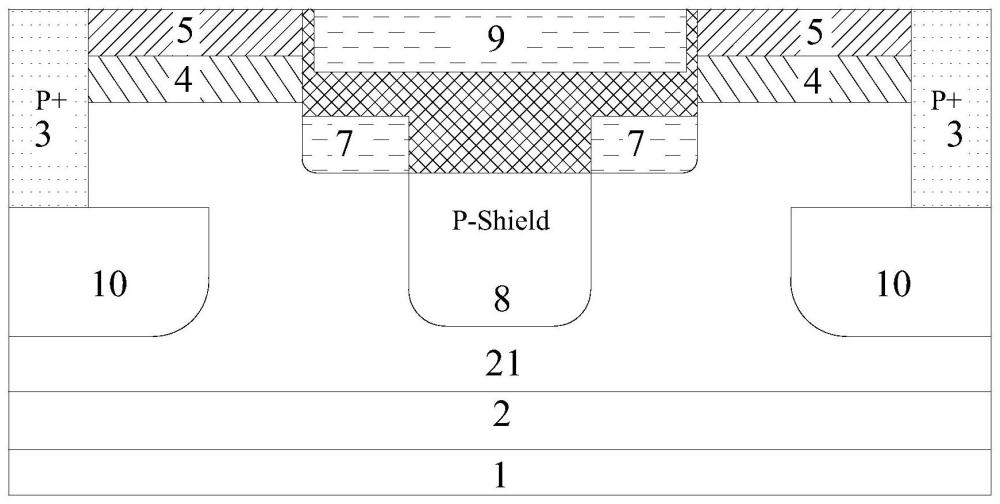

2、第一方面,为解决上述技术问题,本发明提供了一种集成异质结二极管的mosfet器件,其包括,

3、衬底层,所述衬底层设置为第一导电类型;

4、外延层,所述外延层位于所述衬底层上方且设置为第一导电类型;

5、电流分散层,所述电流分散层位于所述外延层上方;

6、凸形结构,所述凸形结构位于所述电流分散层上端中部,其包括自下而上设置的凸起部和基部,所述基部设置为沟槽,所述凸起部设置为p-shield层;所述基部包括第一单晶硅和第二单晶硅,所述第一单晶硅在宽度方向上位于所述p-shield层的两侧对称设置,且与所述电流分散层接触;所述第二单晶硅位于所述凸形结构的顶部,所述第一单晶硅和所述第二单晶硅之间设置有氧化层;

7、p型基区,所述p型基区位于所述电流分散层上端的两侧对称设置;

8、p型区,所述p型区位于所述电流分散层两侧对称设置,且所述p型区位于所述p型基区底部;

9、p型阱区,所述p型阱区位于所述p型基区和所述凸形结构之间,且在所述凸形结构的基部两侧对称设置;

10、n型源区,所述n型源区位于所述p型阱区上方,所述n型源区和所述p型阱区靠近所述凸形结构的一侧被所述氧化层隔离。

11、在本发明的一个实施例中,所述氧化层包括第一栅氧化层和第二栅氧化层,所述第一栅氧化层位于所述凸形结构的所述沟槽的两侧壁,所述第二栅氧化层位于所述p-shield层上方隔离所述第一单晶硅,所述第二栅氧化层还位于所述第一单晶硅上方隔离所述第二单晶硅和所述第一单晶硅。

12、在本发明的一个实施例中,所述p-shield层的宽度为1μm~3μm,所述p-shield层的厚度为4μm~8μm。

13、在本发明的一个实施例中,所述p-shield层底部两端呈圆弧状,所述第一单晶硅底部远离所述氧化层的一端呈圆弧状。

14、在本发明的一个实施例中,所述p型基区的注入剂量为5×1014cm2~1.5×1015cm2;所述p型阱区的注入剂量为5×1013cm2~6×1014cm2;所述n型源区的注入剂量为5×1014cm2~1.5×1015cm2;所述p型区的注入剂量为5×1015cm2~1.5×1016cm2。

15、在本发明的一个实施例中,还包括漏极金属,所述漏极金属接触所述衬底层背离所述外延层的一侧表面,并与所述衬底层电耦合,所述衬底层设置为碳化硅衬底。

16、第二方面,本发明还提供一种集成异质结二极管的mosfet器件的制备方法,用于制备上述任一实施例所述的集成异质结二极管的mosfet器件,所述制备方法包括以下步骤:

17、步骤s1,所述衬底层表面通过外延工艺生长所述外延层,刻蚀去除部分所述外延层并填入所述电流分散层;

18、步骤s2,在所述电流分散层通过光刻和离子注入工艺注入p型半导体杂质形成所述p型基区;在所述p型基区的一端注入p型半导体杂质形成所述p型阱区;在所述p型阱区注入n型半导体杂质形成所述n型源区;

19、步骤s3,通过沟槽刻蚀工艺在所述电流分散层刻蚀得到两个第一沟槽;所述第一沟槽底部回填所述第一单晶硅,所述第一单晶硅上部通过热氧化工艺制得第三栅氧化层;

20、步骤s4,在两个所述第一沟槽之间向所述电流分散层内注入p型半导体杂质形成所述p-shield层;

21、步骤s5,通过湿法刻蚀所述第三栅氧化层,保留其位于所述第一沟槽侧壁的区域得到第一栅氧化层;同时通过沟槽刻蚀工艺刻蚀两个所述第一沟槽在宽度方向上的间隔区域,连通两个所述第一沟槽;

22、步骤s6,通过热氧化工艺生长第二栅氧化层;

23、步骤s7,在所述第二栅氧化层上方回填所述第二单晶硅;

24、步骤s8,在所述p型基区底部通过离子注入工艺注入p型半导体杂质得到所述p型区。

25、在本发明的一个实施例中,所述第一沟槽的深度均设置为1.7μm~3.8μm。

26、在本发明的一个实施例中,所述第一单晶硅的厚度为1μm~2μm,所述第一栅氧化层位于所述第一沟槽侧壁和所述第二单晶硅之间,且厚度为0.7μm~1.8μm。

27、在本发明的一个实施例中,所述第二栅氧化层的厚度为1.5μm~2.5μm。

28、本发明的上述技术方案相比现有技术具有以下优点:

29、本发明所述的一种集成异质结二极管的mosfet器件及制备方法,在沟槽栅拐角处集成异质结二极管,改善寄生体二极管的特性,降低开关损耗,提升开关速率,同时保持器件的静态特性不受影响;同时通过淀积较厚的栅氧化层避免沟槽栅底部及拐角处由于电场集中导致的栅氧击穿,器件处于反偏状态时,p型基区之间形成的耗尽区能够降低栅氧化层和si异质结间的电场强度,提升器件可靠性。

技术特征:

1.一种集成异质结二极管的mosfet器件,其特征在于,包括,

2.根据权利要求1所述的集成异质结二极管的mosfet器件,其特征在于:所述氧化层包括第一栅氧化层和第二栅氧化层,所述第一栅氧化层位于所述凸形结构的所述沟槽的两侧壁,所述第二栅氧化层位于所述p-shield层上方隔离所述第一单晶硅,所述第二栅氧化层还位于所述第一单晶硅上方隔离所述第二单晶硅和所述第一单晶硅。

3.根据权利要求1所述的集成异质结二极管的mosfet器件,其特征在于:所述p-shield层的宽度为1μm~3μm,所述p-shield层的厚度为4μm~8μm。

4.根据权利要求3所述的集成异质结二极管的mosfet器件,其特征在于:所述p-shield层底部两端呈圆弧状,所述第一单晶硅底部远离所述氧化层的一端呈圆弧状。

5.根据权利要求1所述的集成异质结二极管的mosfet器件,其特征在于:所述p型基区的注入剂量为5×1014cm2~1.5×1015cm2;所述p型阱区的注入剂量为5×1013cm2~6×1014cm2;所述n型源区的注入剂量为5×1014cm2~1.5×1015cm2;所述p型区的注入剂量为5×1015cm2~1.5×1016cm2。

6.根据权利要求1所述的集成异质结二极管的mosfet器件,其特征在于:还包括漏极金属,所述漏极金属接触所述衬底层背离所述外延层的一侧表面,并与所述衬底层电耦合,所述衬底层设置为碳化硅衬底。

7.一种集成异质结二极管的mosfet器件的制备方法,用于制备如权利要求1~6中任一项所述的集成异质结二极管的mosfet器件,其特征在于,所述制备方法包括以下步骤:

8.根据权利要求7所述的集成异质结二极管的mosfet器件的制备方法,其特征在于:所述第一沟槽的深度均设置为1.7μm~3.8μm。

9.根据权利要求8所述的集成异质结二极管的mosfet器件的制备方法,其特征在于:所述第一单晶硅的厚度为1μm~2μm,所述第一栅氧化层位于所述第一沟槽侧壁和所述第二单晶硅之间,且厚度为0.7μm~1.8μm。

10.根据权利要求7所述的集成异质结二极管的mosfet器件的制备方法,其特征在于:所述第二栅氧化层的厚度为1.5μm~2.5μm。

技术总结

本发明涉及一种集成异质结二极管的MOSFET器件及制备方法,该器件包括自下而上依次设置的衬底层、外延层和电流分散层;还包括凸形结构,所述凸形结构位于电流分散层上端中部,其包括自下而上设置的凸起部和基部,凸起部设置为p‑shield层;基部包括第一单晶硅和第二单晶硅,第一单晶硅在宽度方向上位于p‑shield层的两侧对称设置,且与电流分散层接触;第二单晶硅位于所述凸形结构的顶部,所述第一单晶硅和第二单晶硅之间设置有氧化层;所述电流分散层上还设有P型基区、P型区、P型阱区和N型源区;本发明在沟槽栅拐角处集成异质结二极管,改善寄生体二极管的特性,降低开关损耗,提升开关速率,同时保持器件静态特性不受影响。

技术研发人员:刘辉,傅玥,孔令涛

受保护的技术使用者:南京芯干线科技有限公司

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!