半导体器件的制作方法

本申请涉及半导体,特别是一种半导体器件。

背景技术:

1、氮化镓高电子迁移率晶体管(gan high electron mobility transistor,ganhemt)技术开启了功率转换器的新纪元,实现了前所未有的高工作频率和功率密度。而采用分立式gan器件的功率转换器不可避免的具有较大的寄生参数,在高速开关过程中会导致振荡和电压/电流尖峰,威胁功率系统的安全运行。为了最大限度地减少寄生参数,发挥ganhemt技术在高频应用领域的潜力,氮化镓基单片功率集成电路(gan integrated circuit,gan ic)成为了一个主流的方案。

2、由高边(high side,hs)晶体管和低边(low side,ls)晶体管组成的半桥电路广泛用于功率转换器中,为了最大限度地提高器件性能,通常高边晶体管以及低边晶体管都采用gan hemt,且hs晶体管和ls晶体管的源极都应该电连接到衬底。然而,si基gan单片功率集成电路仅有一个公共导电衬底,因此hs晶体管和ls晶体管的源极都与衬底连接是不实际的,没有源极到衬底短接的晶体管会通过公共衬底遭受串扰或遭受衬偏效应。在现有技术中,例如,ls晶体管中的gan hemt的源极与衬底连接,hs晶体管中的gan hemt的源极连接切换电压,造成hs晶体管中的gan hemt的源极和衬底之间具有压差,而影响hs晶体管的电流,换句话说,hs晶体管中的gan hemt透过公共衬底遭受串扰或衬偏效应,导致整个半桥电路的性能下降。

技术实现思路

1、根据前述,本申请提供一种半导体器件,解决氮化镓高电子迁移率晶体管的串扰或衬偏效应的问题。

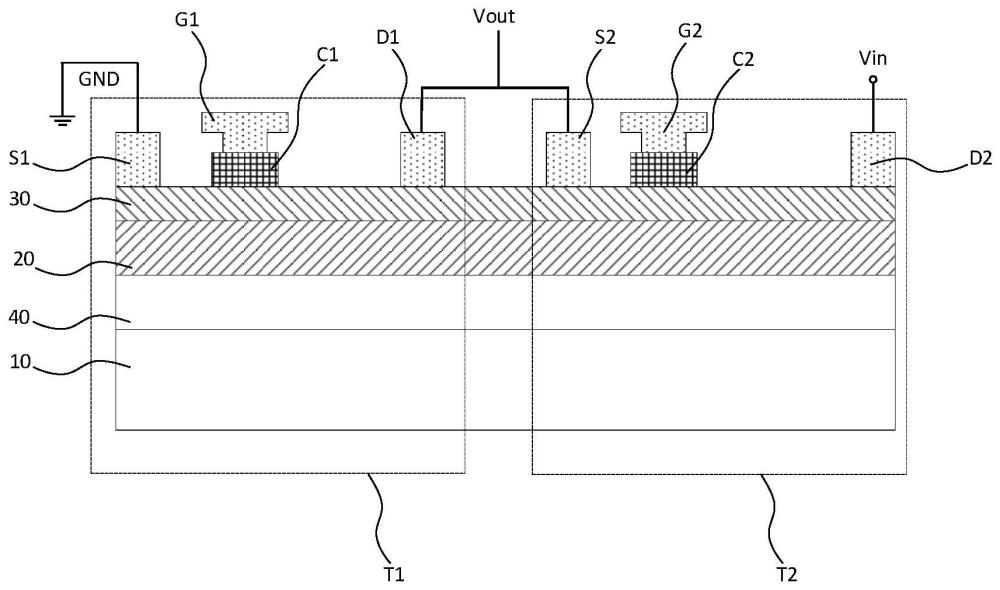

2、基于上述目的,本申请提供一种半导体器件,包括绝缘衬底、沟道层、势垒层、第一栅极、第一源极、第一漏极、第二栅极、第二源极以及第二漏极。绝缘衬底包括第一区域以及第二区域。沟道层设置于绝缘衬底上。势垒层设置于沟道层上。第一栅极设置于第一区域并位于势垒层上。第一源极设置于第一区域的势垒层上,并位于第一栅极的一侧。第一漏极设置于第一区域的势垒层上,并位于第一栅极的另一侧。第二栅极设置于第二区域并位于势垒层上。第二源极设置于第二区域的势垒层上,并位于第二栅极的一侧。第二漏极设置于第二区域的势垒层上,并位于第二栅极的另一侧。沟道层、势垒层、第一栅极、第一源极以及第一漏极形成第一晶体管,沟道层、势垒层、第二栅极、第二源极以及第二漏极形成第二晶体管,绝缘衬底的晶格与沟道层的晶格接近。

3、在本申请的实施例中,绝缘衬底的晶体结构与沟道层的晶体结构都为六方结构。

4、在本申请的实施例中,绝缘衬底与沟道层的晶格失配度小。

5、在本申请的实施例中,绝缘衬底为蓝宝石或高阻的碳化硅或氮化铝或氧化锌。

6、在本申请的实施例中,半导体器件更包括第一帽层以及第二帽层,第一帽层设置于第一栅极和第一区域的势垒层之间,第二帽层设置于第二栅极和第二区域的势垒层之间。

7、在本申请的实施例中,半导体器件更包括缓冲层,缓冲层设置于绝缘衬底与沟道层之间。

8、在本申请的实施例中,半导体器件更包括沟槽以及绝缘层。沟槽设置于第一区域和第二区域之间,并从势垒层延伸至缓冲层,绝缘层设置于沟槽中。

9、在本申请的实施例中,沟槽位于所述第一漏极及所述第二源极之间。

10、在本申请的实施例中,半导体器件更包括介质层,介质层设置于第一帽层和第一源极之间、第一帽层和第一漏极之间、第二帽层和第二源极之间、第二帽层和第二漏极之间以及第二源极和第一漏极之间。

11、在本申请的实施例中,第一源极、第一漏极、第二源极以及第二漏极延伸至沟道层。

12、在本申请的实施例中,半导体器件更包括连接电极,第一漏极与第二源极相邻,连接电极连接第一漏极及第二源极,第一源极连接地电位,第二漏极连接输入电压。

13、在本申请的实施例中,第一晶体管的个数为n个,n个第一晶体管依次并列排布,并共用所述势垒层和缓冲层,每相邻的两个第一晶体管的第一源极或第一漏极共用,n大于等于2,每相邻的两个第一晶体管的两个第一漏极位于对应的第一源极的相对两侧,n个第一栅极的每一个位于对应的第一漏极和第一源极之间。

14、在本申请的实施例中,第二晶体管的个数为n个,n个第二晶体管依次并列排布,并共用势垒层和缓冲层,每相邻的两个第二晶体管的第二漏极或第二源极共用,n大于等于2,每相邻的两个第二晶体管的两个第二源极位于对应的第二漏极的相对两侧,n个第二栅极的每一个位于对应的第二漏极和第二源极之间。

15、在本申请的实施例中,还包括导电结构,以连接相邻的第一晶体管的第一漏极和第二晶体管的第二源极,并作为半导体器件的输出端。

16、综上所述,本申请的半导体器件,基于绝缘衬底的配置,绝缘衬底不会有整体相同的电势,对第一晶体管和第二晶体管开关操作没有影响,另外,无需第一源极和衬底的短接和第二源极和衬底的短接,第一晶体管和第二晶体管也不会受到衬偏效应的影响,也无需特殊设计的衬底,不会增加额外的成本。

17、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,并可依照说明书的内容予以实施,以下以本发明较佳的实施例并配合附图对本发明进行详细说明。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.如权利要求1所述的半导体器件,其特征在于,所述绝缘衬底的晶体结构与所述沟道层的晶体结构都为六方结构。

3.如权利要求1所述的半导体器件,其特征在于,所述绝缘衬底与所述沟道层的晶格失配度小。

4.如权利要求1所述的半导体器件,其特征在于,所述绝缘衬底为蓝宝石或高阻的碳化硅或氮化铝或氧化锌。

5.如权利要求1所述的半导体器件,其特征在于,更包括第一帽层以及第二帽层,所述第一帽层设置于所述第一栅极和所述第一区域的所述势垒层之间,所述第二帽层设置于所述第二栅极和所述第二区域的所述势垒层之间。

6.如权利要求1所述的半导体器件,其特征在于,更包括缓冲层,所述缓冲层设置于所述绝缘衬底与所述沟道层之间。

7.如权利要求6所述的半导体器件,其特征在于,更包括沟槽以及绝缘层,所述沟槽设置于所述第一区域和所述第二区域的之间,并从所述势垒层延伸至所述缓冲层,所述绝缘层设置于所述沟槽中。

8.如权利要求7所述的半导体器件,其特征在于,所述沟槽位于所述第一漏极及所述第二源极之间。

9.如权利要求1所述的半导体器件,其特征在于,更包括介质层,所述介质层设置于所述第一帽层和所述第一源极之间、所述第一帽层和所述第一漏极之间、所述第二帽层和所述第二源极之间、所述第二帽层和所述第二漏极之间以及所述第二源极和所述第一漏极之间。

10.如权利要求1所述的半导体器件,其特征在于,所述第一源极、所述第一漏极、所述第二源极以及所述第二漏极延伸至所述沟道层。

11.如权利要求1所述的半导体器件,其特征在于,更包括连接电极,所述第一漏极与所述第二源极相邻,所述连接电极连接所述第一漏极及所述第二源极,所述第一源极连接地电位,所述第二漏极连接输入电压。

12.如权利要求6所述的半导体器件,其特征在于,所述第一晶体管的个数为n个,所述n个第一晶体管依次并列排布,并共用所述势垒层和所述缓冲层,每相邻的所述两个第一晶体管的所述第一源极或所述第一漏极共用,n大于等于2,每相邻的所述两个第一晶体管的所述两个第一漏极位于对应的所述第一源极的相对两侧,所述n个第一栅极的每一个位于对应的所述第一漏极和所述第一源极之间。

13.如权利要求12所述的半导体器件,其特征在于,所述第二晶体管的个数为n个,所述n个第二晶体管依次并列排布,并共用所述势垒层和缓冲层,每相邻的所述两个第二晶体管的所述第二漏极或所述第二源极共用,n大于等于2,每相邻的所述两个第二晶体管的所述两个第二源极位于对应的所述第二漏极的相对两侧,所述n个第二栅极的每一个位于对应的所述第二漏极和所述第二源极之间。

14.根据权利要求13所述的半导体器件,其特征在于,还包括导电结构,以连接相邻的所述第一晶体管的所述第一漏极和所述第二晶体管的所述第二源极,并作为所述半导体器件的输出端。

技术总结

本申请提供一种半导体器件,括绝缘衬底、沟道层、势垒层、第一栅极、第一源极、第一漏极、第二栅极、第二源极以及第二漏极。沟道层、势垒层、第一栅极、第一源极以及第一漏极形成第一晶体管,沟道层、势垒层、第二栅极、第二源极以及第二漏极形成第二晶体管,第一晶体管和第二晶体管设置于绝缘衬底上。透过绝缘衬底的配置,抑制第一晶体管和第二晶体管之间的串扰,使第一晶体管和第二晶体管不会受到衬偏效应的影响,而无需第一源极和衬底的短接和第二源极和衬底的短接。

技术研发人员:张力,黄秋凯,赵晨

受保护的技术使用者:矽力杰半导体技术(杭州)有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!