抗单粒子辐射SiCUMOSFET器件结构及其制造

本发明涉及场效应晶体管器件领域,尤其涉及一种具有埋层超结al2o3栅介质的抗单粒子辐射sic umosfet器件结构及其制造方法。

背景技术:

1、sic具有优越的物理和化学性质,例如高临界击穿场强、高热导率、宽禁带、高电子饱和漂移速度,因而非常适合应用于高压、高温电力电子领域。在空间领域,sic功率器件应用于卫星、民用飞船等,所以在空间也有广泛的应用前景。

2、然而,在空间的辐射环境下,电离辐射的高能量会使器件产生不稳定状态,甚至损坏失效,破坏力最强的是空间中高能量的单粒子,其中场效应晶体管(mosfet)器件对单粒子入射尤其敏感,容易造成单粒子烧毁(seb),在栅极入射容易造成单粒子栅破裂(segr)。

技术实现思路

1、本发明的目的在于解决现有技术中的上述问题,提供一种具有埋层超结al2o3栅介质的抗单粒子辐射sic沟槽(u)mosfet器件结构及其制造方法,由于埋层的引入,有效降低了单粒子入射后沟槽氧化物中的电场,al2o3的高介电常数和厚度的增加,有效降低了单粒子入射后的栅极氧化物的峰值电场。

2、为达到上述目的,本发明采用如下技术方案:

3、所述抗单粒子辐射sic umosfet器件结构,包括漂移层(3)、部分传输层(10)、p型埋层(11)、上方传输层区域(12)、p型基区层(13);

4、所述漂移层(3)、部分传输层(10)、p型埋层(11)、上方传输层区域(12)、p型基区层(13)自下而上依次生长而成;所述p型基区层(13)上形成有n+源区(14)和p+源区(15),穿过所述n+源区(14)、p型基区层(13)并进入上方传输层区域(12)内形成主沟槽(19),在主沟槽(19)底部形成有p屏蔽层(16);在p屏蔽层(16)上形成有栅介质al2o3(4)。

5、所述p型埋层(11)设有若干,且等间距排列。

6、所述p屏蔽层(16)底部距离p型埋层(11)顶部0.2~0.6μm。

7、所述p型埋层(11)的厚度为1~3μm。

8、所述部分传输层(10)的厚度为2~3μm,上方传输层区域(12)的厚度为1~2μm。

9、所述栅介质al2o3(4)的厚度为40~100nm。

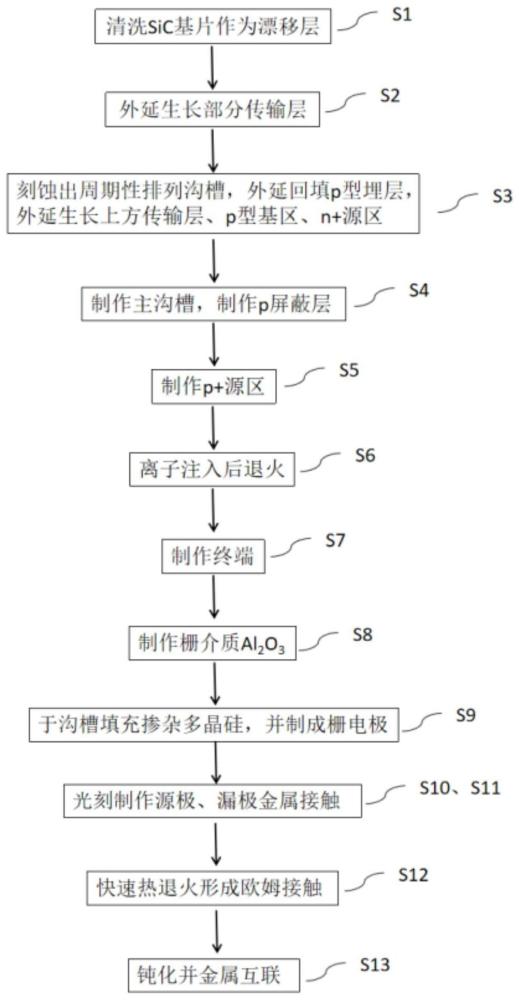

10、所述的抗单粒子辐射sic umosfet器件结构的制备方法,包括以下步骤:

11、1)在漂移层(3)上外延生长部分传输层(10),在部分传输层(10)中用icp刻蚀出周期性排列沟槽并通过外延回填形成若干个等间距p型埋层(11),再通过外延生长得到上方传输层区域(12),在上方传输层区域(12)的表面外延生长p型基区层(13),其中p型埋层(11)在单粒子入射情况下有效保护沟槽氧化物中的电场且在反向高电压下有阻挡作用;

12、2)在所述p型基区层(13)上形成n+源区(14)和p+源区(15),在所述n+源区(14)、p型基区层(13)和上方传输层区域(12)内形成主沟槽(19),以及在主沟槽底部形成p屏蔽层(16);在所述p屏蔽层(16)上利用物理或化学气相法生长形成栅介质al2o3(4),其中栅介质al2o3在单粒子入射过程中有效降低栅氧电场峰值。

13、相对于现有技术,本发明技术方案取得的有益效果是:

14、1、相比于传统的sic基沟槽mosfet,本发明采用p型埋层,将传统器件的阈值let由0.1pc/μm提升到了0.15pc/μm。

15、2、所述的sic umosfet,相比于传统的sic基沟槽mosfet,由于传输层的存在,比导通电阻降低,具有更好的静态特性。

16、3、在不影响阈值电压的前提下,al2o3栅介质有效提高了栅介质的物理厚度,可以有效降低单粒子入射后的栅极氧化物电场峰值。

技术特征:

1.抗单粒子辐射sic umosfet器件结构,其特征在于:包括漂移层(3)、部分传输层(10)、p型埋层(11)、上方传输层区域(12)、p型基区层(13);

2.如权利要求1所述的抗单粒子辐射sic umosfet器件结构,其特征在于:p型埋层(11)设有若干,且等间距排列。

3.如权利要求1所述的抗单粒子辐射sic umosfet器件结构,其特征在于:p屏蔽层(16)底部距离p型埋层(11)顶部0.2~0.6μm。

4.如权利要求1所述的抗单粒子辐射sic umosfet器件结构,其特征在于:p型埋层(11)的厚度为1~3μm。

5.如权利要求1所述的抗单粒子辐射sic umosfet器件结构,其特征在于:部分传输层(10)的厚度为2~3μm,上方传输层区域(12)的厚度为1~2μm。

6.如权利要求1所述的抗单粒子辐射sic umosfet器件结构,其特征在于:所述栅介质al2o3(4)的厚度为40~100nm。

7.权利要求1~6任一项所述的抗单粒子辐射sic umosfet器件结构的制造,其特征在于,包括以下步骤:

技术总结

抗单粒子辐射SiC UMOSFET器件结构及其制造,在SiC衬底上生长漂移层和部分传输层,在传输层中用ICP刻蚀出周期性排列沟槽并通过外延回填形成四个等间距p型埋层,再通过多外延生长得到埋层上方传输层区域,在传输层表面外延生长p型基区层,通过高能离子注入形成n+源区和p+源区,然后采用ICP刻蚀栅极沟槽,在沟槽底部通过多次高能离子注入形成p屏蔽层,表面上利用物理或化学气相法生长形成栅介质Al<subgt;2</subgt;O<subgt;3</subgt;。由于p型埋层的存在,提高了器件抗单粒子烧毁能力,由于Al<subgt;2</subgt;O<subgt;3</subgt;介电常数大于传统的栅氧化物SiO<subgt;2</subgt;,单粒子轰击过程中有效降低栅极氧化物电场峰值,提高了器件抗单粒子栅穿能力。

技术研发人员:张峰,缪宇扬,王小杰

受保护的技术使用者:厦门大学

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!