一种半导体器件及其制备方法与流程

本发明实施例涉及半导体,尤其涉及一种半导体器件及其制备方法。

背景技术:

1、氮化物基半导体器件利用具有不同带隙的两种材料之间的异质结界面来形成量子阱类结构,所述量子阱类结构容纳二维电子气体区,从而满足高功率/频率器件的需求。

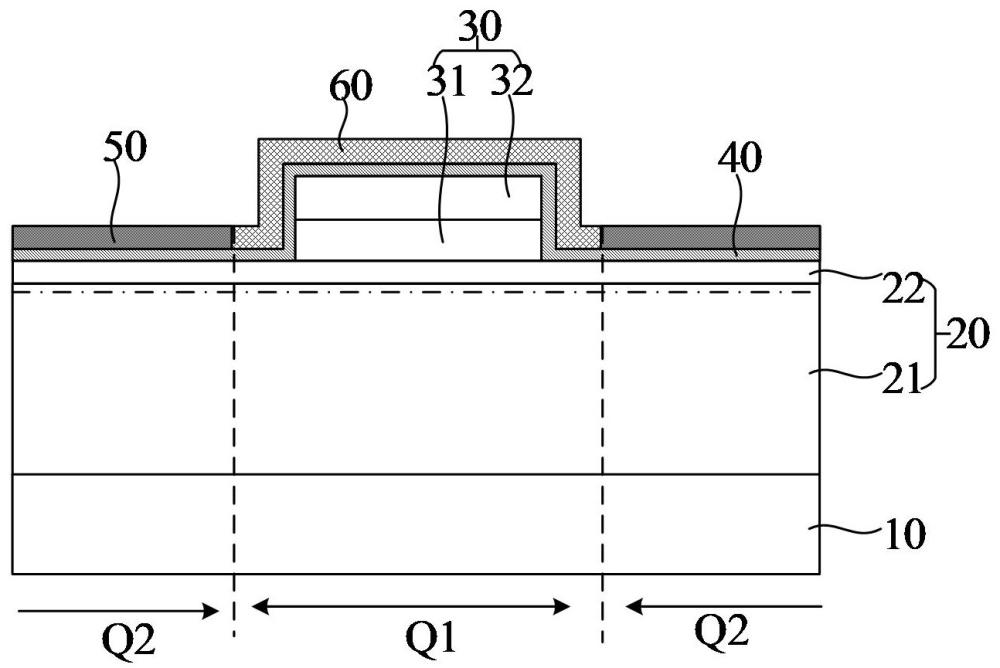

2、尽管如此,依然有一些可靠性问题值得关注。图1是现有技术中提供的一种半导体器件的剖面结构示意图,参考图1,半导体器件包括带隙不同的第一氮化物半导体层1和第二氮化物半导体层2,第二氮化物半导体层2上设置有栅极结构4,以及覆盖在栅极结构的表面和第二氮化物半导体层2表面的sin 钝化层3。sin 钝化层3中的si含量会影响半导体器件的性能。如果sin 中si的含量偏高,si向栅极结构4扩散,会在栅极结构4的侧壁区域形成栅极泄露;如果sin 中si的含量偏低,si不能有效的向下扩散,从而无法有效增加2deg(twodimensional electron gas,二维电子气体)浓度。因此如何有效增加2deg 的浓度,以减少导通电阻,提高器件工作效率的同时,降低栅极泄露的概率,成为本领域人员亟待解决的技术问题。

技术实现思路

1、本发明实施例提供了一种半导体器件及其制备方法,以有效提高2deg浓度,减少导通电阻,提高器件工作效率的同时,降低栅极泄露的概率。

2、根据本发明的一方面,提供了一种半导体器件,包括:

3、衬底;

4、半导体外延层,位于所述衬底的一侧;其中,所述半导体外延层内具有二维电子气的异质结;所述半导体外延层包括栅极区以及位于所述栅极区相对两侧的漂移区;

5、栅极结构,位于所述半导体外延层的栅极区;

6、间隔层,位于所述半导体外延层的漂移区;

7、硅元素供给层,位于所述间隔层远离所述衬底的一侧;

8、阻挡层,位于所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁;所述阻挡层用于阻挡所述硅元素供给层中的硅向所述栅极结构扩散。

9、可选的,所述硅元素供给层在所述半导体外延层上的垂直投影位于所述半导体外延层的漂移区;

10、且所述硅元素供给层在所述半导体外延层上的垂直投影的面积小于或等于所述间隔层在所述半导体外延层上的垂直投影的面积。

11、可选的,所述间隔层还位于所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁;

12、且位于所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁的间隔层在所述阻挡层与所述栅极结构之间。

13、可选的,所述阻挡层的材料包括氧化硅;所述硅元素供给层的材料为硅。

14、可选的,所述间隔层的材料包括氮化硅;且所述间隔层的材料中硅含量的范围为20%~40%。

15、可选的,所述半导体器件还包括:

16、应变层,位于所述间隔层和所述半导体外延层之间,以及所述间隔层和所述栅极结构之间;并且,所述应变层覆盖所述半导体外延层的表面以及所述栅极结构的表面;其中,所述应变层的材料包括氮化铝。

17、可选的,所述半导体器件还包括源极电极和漏极电极,位于所述半导体外延层远离所述衬底的一侧;且所述源极电极和所述漏极电极位于所述栅极结构的相对两侧;

18、其中,所述硅元素供给层位于所述栅极结构与所述漏极电极之间以及所述栅极结构与所述源极电极之间。

19、根据本发明的另一方面,提供了一种半导体器件的制备方法,包括:

20、提供衬底;

21、在所述衬底的一侧形成半导体外延层;其中,所述半导体外延层内具有二维电子气的异质结;所述半导体外延层包括栅极区以及位于所述栅极区相对两侧的漂移区;

22、于所述半导体外延层的栅极区形成栅极结构;

23、于所述半导体外延层的漂移区形成间隔层;

24、在所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁形成阻挡层;

25、在所述间隔层远离所述衬底的一侧形成硅元素供给层;其中,所述阻挡层用于阻挡所述硅元素供给层中的硅向所述栅极结构扩散。

26、可选的,于所述半导体外延层的漂移区形成间隔层时,还包括:

27、于所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁形成间隔层;

28、在所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁形成阻挡层,包括:

29、在所述间隔层远离所述衬底一侧的表面沉积氧化硅材料形成所述阻挡层,并刻蚀掉位于所述漂移区的阻挡层,暴露出所述间隔层;

30、在所述间隔层远离所述衬底的一侧形成硅元素供给层,包括:

31、在所述阻挡层远离所述衬底一侧的表面以及暴露出的所述间隔层的表面沉积硅材料形成硅元素供给层,并刻蚀掉位于所述阻挡层远离所述衬底一侧的硅元素供给层。

32、可选的,于所述半导体外延层的栅极区形成栅极结构之后,还包括:

33、于所述半导体外延层的表面以及所述栅极结构的表面形成应变层;其中,所述应变层的材料包括氮化铝;所述间隔层位于所述应变层远离所述衬底的一侧。

34、有益效果:本发明实施例提供了一种半导体器件及其制备方法,其中半导体器件包括:衬底;半导体外延层,位于衬底的一侧;其中,半导体外延层内具有二维电子气的异质结;半导体外延层包括栅极区以及位于栅极区相对两侧的漂移区;栅极结构,位于半导体外延层的栅极区;间隔层,位于半导体外延层的漂移区;硅元素供给层,位于间隔层远离衬底的一侧;阻挡层,位于栅极结构远离衬底的一侧以及栅极结构的侧壁;阻挡层用于阻挡硅元素供给层中的硅向栅极结构扩散。本发明实施例提供的技术方案,将硅元素供给层和阻挡层分开设置,通过含硅元素高的硅元素供给层可以向漂移区的半导体外延层提供硅,从而有效的提高2deg浓度,减少导通电阻,提高器件工作效率;通过对硅阻挡性好的阻挡层包裹住栅极结构的侧壁和上表面,防止阻挡硅元素供给层中的硅向栅极结构扩散,从而可以有效的降低栅极泄露的概率。

35、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,

3.根据权利要求1所述的半导体器件,其特征在于,所述间隔层还位于所述栅极结构远离所述衬底的一侧以及栅极结构的侧壁;

4.根据权利要求1所述的半导体器件,其特征在于,所述阻挡层的材料包括氧化硅;所述硅元素供给层的材料为硅。

5.根据权利要求1所述的半导体器件,其特征在于,所述间隔层的材料包括氮化硅;且所述间隔层的材料中硅含量的范围为20%~40%。

6.根据权利要求3所述的半导体器件,其特征在于,还包括:

7.根据权利要求1~6任一所述的半导体器件,其特征在于,还包括源极电极和漏极电极,位于所述半导体外延层远离所述衬底的一侧;且所述源极电极和所述漏极电极位于所述栅极结构的相对两侧;

8.一种半导体器件的制备方法,其特征在于,包括:

9.根据权利要求8所述的半导体器件的制备方法,其特征在于,于所述半导体外延层的漂移区形成间隔层时,还包括:

10.根据权利要求9所述的半导体器件的制备方法,其特征在于,于所述半导体外延层的栅极区形成栅极结构之后,还包括:

技术总结

本发明公开了一种半导体器件及其制备方法,半导体器件包括:衬底;半导体外延层,位于衬底的一侧;其中,半导体外延层内具有二维电子气的异质结;半导体外延层包括栅极区以及位于栅极区相对两侧的漂移区;栅极结构,位于半导体外延层的栅极区;间隔层,位于半导体外延层的漂移区;硅元素供给层,位于间隔层远离衬底的一侧;阻挡层,位于栅极结构远离衬底的一侧以及栅极结构的侧壁;阻挡层用于阻挡硅元素供给层中的硅向栅极结构扩散。本发明提供的技术方案,有效的提高了2DEG浓度,减少导通电阻,提高器件工作效率的同时,降低了栅极泄露的概率。

技术研发人员:刘成名,高钒,徐畅,王安,余仁旭,何有丰

受保护的技术使用者:英诺赛科(苏州)半导体有限公司

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!