半导体制造方法及半导体结构与流程

本发明属于半导体制造,尤其涉及一种半导体制造方法及半导体结构。

背景技术:

1、自“摩尔定律”提出以来,微电子器件密度几乎沿着“摩尔定律”的预言发展。为了提高电路密度,微电子制造已由二维向三维发展。方法之一是将芯片堆叠以后进行封装,由此产生了三维电路封装技术(3d ic packaging)。三维电路封装技术中,要实现硅芯片上下层之间的连接,需要使用互联结构。

2、随着半导体制造技术的发展,由于传统的铝金属互连材料本身的性质,现已逐渐被低电阻率以及高抗电迁移性的金属铜取代。然而随着技术节点的演变,互联结构的尺寸越来越小,互连结构中铜的均匀填充成为目前制造过程中的另一挑战。目前普遍采用的铜互连工艺首先是利用物理气相沉积(pvd)生长铜阻挡层和种子层,随后利用电化学电镀(ecp)进行铜的填充。而随着互连尺寸的减小,沉积形成的种子层可能会在互连结构开口处形成突起,这将使得凹槽顶部的工艺窗口减小,会造成ecp完成后在铜互连结构中形成空洞。

3、目前改善上述问题带来的铜空洞缺陷的方法主要是通过沉积更薄的阻挡层和种子层来增大后续ecp的工艺窗口,然而该方法不能够适应于当前半导体制造技术的不断演变,因此需要寻求其他能够减少铜电镀时造成的空洞问题的解决方案。

技术实现思路

1、针对相关技术中存在的至少一个不足之处,本申请提供了一种半导体制造方法及半导体结构,可以实现互连结构中少空洞或无空洞地填充。

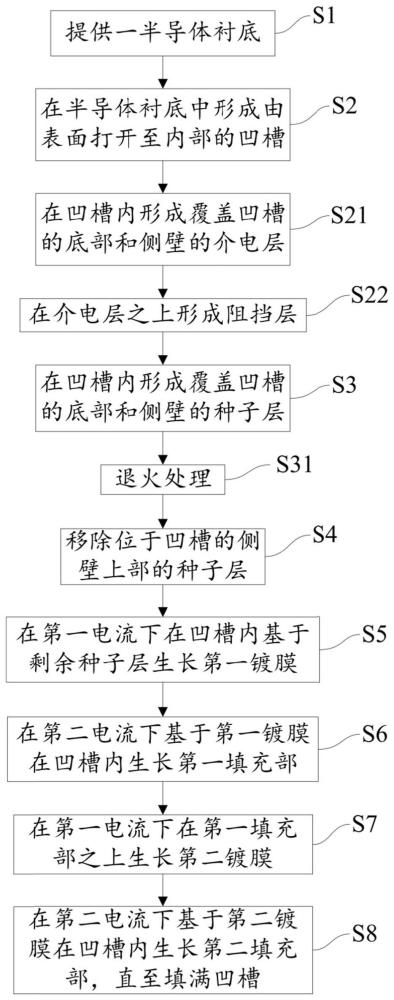

2、本申请第一方面提供一种半导体制造方法,包括以下步骤:

3、提供一半导体衬底;

4、在半导体衬底中形成由表面打开至内部的凹槽;

5、在凹槽内形成覆盖凹槽的底部和侧壁的种子层;

6、移除位于凹槽的侧壁上部的种子层;

7、在第一电流下在凹槽内基于剩余种子层生长第一镀膜;

8、在第二电流下基于第一镀膜在凹槽内生长第一填充部;

9、在第一电流下在第一填充部之上生长第二镀膜;

10、在第二电流下基于第二镀膜在凹槽内生长第二填充部,直至填满凹槽。

11、在第一方面的一些实施例中,采用离子束刻蚀方法将凹槽的侧壁上部的种子层移除,刻蚀速率为刻蚀气体为氩气,刻蚀能量为1~3kev。

12、在第一方面的一些实施例中,移除位于凹槽的侧壁上部的种子层后,剩余种子层的高度占凹槽深度的60%~70%。

13、在第一方面的一些实施例中,在形成种子层之后,还包括退火处理的步骤,退火处理的温度为180~200℃,退火处理的时间为100~180s。

14、在第一方面的一些实施例中,第一电流的值为3~5a,在第一电流下进行电镀的时间为5.5~30s。

15、在第一方面的一些实施例中,第二电流的值为10~20a,在第二电流下进行电镀的时间为60~120s。

16、在第一方面的一些实施例中,在形成种子层之前,还包括:在凹槽内形成覆盖凹槽的底部和侧壁的介电层。

17、在第一方面的一些实施例中,在形成种子层之前,还包括:在介电层之上形成阻挡层。

18、本申请第二方面提供一种根据第一方面任一项所述的半导体制造方法制造而成的半导体结构。

19、在第二方面的一些实施例中,该半导体结构包括:

20、半导体衬底,在半导体衬底中形成有由表面打开至内部的凹槽;

21、种子层,其覆盖凹槽的底部和侧壁的下部;

22、第一填充部,其填充于凹槽的下部;

23、第二填充部,其位于第一填充部之上且与第一填充部共同填满凹槽。

24、与现有技术相比,本申请的优点和积极效果在于:

25、(1)本申请至少一个实施例所提供的半导体制造方法,将凹槽内种子层的上部分移除,同时种子层在开口处所形成的突起也被移除,扩大了凹槽顶部的工艺窗口,在利用电化学电镀工艺进行填洞的过程中分为两个阶段分别进行,有利于实现自下向上的填充,从而使得填充后的互连结构中几乎没有空洞等缺陷;

26、(2)本申请至少一个实施例所提供的半导体制造方法,通过离子束轰击的方法将位于凹槽内部上方的种子层去除,能够精准控制刻蚀的方向和刻蚀的深度,避免对附近其它结构造成刻蚀破坏;

27、(3)本申请至少一个实施例所提供的半导体制造方法,在填充过程中,首先在第一电流下生长一镀膜,然后将电流增加至第二电流进行填充,且分两个阶段分别进行,可以更充分地进行填充,实现对凹槽自下向上的填充,避免空洞等缺陷发生,提高填充质量;

28、(4)本申请至少一个实施例所提供的半导体结构,在凹槽中分两个阶段分别进行电镀生长,第一填充部和第二填充部共同填满凹槽,在填充后的空洞缺陷较少或基本不会发生,具有较好的互连电性。

技术特征:

1.一种半导体制造方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的半导体制造方法,其特征在于,采用离子束刻蚀方法将所述凹槽的侧壁上部的所述种子层移除,刻蚀速率为刻蚀气体为氩气,刻蚀能量为1~3kev。

3.根据权利要求1所述的半导体制造方法,其特征在于,移除位于所述凹槽的侧壁上部的所述种子层后,剩余种子层的高度占所述凹槽深度的60%~70%。

4.根据权利要求1所述的半导体制造方法,其特征在于,在形成所述种子层之后,还包括退火处理的步骤,所述退火处理的温度为180~200℃,所述退火处理的时间为100~180s。

5.根据权利要求1所述的半导体制造方法,其特征在于,所述第一电流的值为3~5a,在所述第一电流下进行电镀的时间为5.5~30s。

6.根据权利要求5所述的半导体制造方法,其特征在于,所述第二电流的值为10~20a,在所述第二电流下进行电镀的时间为60~120s。

7.根据权利要求1所述的半导体制造方法,其特征在于,在形成所述种子层之前,还包括:在所述凹槽内形成覆盖所述凹槽的底部和侧壁的介电层。

8.根据权利要求7所述的半导体制造方法,其特征在于,在形成所述种子层之前,还包括:在所述介电层之上形成阻挡层。

9.一种根据权利要求1-9任一项所述的半导体制造方法制造而成的半导体结构。

10.根据权利要求9所述的半导体结构,其特征在于,包括:

技术总结

本发明涉及一种半导体制造方法及半导体结构,其中,半导体制造方法包括:提供一半导体衬底;在半导体衬底中形成由表面打开至内部的凹槽;在凹槽内形成覆盖凹槽的底部和侧壁的种子层;移除位于凹槽的侧壁上部的种子层;在第一电流下在凹槽内基于剩余种子层生长第一镀膜;在第二电流下基于第一镀膜在凹槽内生长第一填充部;在第一电流下在第一填充部之上生长第二镀膜;在第二电流下基于第二镀膜在凹槽内生长第二填充部,直至填满凹槽。该方法可以实现互连结构中少空洞或无空洞地填充,提高互连结构的电性能。

技术研发人员:华逢钊,黄耀贤,郝广信,王全,王燕琳

受保护的技术使用者:物元半导体技术(青岛)有限公司

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!