一种ESD器件结构的制作方法

本技术属于esd器件,尤其涉及一种esd器件结构。

背景技术:

1、为了应对常规静电放电对芯片的损伤,在常规设计时候每个输入输出端都必须配备esd保护器件,常规的esd保护器件比如ggnmos(栅极接地的nmos器件)或者diode(二极管)结构方案,都会存在一个gnd端对i/o管脚端的寄生二极管,当i/o管脚端出现比二极管导通压降大的负值电压,该二极管就会开启,产生一个gnd到i/o管脚端的大电流,导致该i/o管脚端功能失效,所以常规esd结构不适用于i/o管脚端有负电压的情况。

技术实现思路

1、本实用新型目的在于提供一种esd器件结构,以解决现有esd器件如ggnmos或者diode结构,当i/o管脚端出现比二极管导通压降大的负值电压时,该二极管就会开启,产生一个gnd到i/o管脚端的大电流,导致该i/o管脚端功能失效的技术问题。

2、为实现上述目的,本实用新型的esd器件结构的具体技术方案如下:

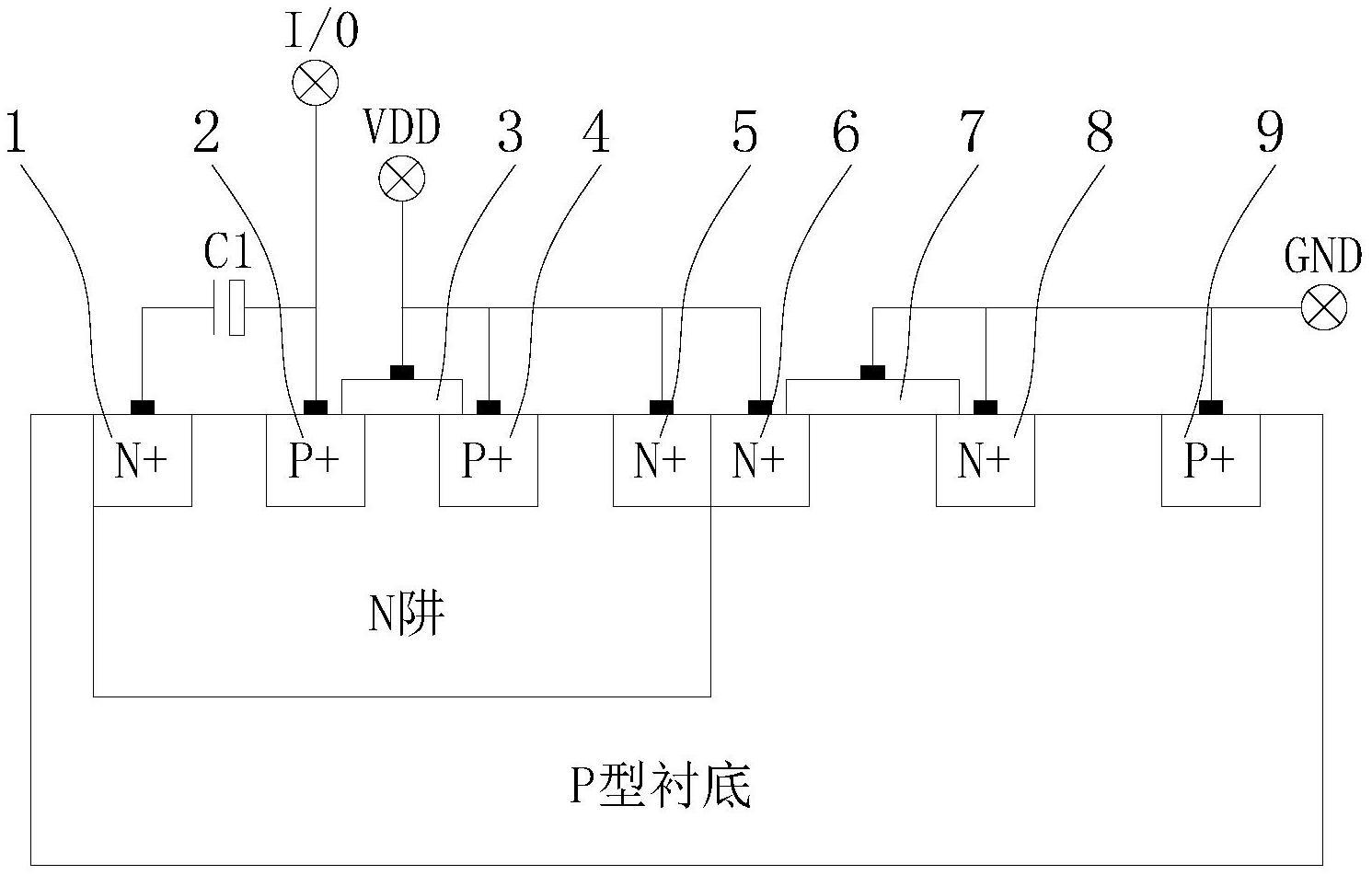

3、一种esd器件结构,包括p型衬底,所述p型衬底上设置有第三n+区、第四n+区、第三p+区和第二栅极;所述p型衬底上还设置有n阱区,所述n阱区上设置有第一n+区、第一p+区、第二p+区、第二n+区和第一栅极;所述第一p+区连接i/o端,所述第一n+区通过电容c1连接i/o端,所述第一栅极、所述第二p+区、所述第二n+区和所述第三n+区连接vdd端,所述第二栅极、所述第四n+区和所述第三p+区连接gnd端。

4、优选的,所述电容c1的时间参数为纳秒级别。

5、优选的,所述第三n+区紧邻所述n阱区设置。

6、本实用新型的esd器件结构具有以下优点:当i/o端出现负电压时,i/o端与vdd端之间有反偏寄生二极管,该二极管截止,同时i/o端还连接pmos的源极,该pmos的漏极和栅极接vdd端,源极接负电压,该pmos也处于截止状态,使该i/o端可耐负电压,进而实现了esd器件的耐负电压功能。

技术特征:

1.一种esd器件结构,其特征在于:

2.根据权利要求1所述的esd器件结构,其特征在于,所述电容c1的时间参数为纳秒级别。

3.根据权利要求1所述的esd器件结构,其特征在于,所述第三n+区(6)紧邻所述n阱区设置。

技术总结

本技术公开了一种ESD器件结构,包括P型衬底,P型衬底上设置有第三N+区、第四N+区、第三P+区和第二栅极;P型衬底上还设置有N阱区,N阱区上设置有第一N+区、第一P+区、第二P+区、第二N+区和第一栅极;第一P+区连接I/O端,第一N+区通过电容C1连接I/O端,第一栅极、第二P+区、第二N+区和第三N+区连接VDD端,第二栅极、第四N+区和第三P+区连接GND端。当I/O端出现负电压时,I/O端与VDD端之间有反偏寄生二极管,该二极管截止,同时I/O端还连接PMOS的源极,该PMOS的漏极和栅极接VDD端,源极接负电压,该PMOS也处于截止状态,使该I/O端可耐负电压,实现了ESD器件的耐负电压功能。

技术研发人员:柴伟忠

受保护的技术使用者:无锡华众芯微电子有限公司

技术研发日:20230110

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!