一种多芯片大容量高集成封装结构的制作方法

本技术涉及一种多芯片大容量高集成封装结构,属于半导体封装。

背景技术:

1、目前市面上行业普遍采用常规的控制芯片封装中,大多元件通过金线键合跟基板导通,同时搭配存储芯片进行封装;但存储芯片未同时兼顾dram和nand flash混合封装,从而导致产品io接口数量有限,电性能较差,散热性不好,无法满足高速大容量需求;而随着5g手机的发展将从高端机向低端机不断渗透,快速实现全面普及,同样是对大容量高性能的芯片封装提出更高的要求。

技术实现思路

1、本实用新型目的是为了克服现有技术的不足而提供一种多芯片大容量高集成封装结构。

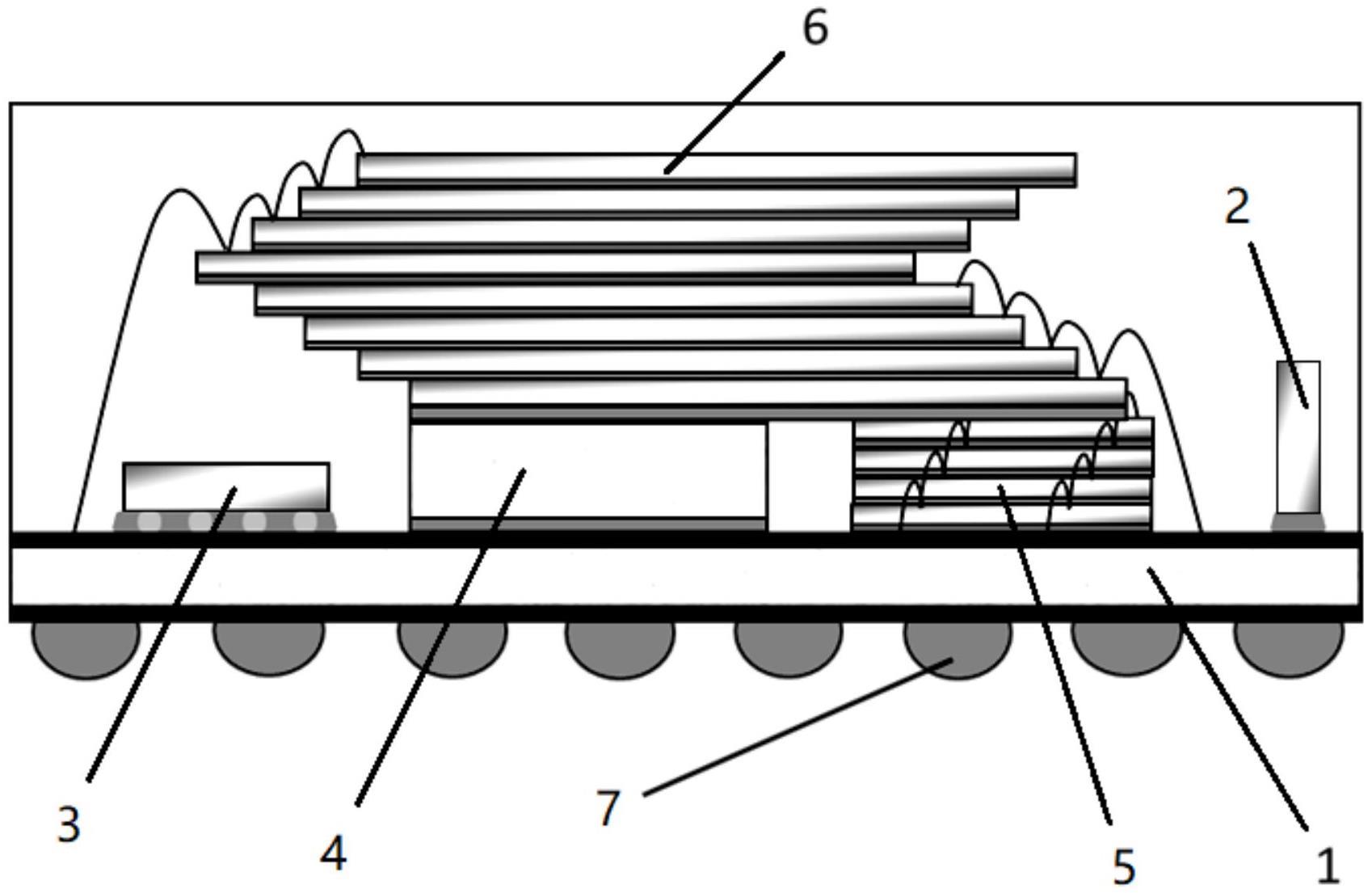

2、为达到上述目的,本实用新型采用的技术方案是:一种多芯片大容量高集成封装结构,包含基板、元器件、控制器、垫片、内存芯片和闪存芯片;所述元器件焊接在基板上,控制器通过底部填胶倒装在基板上,垫片通过daf胶膜贴合在基板上;所述的内存芯片有多层,多层内存芯片通过daf胶膜依次阶梯堆叠在基板上,最上层的内存芯片的顶面与垫片的顶面齐平;所述的闪存芯片有多层,多层闪存芯片通过daf胶膜依次阶梯堆叠在垫片和最上层的内存芯片上。

3、优选的,所述的内存芯片堆叠四层,四层内存芯片依次通过键合线电连接,最下层的内存芯片通过键合线与基板导通。

4、优选的,所述的多层闪存芯片分为第一闪存阶梯堆叠组和第二闪存阶梯堆叠组,第一闪存阶梯堆叠组设置在垫片和最上层的内存芯片上,第二闪存阶梯堆叠组设置在第一闪存阶梯堆叠组上,第一闪存阶梯堆叠组与第二闪存阶梯堆叠组的堆叠方向相反。

5、优选的,所述的第一闪存阶梯堆叠组和第二闪存阶梯堆叠组各包含四层闪存芯片;第一闪存阶梯堆叠组的四层闪存芯片通过键合线依次电连接,第一闪存阶梯堆叠组最下层的闪存芯片通过键合线与基板导通;第二闪存阶梯堆叠组的四层闪存芯片通过键合线依次电连接,第二闪存阶梯堆叠组最下层的闪存芯片通过键合线与基板导通。

6、由于上述技术方案的运用,本实用新型与现有技术相比具有下列优点:

7、本实用新型方案的多芯片大容量高集成封装结构,将多颗内存芯片堆叠在基板上,并在基板上设置与多颗内存芯片等高的垫片,使多层闪存芯片可以直接堆叠在垫片和内存芯片上,以此减少存储芯片的占用并实现更灵活的系统设计,可以最大限度的实现多芯片,大容量,低功耗,高集成的封装模式。

技术特征:

1.一种多芯片大容量高集成封装结构,其特征在于:包含基板(1)、元器件(2)、控制器(3)、垫片(4)、内存芯片(5)和闪存芯片(6);所述元器件(2)焊接在基板(1)上,控制器(3)通过底部填胶倒装在基板(1)上,垫片(4)通过daf胶膜贴合在基板(1)上;所述的内存芯片(5)有多层,多层内存芯片(5)通过daf胶膜依次阶梯堆叠在基板(1)上,最上层的内存芯片(5)的顶面与垫片(4)的顶面齐平;所述的闪存芯片(6)有多层,多层闪存芯片(6)通过daf胶膜依次阶梯堆叠在垫片(4)和最上层的内存芯片(5)上。

2.根据权利要求1所述的多芯片大容量高集成封装结构,其特征在于:所述的内存芯片(5)堆叠四层,四层内存芯片(5)依次通过键合线电连接,最下层的内存芯片(5)通过键合线与基板(1)导通。

3.根据权利要求1所述的多芯片大容量高集成封装结构,其特征在于:所述的多层闪存芯片(6)分为第一闪存阶梯堆叠组和第二闪存阶梯堆叠组,第一闪存阶梯堆叠组设置在垫片(4)和最上层的内存芯片(5)上,第二闪存阶梯堆叠组设置在第一闪存阶梯堆叠组上,第一闪存阶梯堆叠组与第二闪存阶梯堆叠组的堆叠方向相反。

4.根据权利要求3所述的多芯片大容量高集成封装结构,其特征在于:所述的第一闪存阶梯堆叠组和第二闪存阶梯堆叠组各包含四层闪存芯片(6);第一闪存阶梯堆叠组的四层闪存芯片(6)通过键合线依次电连接,第一闪存阶梯堆叠组最下层的闪存芯片(6)通过键合线与基板(1)导通;第二闪存阶梯堆叠组的四层闪存芯片(6)通过键合线依次电连接,第二闪存阶梯堆叠组最下层的闪存芯片(6)通过键合线与基板(1)导通。

技术总结

本技术涉及一种多芯片大容量高集成封装结构,包含基板、元器件、控制器、垫片、内存芯片和闪存芯片;元器件焊接在基板上,控制器通过底部填胶倒装在基板上,垫片通过DAF胶膜贴合在基板上;内存芯片有多层,多层内存芯片通过DAF胶膜依次阶梯堆叠在基板上,最上层的内存芯片的顶面与垫片的顶面齐平;闪存芯片有多层,多层闪存芯片通过DAF胶膜依次阶梯堆叠在垫片和最上层的内存芯片上;本方案将多颗内存芯片堆叠在基板上,并在基板上设置与多颗内存芯片等高的垫片,使多层闪存芯片可以直接堆叠在垫片和内存芯片上,以此减少存储芯片的占用并实现更灵活的系统设计,可以最大限度的实现多芯片,大容量,低功耗,高集成的封装模式。

技术研发人员:韩磊磊,张军军,华毅

受保护的技术使用者:太极半导体(苏州)有限公司

技术研发日:20230109

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!