半导体封装装置的制作方法

本申请涉及半导体封装,具体涉及一种半导体封装装置。

背景技术:

1、pop(package on package,内埋式堆叠封装)结构是将复数个package(封装)堆叠起来,其中,各个package内有一个至多个芯片(die)设置于基板(substrate,sbt)上,各个package之间通过锡球连接,借此方式整合成高密度的电子组件封装件。

2、参考图1,示出了目前的一种pop结构的半导体封装装置,包括第二封装结构12和堆叠于其上的第一封装结构11,第一封装结构11和第二封装结构12通过锡球13实现电性连接和物理连接,且第一封装结构11和第二封装结构12之间的间隙内还可以填充有包覆锡球13的底部填充料14。另外,第一封装结构11和第二封装结构12通常还包括设置于外表面的阻焊层(图中未示出)。

3、pop结构中各个package来自不同制造厂,各个制造厂之间在一般情况下不会特别去考虑pop时各个材料的cte(coefficient of thermal expansion,热膨胀系数)是否匹配。在前段没有考虑材料cte的情况下,装配厂在堆叠package时就会遇到因cte不匹配导致的翘曲(warpage)及其所衍伸的焊接等问题,例如第一封装结构11与第二封装结构12因翘曲使得各个锡球接点之间的距离不同造成第一封装结构11无法良好的焊接到第二封装结构12上。

技术实现思路

1、本申请提出了一种半导体封装装置,用于解决pop结构因在前端工序中无法考虑各个封装的cte导致堆叠后容易产生翘曲等技术问题。

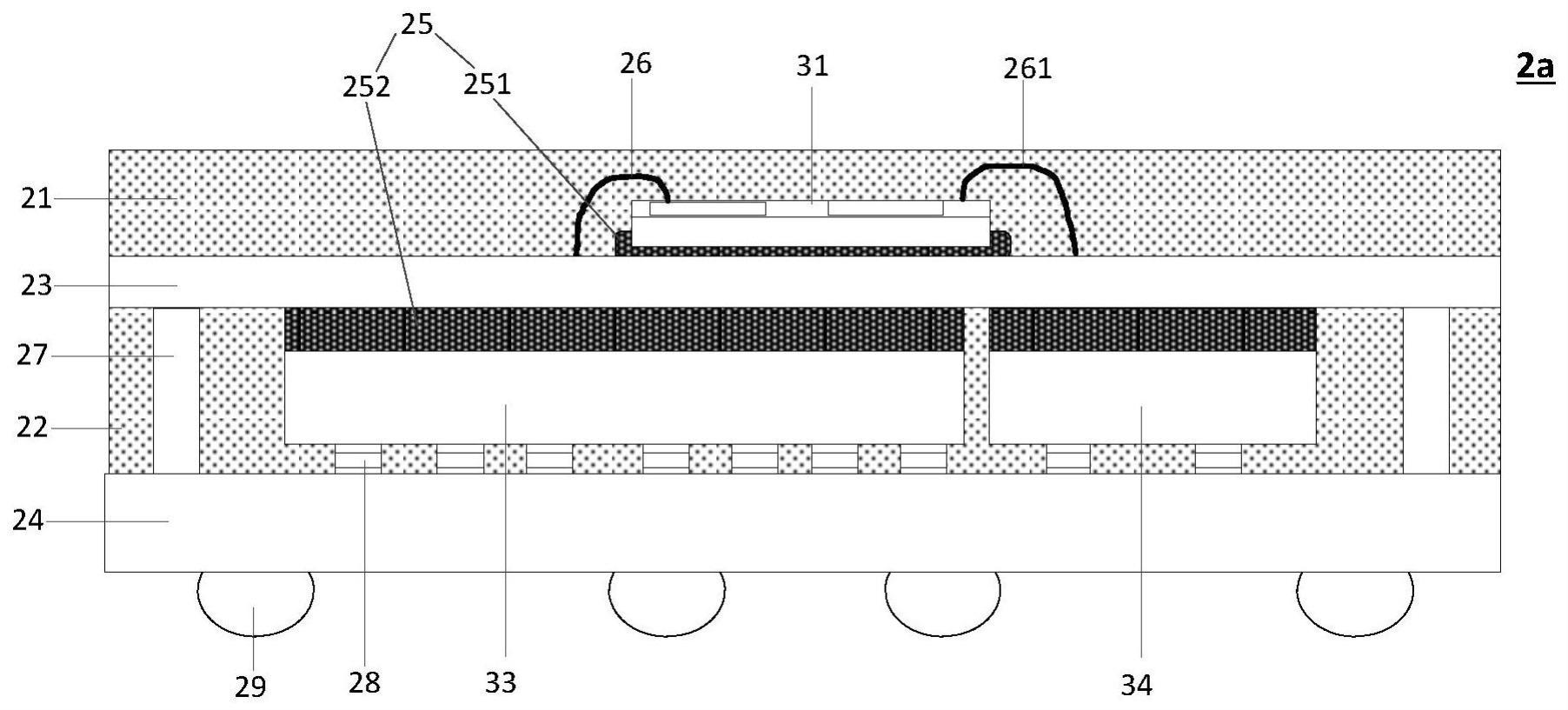

2、为实现上述目的,本申请提供如下技术方案:一种半导体封装装置,包括:第一模封材和第二模封材;第一重布线层,设置在所述第一模封材和所述第二模封材之间;第一芯片,埋设在所述第一模封材内,通过第一接合线与所述第一重布线层电性连接。

3、在一些可选的实施方式中,所述第一芯片通过第一粘着层连接在所述第一重布线层上,所述第一芯片的背面朝向所述第一重布线层。

4、在一些可选的实施方式中,所述的半导体封装装置还包括堆叠在所述第一芯片上的第二芯片,所述第二芯片埋设在所述第一模封材内。

5、在一些可选的实施方式中,所述第二芯片通过第二接合线与所述第一芯片电性连接。

6、在一些可选的实施方式中,所述的半导体封装装置还包括:第三芯片,埋设在所述第二模封材内,通过第二粘着层连接在所述第一重布线层上,且所述第三芯片的背面朝向所述第一重布线层。

7、在一些可选的实施方式中,所述的半导体封装装置还包括:第四芯片,埋设在所述第二模封材内,通过所述第二粘着层连接在所述第一重布线层上;所述第四芯片的背面朝向所述第一重布线层,所述第四芯片与所述第三芯片并排设置,且所述第四芯片与所述第三芯片的厚度不同。

8、在一些可选的实施方式中,所述的半导体封装装置还包括:第二重布线层,相对于所述第一重布线层,设置在所述第二模封材的另一侧。

9、在一些可选的实施方式中,所述的半导体封装装置还包括:导热层,相对于所述第一重布线层,设置在所述第一模封材的另一侧。

10、在一些可选的实施方式中,所述的半导体封装装置还包括:所述第一模封材的硬度大于所述第二模封材的硬度。

11、在一些可选的实施方式中,所述的半导体封装装置还包括:所述第一模封材内填料的尺寸大于所述第二模封材内填料的尺寸。

12、在一些可选的实施方式中,所述的半导体封装装置还包括:所述第一芯片的主动面朝向所述第一重布线层,并与所述第一重布线层间隔开。

13、在一些可选的实施方式中,所述的半导体封装装置还包括:所述第三芯片的主动面朝向所述第一重布线层,并与所述第一重布线层间隔开。

14、为了解决pop结构因在前端工序中无法考虑各个封装的cte导致堆叠后容易产生翘曲等技术问题,本申请提出了一种半导体封装装置。本申请通过在某个封装(即第二模封材)的表面设置第一重布线层,再于第一重布线层上堆叠另一封装(即第一模封材),第一模封材和第二模封材内部可埋设有芯片,以此形成epop(embedded package on package,内埋式堆叠封装)结构。

15、相对于pop结构,本申请的epop结构不再有锡球结合的部分,而是一体式整体结构,刚性更佳,有助于抑制翘曲,而且,即便有翘曲状况发生,由于第一重布线层的结构强度比锡球结合部分高的多,也不会发生开裂的问题。

16、另外,本申请的epop结构,为一体式整体结构,不涉及来自不同制造厂的封装,因此,可以在制造过程中通过材料的选用进行cte的匹配,减少材料特性差异,以此有助于降低翘曲,并有助于解决因cte不匹配而衍伸的例如焊接等其它问题。

17、另外,pop结构包含锡球(厚度约80μm),且各个封装包含基板(厚度约200μm-300μm),厚度较大,难以薄化,而本申请的epop结构,利用重布线层

18、(厚度约50μm)取消了基板和锡球,厚度小的多,可实现较好的薄化效果。

19、另外,pop结构的各个封装之间采用锡球连接,会因为翘曲状况导致焊接不良或无法焊接,而本申请的epop结构,第一模封材和第二模封材通过第一重布线层连接,且第一模封材内埋设的第一芯片通过接合线连接第一重布线层,以此,可以避免产生焊接方面的问题,例如不会发生空孔问题,且电性能更好,且io(输入输出)密度更高。

20、另外,本申请的epop结构,减少了底部填充料和阻焊层等材料,通过减少材料的种类有助于降低cte不匹配从而抑制翘曲,还有助于减少材料和制程方面的成本。

21、另外,本申请的epop结构,为一体式整体结构,轻薄短小,可以在一个封装中实现更多功能,且制程效率更高,产能更高。

技术特征:

1.一种半导体封装装置,其特征在于,包括:

2.根据权利要求1所述的半导体封装装置,其特征在于,所述第一芯片通过第一粘着层连接在所述第一重布线层上,所述第一芯片的背面朝向所述第一重布线层。

3.根据权利要求1所述的半导体封装装置,其特征在于,还包括堆叠在所述第一芯片上的第二芯片,所述第二芯片埋设在所述第一模封材内。

4.根据权利要求3所述的半导体封装装置,其特征在于,所述第二芯片通过第二接合线与所述第一芯片电性连接。

5.根据权利要求1所述的半导体封装装置,其特征在于,还包括:第三芯片,埋设在所述第二模封材内,通过第二粘着层连接在所述第一重布线层上,且所述第三芯片的背面朝向所述第一重布线层。

6.根据权利要求5所述的半导体封装装置,其特征在于,还包括:第四芯片,埋设在所述第二模封材内,通过所述第二粘着层连接在所述第一重布线层上;所述第四芯片的背面朝向所述第一重布线层,所述第四芯片与所述第三芯片并排设置,且所述第四芯片与所述第三芯片的厚度不同。

7.根据权利要求1所述的半导体封装装置,其特征在于,还包括:第二重布线层,相对于所述第一重布线层,设置在所述第二模封材的另一侧。

8.根据权利要求1所述的半导体封装装置,其特征在于,还包括:导热层,相对于所述第一重布线层,设置在所述第一模封材的另一侧。

9.根据权利要求1所述的半导体封装装置,其特征在于,所述第一模封材的硬度大于所述第二模封材的硬度。

10.根据权利要求1所述的半导体封装装置,其特征在于,所述第一芯片的主动面朝向所述第一重布线层,并与所述第一重布线层间隔开。

技术总结

本申请提出了一种半导体封装装置,包括:第一模封材和第二模封材;第一重布线层,设置在第一模封材和第二模封材之间;第一芯片,埋设在第一模封材内,通过接合线与第一重布线层电性连接。本申请的半导体封装装置形成ePoP(内埋式堆叠封装)结构,是一体式整体结构,刚性更佳,有助于抑制翘曲。另外,可以在制造过程中通过材料的选用进行CTE的匹配,有助于降低翘曲。另外,本申请的ePoP结构可实现较好的薄化效果。另外,本申请通过接合线连接,IO(输入输出)密度更高。

技术研发人员:闵繁宇,李铮鸿

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:20230116

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!