半导体装置的制作方法

本实施方式涉及一种半导体装置。

背景技术:

1、已知有在cmos(complementary metal oxide semiconductor,互补式金属氧化物半导体)电路的上方设置存储单元阵列的半导体装置。对于这种半导体装置,提出了如下构造,即,在存储单元阵列上设置半导体源极层,进而在该半导体源极层上设置金属源极线。通过将金属源极线连接于半导体源极层,而使整个源极层的电阻降低。但是,构成金属源极线的金属层仅作为源极线使用,而无法用于其它用途。

技术实现思路

1、一实施方式提供一种将设置在半导体的源极层上的金属层不仅用作源极线还能够用于其它用途的半导体装置。

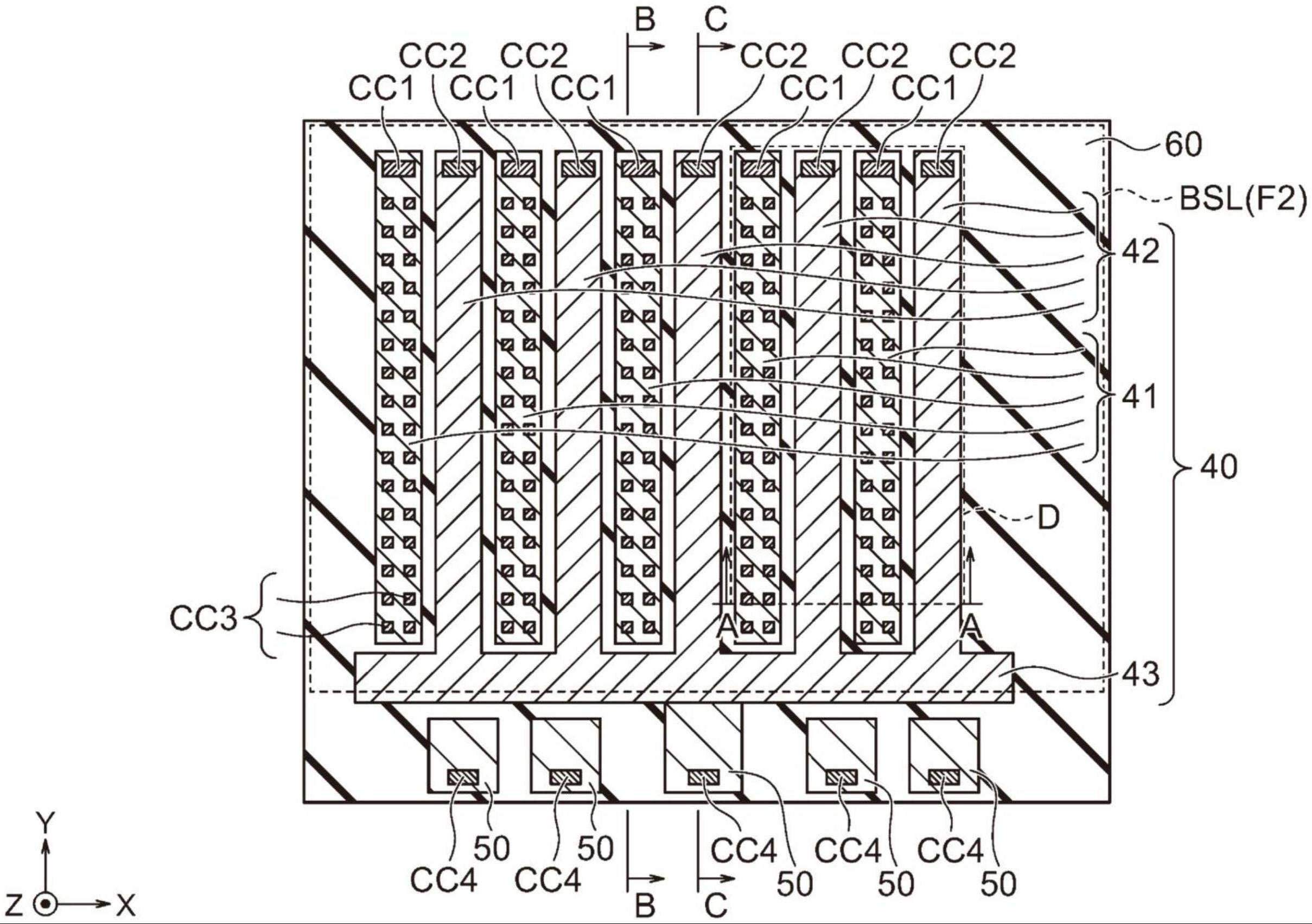

2、本实施方式的半导体装置具备多个晶体管。存储单元阵列设置在多个晶体管的上方。第1半导体层设置在存储单元阵列的上方,具有存储单元阵列侧的第1面及与第1面为相反侧的第2面。第1金属配线设置在第2面的上方,且电连接于第1半导体层。第2金属配线在第2面的上方设置在与第1金属配线相同的层中,且不与第1金属配线及所述第1半导体层接触。第1接点设置在第1金属配线的下方,在从第1面朝向第2面的第1方向上延伸,将多个晶体管中的一个电连接于第1金属配线。第2接点设置在第2金属配线的下方,在第1方向上延伸,将多个晶体管中的另一个电连接于第2金属配线。

3、根据所述构成,能够提供一种将设置在半导体的源极层上的金属层不仅用作源极线还能够用于其它用途的半导体装置。

技术特征:

1.一种半导体装置,其特征在于具备:多个晶体管;存储单元阵列,设置在所述多个晶体管的上方;第1半导体层,设置在所述存储单元阵列的上方,具有所述存储单元阵列侧的第1面及与所述第1面为相反侧的第2面;第1金属配线,设置在所述第2面的上方,电连接于所述第1半导体层;第2金属配线,在所述第2面的上方设置在与所述第1金属配线设置相同的层中,且不与所述第1金属配线及所述第1半导体层接触;第1接点,设置在所述第1金属配线的下方,在从所述第1面朝向所述第2面的第1方向上延伸,将所述多个晶体管中的一个电连接于所述第1金属配线;以及第2接点,设置在所述第2金属配线的下方,在所述第1方向上延伸,将所述多个晶体管中的另一个电连接于所述第2金属配线。

2.根据权利要求1所述的半导体装置,其特征在于还具备设置在所述第1半导体层上的第1绝缘层,所述多个第2金属配线设置在所述第1绝缘层上,通过该第1绝缘层而与所述第1半导体层电分离。

3.根据权利要求1所述的半导体装置,其特征在于还具备设置在所述第1半导体层上的第1绝缘层,所述多个第1金属配线设置在所述第1绝缘层上,经由设置在该第1绝缘层的多个第3接点而电连接于所述第1半导体层。

4.根据权利要求1至3中任一项所述的半导体装置,其特征在于所述多个第1金属配线及所述多个第2金属配线朝向与所述第2面平行的第2方向延伸。

5.根据权利要求4所述的半导体装置,其特征在于在从所述第1方向观察的俯视下,所述第1金属配线与所述第2金属配线朝向与所述第1方向及所述第2方向大致正交的第3方向交替配置。

6.根据权利要求5所述的半导体装置,其特征在于还具备第1电极,所述第1电极设置在所述第2面的上方,且与所述第1半导体层电分离,所述多个第2金属配线电连接于所述第1电极。

7.根据权利要求6所述的半导体装置,其特征在于还具备第4接点,所述第4接点在所述第1方向上延伸设置,且连接于所述第1电极与所述多个晶体管中的第3晶体管之间。

8.根据权利要求7所述的半导体装置,其特征在于在从所述第1方向观察的俯视下,所述多个第1金属配线分别具有在所述第2方向上具有长度方向的矩形形状,所述第2金属配线在所述多个第1金属配线之间延伸,将所述第2接点与所述第4接点之间电连接。

9.根据权利要求8所述的半导体装置,其特征在于在从所述第1方向观察的俯视下,与所述第2金属配线对向的所述多个第1金属配线的边相对于所述第2方向倾斜,与所述第1金属配线对向的所述第2金属配线的边相对于所述第2方向倾斜。

10.根据权利要求1所述的半导体装置,其特征在于还具备以与所述存储单元阵列电分离的状态贯通所述存储单元阵列内并连接于所述第1半导体层的配线,在从所述第1方向观察的俯视下,所述配线在与所述第1及第2金属配线交叉的方向上延伸。

11.根据权利要求10所述的半导体装置,其特征在于在从所述第1方向观察的俯视下,所述配线与所述第1及第2金属配线大致正交。

12.根据权利要求10所述的半导体装置,其特征在于所述配线包含设置在贯通所述存储单元阵列内而到达所述第1半导体层的狭缝的内壁的绝缘膜、及填埋该绝缘膜的内侧的导电材料。

技术总结

本技术的半导体装置具备晶体管。存储单元阵列设置在晶体管的上方。第1半导体层设置在存储单元阵列的上方,具有存储单元阵列侧的第1面及与第1面为相反侧的第2面。第1金属配线设置在第2面的上方,且电连接于第1半导体层。第2金属配线在第2面的上方设置在与第1金属配线相同的层中,且不与第1金属配线及第1半导体层接触。第1接点设置在第1金属配线的下方,在从第1面朝向第2面的第1方向上延伸,将多个晶体管中的一个电连接于第1金属配线。第2接点设置在第2金属配线的下方,在第1方向上延伸,将多个晶体管中的另一个电连接于第2金属配线。

技术研发人员:和田秀雄,滨中启伸

受保护的技术使用者:铠侠股份有限公司

技术研发日:20230222

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!