半导体工艺腔室的制作方法

本申请属于半导体加工,具体涉及一种半导体工艺腔室。

背景技术:

1、在晶圆表面制成薄膜,即制成金属硅化物的工艺技术中,通常采用半导体工艺设备,例如pvd(physical vapor deposition,物理气相淀积)磁控溅射设备在晶圆表面上沉积薄膜,具体是使靶材的金属原子逸出靶材,以借助逸出的金属原子在工艺腔室内扩散,并对晶圆进行轰击,从而在晶圆上沉积薄膜。

2、为了避免逸出的金属原子扩散至工艺腔室的内壁,并污染内壁,需要在工艺腔室内设置内衬以对内壁进行遮挡,从而避免工艺腔室长期使用过程中被污染。但由于在工艺过程中内衬上会积累越来越多的电荷,该电荷会对加工晶圆产生不良影响,因此,为及时导走内衬上的电荷,以及为确保内衬两端电位一致,当前所采用的方式是在承载晶圆的基座上安装有接地环和接地弹片,当基座在工艺腔室内上升到加工晶圆的工艺位时,内衬的一端会与接地弹片接触,以将电荷通过接地弹片、接地环和基座导走,并且,由于内衬的另一端设在内壁上,因此,通过此种设置方式可以将内衬接地设置的同时,确保内衬两端电位保持一致。

3、但随着加工晶圆的次数增加,即基座会在工艺腔室内反复上升到工艺位,此时,内衬和接地环会反复压缩接地弹片,这容易使接地弹片发生过度变形甚至断裂的问题,因此需要定期进行更换,而这容易导致晶圆的生产效率较低,同时,由于接地弹片的限制,基座在工艺腔室内上升的高度有限,进而不利于实现在晶圆上沉积更多不同薄膜厚度的需求,即不利于工艺的调节。

技术实现思路

1、本申请公开一种半导体工艺腔室,以解决相关技术涉及的半导体工艺腔室存在生产晶圆效率较低以及不利于工艺调节的问题。

2、为了解决上述技术问题,本申请采用下述技术方案:

3、一种半导体工艺腔室,包括腔室本体、基座、内衬和接地件,所述基座设置于所述腔室本体内且用于承载晶圆,所述内衬环绕所述基座设置,所述内衬的顶端与所述腔室本体相连,所述接地件包括相连的第一分部和第二分部,所述第一分部贴附于所述内衬的底端,所述第二分部贴附于所述腔室本体。

4、本申请采用的技术方案能够达到以下有益效果:

5、本申请中,由于内衬的顶端与腔室本体相连,因此,内衬的顶端处于接地设置的状态,并且由于接地件的第一分部贴附于内衬的底端,与第一分部相连的接地件的第二分部贴附于腔室本体上,因此,内衬的底端通过接地件与腔室本体始终相连,即内衬的底端始终处于接地设置的状态,这使得内衬两端的电位保持一致,以避免影响加工晶圆的工艺效果。同时,由于接地件始终连接内衬的底端和腔室本体,且基座在腔室本体内运动时,接地件不限制基座在腔室本体内的高度,这使得晶圆上可以沉积更多不同厚度的薄膜,并且接地件也不受内衬和接地环的反复压缩,这使得接地件不容易发生过度变形甚至断裂的问题,进而不需要定期进行更换,进而不容易导致晶圆的生产效率较低。因此,本申请公开的半导体工艺设备能够解决相关技术涉及的半导体工艺腔室存在生产晶圆效率较低以及不利于工艺调节的问题。

技术特征:

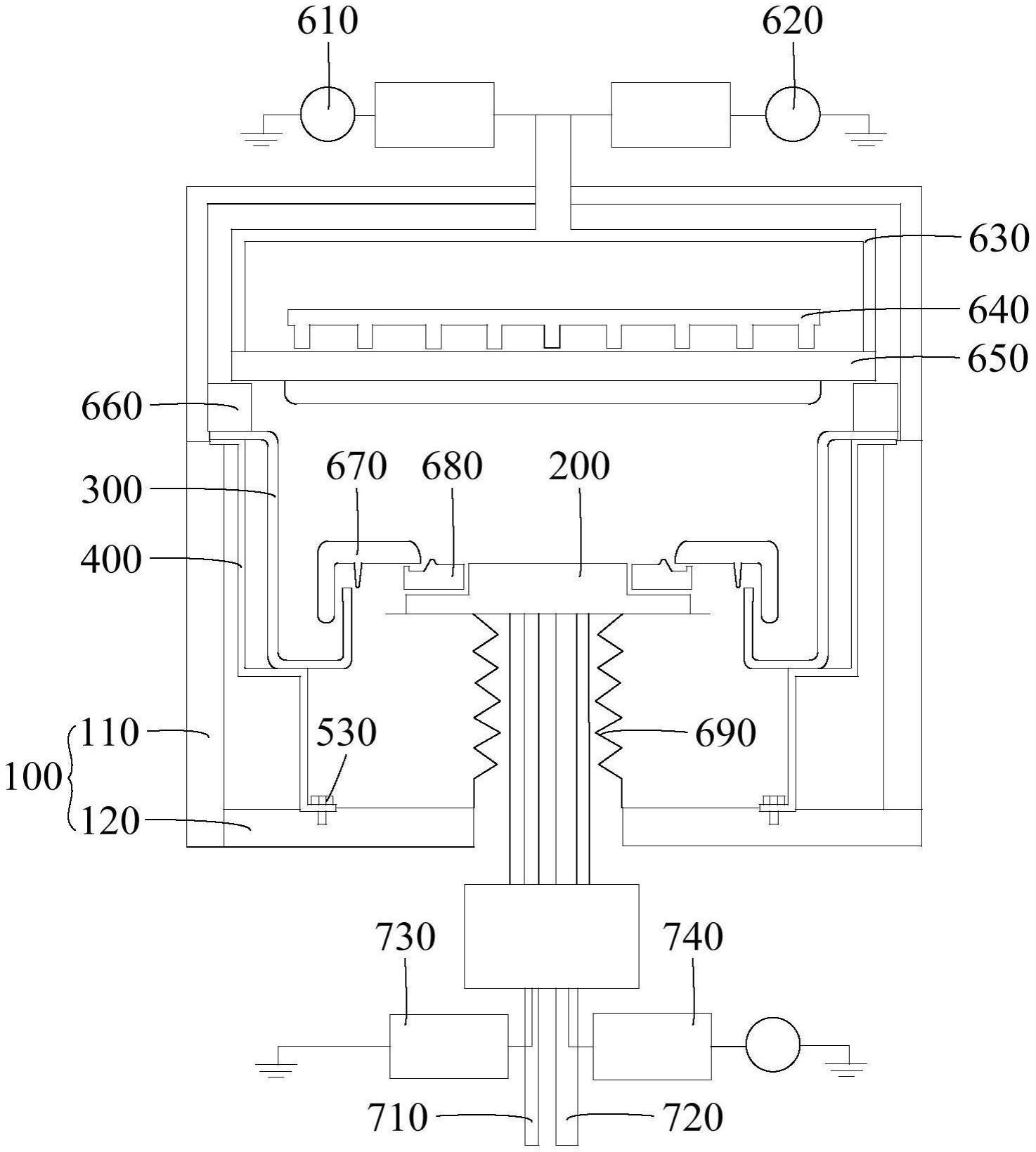

1.一种半导体工艺腔室,其特征在于,包括腔室本体(100)、基座(200)、内衬(300)和接地件(400),所述基座(200)设置于所述腔室本体(100)内且用于承载晶圆,所述内衬(300)环绕所述基座(200)设置,所述内衬(300)的顶端与所述腔室本体(100)相连,所述接地件(400)包括相连的第一分部(420)和第二分部(430),所述第一分部(420)贴附于所述内衬(300)的底端,所述第二分部(430)贴附于所述腔室本体(100)。

2.根据权利要求1所述的半导体工艺腔室,其特征在于,所述腔室本体(100)包括侧壁(110),所述内衬(300)的顶端与所述侧壁(110)相连,所述第二分部(430)沿竖直方向延伸,且所述第二分部(430)贴附于所述侧壁(110)。

3.根据权利要求1所述的半导体工艺腔室,其特征在于,所述腔室本体(100)包括侧壁(110),所述内衬(300)的顶端与所述侧壁(110)相连,所述第二分部(430)包括第一子分部(431)和第二子分部(432),所述第一子分部(431)、所述第二子分部(432)和所述第一分部(420)依次相连,且所述第一子分部(431)设于所述内衬(300)的顶端与所述侧壁(110)之间。

4.根据权利要求3所述的半导体工艺腔室,其特征在于,所述半导体工艺腔室还包括第一紧固件(510),所述内衬(300)的顶端设有第一连接孔,所述第一子分部(431)设有第二连接孔(410),所述第一紧固件(510)的一端依次穿过所述第一连接孔和所述第二连接孔(410),并与所述侧壁(110)相连。

5.根据权利要求3所述的半导体工艺腔室,其特征在于,所述第一分部(420)沿水平方向延伸,所述第一分部(420)的一端与所述内衬(300)的底端相贴合,所述第一分部(420)的另一端设有沿竖直方向延伸的第一弯折片(421),所述第一弯折片(421)与所述侧壁(110)相连。

6.根据权利要求5所述的半导体工艺腔室,其特征在于,所述半导体工艺腔室还包括第二紧固件(520),所述第一弯折片(421)设有第三连接孔(422),所述第二紧固件(520)的一端穿过所述第三连接孔(422)与所述侧壁(110)相连。

7.根据权利要求1所述的半导体工艺腔室,其特征在于,所述腔室本体(100)包括相连的侧壁(110)和底壁(120),所述接地件(400)还包括第三分部(440),所述第二分部(430)、所述第一分部(420)和所述第三分部(440)依次相连,且所述第二分部(430)贴附于所述侧壁(110),所述第三分部(440)与所述底壁(120)相连。

8.根据权利要求7所述的半导体工艺腔室,其特征在于,所述第三分部(440)的一端与所述第一分部(420)相连,所述第三分部(440)的另一端设有沿水平方向延伸的第二弯折片(441),所述第二弯折片(441)贴附于所述底壁(120)。

9.根据权利要求1所述的半导体工艺腔室,其特征在于,所述接地件(400)的数量为至少两个,各所述接地件(400)沿环绕所述内衬(300)的方向间隔设置。

10.根据权利要求1所述的半导体工艺腔室,其特征在于,所述接地件(400)为一体式结构件。

技术总结

本申请公开一种半导体工艺腔室,属于半导体加工技术领域。所公开的半导体工艺腔室包括腔室本体、基座、内衬和接地件,所述基座设置于所述腔室本体内且用于承载晶圆,所述内衬环绕所述基座设置,所述内衬的顶端与所述腔室本体相连,所述接地件包括相连的第一分部和第二分部,所述第一分部贴附于所述内衬的底端,所述第二分部贴附于所述腔室本体。上述方案能够解决相关技术涉及的半导体工艺腔室存在生产晶圆效率较低以及不利于工艺调节的问题。

技术研发人员:夏伟,董彦超,耿硕,杨玉杰

受保护的技术使用者:北京北方华创微电子装备有限公司

技术研发日:20230227

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!