一种半蚀刻双基岛共源共栅半导体引线框架及其封装器件的制作方法

本技术涉及半导体封装领域,具体涉及一种半蚀刻双基岛共源共栅半导体引线框架及其封装器件。

背景技术:

1、共源共栅型gan功率器件是通过低压增强型si mosfet和耗尽型gan hemt串联封装形成常关器件,即cascode结构gan功率器件,图1所示为现有技术中cascode结构的电路原理图。cascode结构gan功率器件因栅极稳定性和漏电流的优势,在高达1mhz开关频率的大功率产品中最为适合使用。

2、目前常用的高性能si mosfet都是垂直型设计,其漏极、源极和栅极不在晶圆同一侧,需要通过连接线从另一侧引出。目前常规qfn/dfn封装方案都是采用叠加基板来实现,但这种方案相对复杂,主功率回路电流路径交错曲折,直接引入的寄生杂散(源极串联电感和电阻)较大,很大程度上限制了封装后器件的整体性能(如器件的开关速度、开关振荡等性能)以及成本,也带来了额外的生产风险,甚至出现性能达不到设计要求等问题。

技术实现思路

1、为了解决现有技术存在的上述问题,本发明提供一种半蚀刻双基岛共源共栅半导体引线框架,解决需要采用叠加基板引出si mosfet漏极信号和封装走线复杂及良率风险等问题。

2、为了实现上述目的,本实用新型采用的技术方案如下:

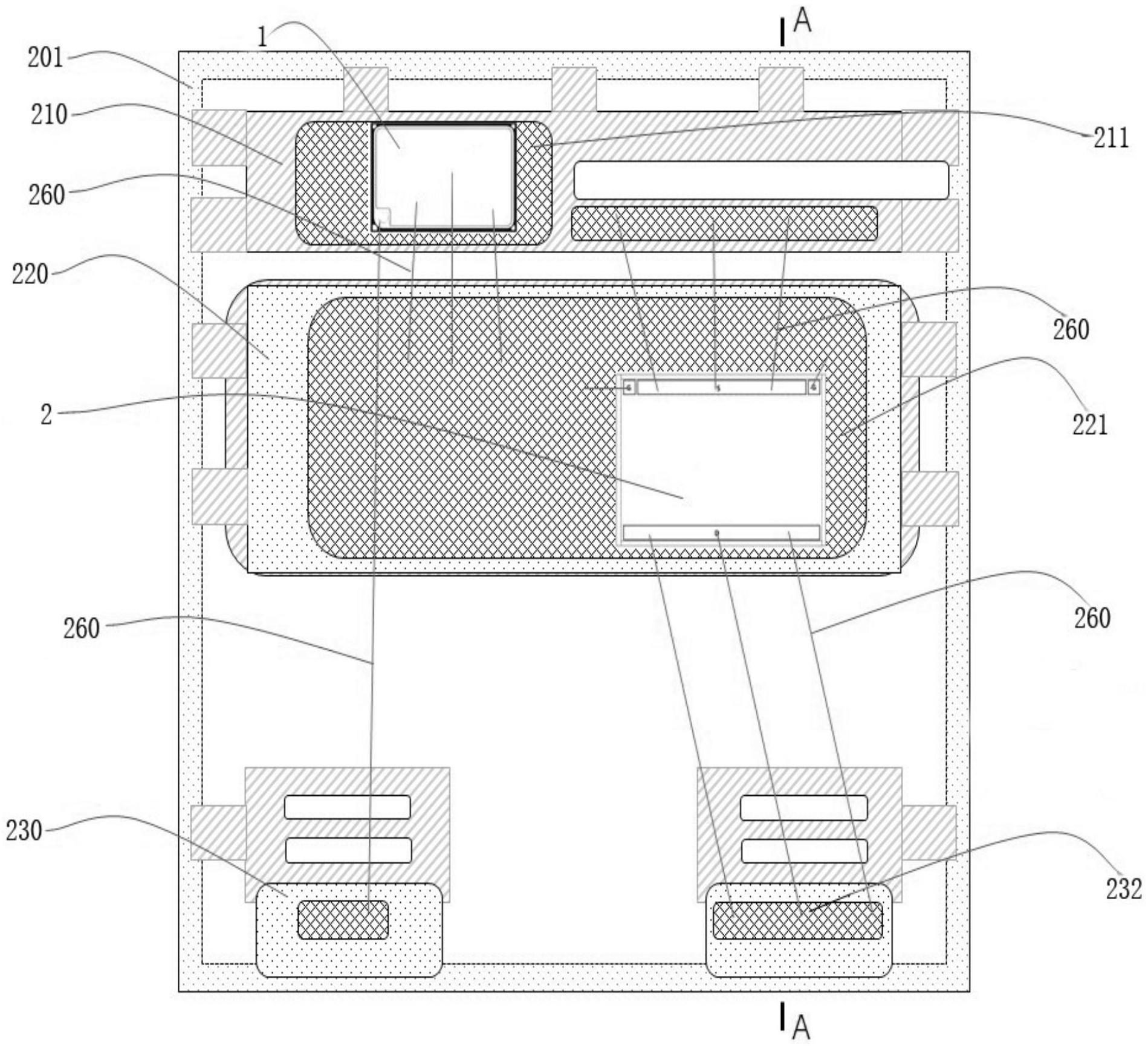

3、该半蚀刻双基岛共源共栅半导体引线框架,由若干个近似矩阵排列的框架单元组成,所述框架单元包括框架边框、基岛固定区、引脚、连筋和蚀刻区,所述框架边框位于外围边缘,所述基岛固定区包括间隔设置的第一基岛固定区和第二基岛固定区,所述第一基岛固定区设有半蚀刻的第一基岛,所述第二基岛固定区设有非蚀刻的第二基岛,所述第一基岛和第二基岛用于固定芯片;所述引脚位于所述基岛固定区的下方;所述连筋连接框架边框与基岛固定区及引脚;所述框架边框内的其他区域设置为蚀刻区,所述蚀刻区包围所述基岛固定区。

4、优选的,所述基岛固定区在其四周边缘设有半蚀刻的基岛支架,所述连筋连接所述基岛支架。

5、优选的,所述第一基岛上设有两个间隔的矩形镀银焊接区,所述第二基岛上设有矩形镀银焊接区,所述引脚上在其中间位置也设有矩形镀银焊接区。镀银焊接区用于与芯片和焊线的焊接连接。

6、优选的,所述第一基岛固定区位于第二基岛固定区的上方,所述第一基岛固定区采用双对称4个连筋连接所述框架边框的侧边和3个连筋连接所述框架边框的顶边,所述第二基岛固定区采用双对称4个连筋连接所述框架边框的侧边。

7、优选的,所述引脚设置两个,每个所述引脚的一侧与所述框架边框的一侧直接连接,每个所述引脚设有半蚀刻的引脚支架,所述引脚支架通过连筋与所述框架边框的另一侧相连。

8、优选的,所述第一基岛固定区上设有方形的应力释放孔,所述引脚支架上设有两个方形的应力释放孔。可用于应力释放和塑封填充。

9、优选的,所述连筋包括非蚀刻的根部和半蚀刻的前部,所述前部位于靠近基岛支架的半蚀刻区,根部位于远离基岛支架的框架边框上,所述连筋的定位支撑点位于所述蚀刻区。

10、本实用新型还提供一种上述半蚀刻双基岛共源共栅半导体引线框架封装器件,在所述引线框架上贴装si mosfet芯片和gan hemt芯片,所述si mosfet芯片通过导电银胶固定于第一基岛上,其源极和栅极位于顶部,其漏极位于底部并和第一基岛电性连接,所述gan hemt芯片通过导电银胶固定于第二基岛上,其源极、漏极和栅极都位于顶部,与第二基岛之间无电性连接;所述si mosfet芯片的栅极g与引脚通过焊线直接连接,形成封装器件的栅极g,所述gan hemt芯片的漏极d与引脚通过焊线直接连接,形成封装器件的漏极d;所述gan hemt芯片的源极s与第一基岛通过焊线直接连接,实现gan hemt芯片的源极s与simosfet芯片的漏极d的电性连接,形成第一引线;所述si mosfet芯片的栅极s与第二基岛通过焊线直接连接,形成第二引线;所述gan hemt芯片的栅极g与第一基岛通过焊线直接连接,形成第三引线。

11、优选的,增加一个引脚作为封装器件的源极s,将第二基岛固定区完全作为散热引脚,在器件使用中作为散热焊盘。

12、优选地,还包括隔离带和塑封料,所述隔离带贴附在蚀刻区、引脚和基岛固定区的背面,所述隔离带为耐高温pet薄膜或peek片材膜,且所述隔离带可剥离,在塑封之前隔离带贴附在框架的背面,塑封之后可将隔离带去除;所述塑封料通过塑封固化的方式将蚀刻区、第一基岛、第二基岛、si mosfet芯片、gan hemt芯片和焊线塑封于内,塑封料为长方体或小圆柱体,塑封时变成液体包裹上述组件和框架,最终再固化成型,且由塑封料粉状颗粒料堆砌而成。

13、本实用新型提供一种半蚀刻双基岛共源共栅半导体引线框架,可以将垂直型simosfet芯片直接固定在半蚀刻的一个基岛上,底部的电极信号直接通过基岛引出,减少了传统封装方式的对额外基板要求,同时因框架铜板的低阻抗和低感抗特性,极大地减少了因为复杂走线而引起的芯片内阻和电感的增加,减少了封装的复杂性,提高了器件的封装良率;半蚀刻的基岛封装了si mosfet漏极引脚,降低外部干扰信号引入器件;也减少了裸露si mosfet漏极器件的使用风险。同时,半蚀刻的扩展了漏极面积,也缩短了封装焊线的长度,减少了封装阻抗。

技术特征:

1.一种半蚀刻双基岛共源共栅半导体引线框架,其特征在于,由若干个近似矩阵排列的框架单元组成,所述框架单元包括:

2.根据权利要求1所述的半导体引线框架,其特征在于,所述基岛固定区在其四周边缘设有半蚀刻的基岛支架,所述连筋连接所述基岛支架。

3.根据权利要求1或2所述的半导体引线框架,其特征在于,所述第一基岛上设有两个间隔的矩形镀银焊接区,所述第二基岛上设有矩形镀银焊接区,所述引脚上在其中间位置也设有矩形镀银焊接区。

4.根据权利要求1或2所述的半导体引线框架,其特征在于,所述第一基岛固定区位于第二基岛固定区的上方,所述第一基岛固定区采用双对称4个连筋连接所述框架边框的侧边和3个连筋连接所述框架边框的顶边,所述第二基岛固定区采用双对称4个连筋连接所述框架边框的侧边。

5.根据权利要求1或2所述的半导体引线框架,其特征在于,所述引脚设置两个,每个所述引脚的一侧与所述框架边框的一侧直接连接,每个所述引脚设有半蚀刻的引脚支架,所述引脚支架上设有两个方形的应力释放孔,所述引脚支架还通过连筋与所述框架边框的另一侧相连。

6.根据权利要求1或2所述的半导体引线框架,其特征在于,所述第一基岛固定区上设有方形的应力释放孔。

7.根据权利要求1或2所述的半导体引线框架,其特征在于,所述连筋包括非蚀刻的根部和半蚀刻的前部,所述前部位于靠近基岛固定区的半蚀刻区,根部位于远离基岛固定区的框架边框上,所述连筋的定位支撑点位于所述蚀刻区。

8.一种权利要求1-7中任一半导体引线框架的封装器件,其特征在于,在所述引线框架上贴装si mosfet芯片和gan hemt芯片,所述si mosfet芯片通过导电银胶固定于第一基岛上,其源极和栅极位于顶部,其漏极位于底部并和第一基岛电性连接,所述gan hemt芯片通过导电银胶固定于第二基岛上,其源极、漏极和栅极都位于顶部,与第二基岛之间无电性连接;所述si

9.根据权利要求8所述的封装器件,其特征在于,增加一个引脚作为封装器件的源极s,将第二基岛固定区完全作为散热引脚,在器件使用中作为散热焊盘。

10.根据权利要求8或9所述的封装器件,其特征在于,还包括隔离带和塑封料,所述隔离带贴附在蚀刻区、引脚和基岛固定区的背面,所述隔离带为耐高温pet薄膜或peek片材膜,且所述隔离带可剥离,在塑封之前隔离带贴附在框架的背面,塑封之后可将隔离带去除;所述塑封料通过塑封固化的方式将蚀刻区、第一基岛、第二基岛、simosfet芯片、ganhemt芯片和焊线塑封于内,塑封料为长方体或小圆柱体,塑封时变成液体包裹上述组件和框架,最终再固化成型,且由塑封料粉状颗粒料堆砌而成。

技术总结

本技术涉及一种半蚀刻双基岛共源共栅半导体引线框架,由框架单元组成,框架单元包括框架边框、基岛固定区、引脚、连筋和蚀刻区,框架边框位于外围边缘,基岛固定区包括间隔设置的第一基岛固定区和第二基岛固定区,第一基岛固定区设有半蚀刻的第一基岛,第二基岛固定区设有非蚀刻的第二基岛,第一基岛和第二基岛用于固定芯片;引脚位于所述基岛固定区的下方,并与所述框架边框连接;连筋连接框架边框与基岛固定区及引脚;框架边框内的其他区域设置为蚀刻区,蚀刻区包围所述基岛固定区。该引线框架减少了传统封装方式对额外基板的要求,同时减少了封装的复杂性,提高了器件的封装良率。

技术研发人员:张勇

受保护的技术使用者:张勇

技术研发日:20230321

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!