一种基于复合介质栅的全局曝光光敏探测器的制作方法

本技术涉及一种基于复合介质栅的全局曝光光敏探测器,属于感光。

背景技术:

1、目前应用的感光技术从原理区分,主要有ccd(电荷耦合元件)和cmos(互补金属氧化物半导体)两种,其中cmos相对于ccd具有更快的成像速度和更加优良的系统集成能力,且可实现更低的功耗。但是,利用cmos实现的图像传感器的感光阵列中每个像素通常包括至少一个感光二极管和三至六个晶体管,使得感光区的占比较小。随着技术发展,对单位面积内像素数目提升的需求更加迫切,因而单个像素的面积设计得越来越小,cmos像素的满阱电荷量偏低,导致感光阵列面临着灵敏度下降及动态范围降低的问题。

2、中国专利cn102938409a和cn107658321b公开了几种基于复合介质栅mosfet的双晶体管光敏探测单元(以下将该探测单元结构称为垂直电荷感光器件,即vps),每个探测单元包括主要用于收集光电子的感光晶体管和用于读取光生电荷数量的读取晶体管。所述感光晶体管的衬底(收集区)和读取晶体管的衬底(读取区)通过浅槽隔离(sti)隔开,且均包括在衬底上依次叠加形成的底层绝缘介质、光电子存储层、顶层绝缘介质和控制栅,源/漏区设置在读取晶体管一侧的衬底中。所述感光晶体管和读取晶体管之间的光电子存储层连通,通过控制读取晶体管可以读出曝光过程从读取晶体管一侧衬底进入到光电子存储层的光生电荷量。上述光敏探测单元的制作可以与集成电路制造工艺兼容,且相较ccd和cmos,在相同像素尺寸下可实现更高的信噪比以及更高的满阱电荷,因而应用前景广阔。

3、利用上述的vps像素结构形成全局快门感光阵列时,需要设计一种方法,使得感光阵列在曝光结束后能够保持像素中的光电信号在后续的读取过程中不会发生变化,即像素中的信号量不会随着读取过程中持续入射到像素中的光子而持续累积。

4、一种常见的做法是,将曝光结束后像素内得到的光信号储存到一个额外的存储节点中,且通过一定设计使得该存储节点中储存的信号量不会随着光子持续不断地入射到像素中而发生变化。中国专利cn201711033195.x以及cn201910965769.x所公开的方法都是改变了vps像素的结构,在像素中增加了存储节点而实现了全局快门的功能。但这两种方法都会使vps像素的结构变得复杂,难以在亚微米的vps像素中实现全局快门的功能。另外,由于直接将存储节点集成在vps像素中,存储节点仍然会受到一定杂散光的照射进而导致快门关闭后其储存的信号随着光的持续照射而发生变化。

技术实现思路

1、发明目的:为了解决上述基于复合介质栅mosfet的全局曝光光敏探测器中的pls问题,同时不改变复合介质栅mosfet的双器件光敏探测器的简单的像素结构,本实用新型提供一种基于复合介质栅的全局曝光光敏探测器。

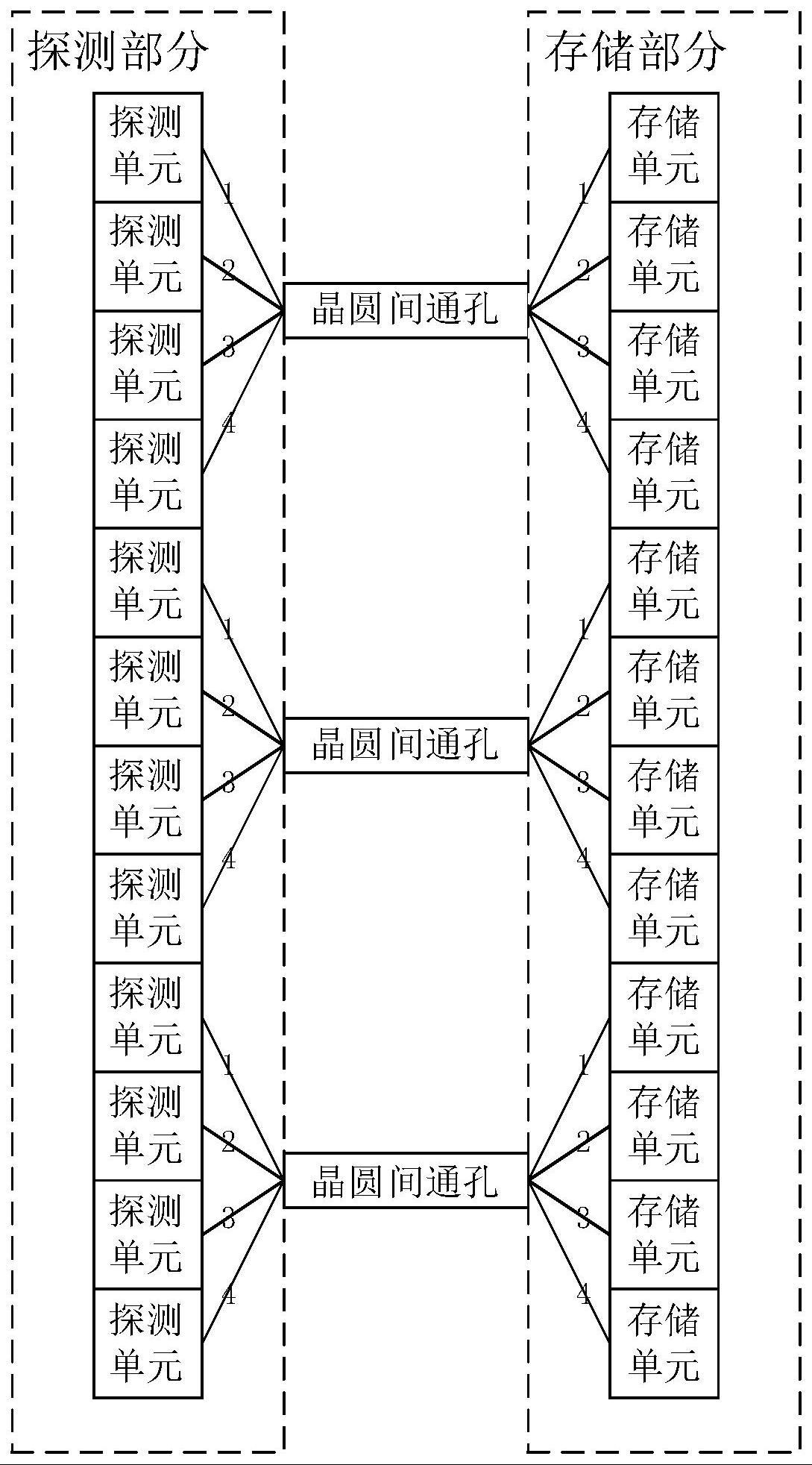

2、技术方案:为实现上述目的,本实用新型提供一种基于复合介质栅的全局曝光光敏探测器,包括制作于上晶圆部分的光敏探测部分和制作于下晶圆部分的存储部分,所述上晶圆部分与下晶圆部分之间通过晶圆堆叠工艺键合为一体,且两部分之间设置有晶圆间通孔进行电学互连;

3、所述光敏探测部分包含横向和纵向周期性排列的若干个复合介质栅双器件光敏探测单元,所述存储部分包含横向和纵向周期性排列的若干个存储单元,每个探测单元和一个存储单元对应,共同构成一个像素,所述探测单元和对应的存储单元之间通过晶圆间通孔进行信号传递。

4、可选的,所述探测单元包括具有感光功能的复合介质栅mos-c部分和具有读取功能的复合介质栅mosfet部分,且这两部分形成在同一p型半导体衬底上;所述复合介质栅mos-c部分和复合介质栅mosfet部分之间通过浅槽隔离隔开,且p型半导体衬底的上方依次叠加底层介质层、电荷耦合层、顶层介质层和控制栅极,所述复合介质栅mosfet部分还设有源极和漏极,且源极连接至所对应的晶圆间通孔。

5、可选的,所述存储单元包括采样mos晶体管、存储电容、源跟随mos晶体管和行选mos晶体管,其中采样mos晶体管的源极连接至所对应的晶圆间通孔,漏极连接至存储电容的一端,且与源跟随mos晶体管的栅极相连,所述存储电容的另一端接地;所述源跟随mos晶体管的源极连接至行选mos晶体管的源极,所有源跟随mos晶体管的漏极连接至同一电源电压。

6、可选的,各个组内同一编号的所述探测单元的控制栅极之间电学相连形成字线,字线的数目与每组内像素的个数相同;同一组内不同编号的所述探测单元的源极之间电学相连形成源线,且连接至所对应的晶圆间通孔,源线的数目与像素的组数即晶圆间通孔的个数相同;所有探测单元的漏极电学相连形成漏线,所有探测单元的衬底直接相连;不同组内同一编号的所述存储单元的采样mos晶体管的栅极之间电学相连构成转移线。

7、可选的,在所述存储部分中,对于每个晶圆间通孔,还设置有一个偏置mos晶体管(作为一个电流源)与其对应,其中,每个偏置mos晶体管的漏极连接至所对应的晶圆间通孔,源极接地,所有偏置mos晶体管的栅极全部相连形成偏置线。

8、可选的,所有行选mos晶体管的栅极和漏极之间采用标准cmos图像传感器像素阵列的互联架构,即同一行所述存储单元中的行选mos晶体管的栅极之间电学连接形成行线,同一列所述存储单元中的行选mos晶体管的漏极之间电学连接形成列线。

9、有益效果:

10、本实用新型通过使用制作于上晶圆的复合介质栅双器件光敏探测单元进行感光,使用制作于下晶圆的存储单元进行存储,将一个探测单元和一个存储单元组合为一个像素,且在结束曝光时使用晶圆堆叠时制作的晶圆间通孔将像素的探测单元得到的光电信号传递到像素的存储单元,实现了全局快门的功能。

11、由于本实用新型中复合介质栅双器件光敏探测单元的基本结构没有发生改变,仍然只包含感光晶体管和读取晶体管,其探测单元能够持续微缩至亚微米。而存储单元由于制作于不同的晶圆上,且全部由标准的mos晶体管和电容组成,在使用先进的制造工艺后同样具有持续微缩的能力。由于快门关闭时存储的电信号位于下晶圆,不会受到寄生光信号的影响,因而该光敏探测器的pls性能强于现有的探测器结构。

技术特征:

1.一种基于复合介质栅的全局曝光光敏探测器,其特征在于,包括制作于上晶圆部分的光敏探测部分和制作于下晶圆部分的存储部分,所述上晶圆部分与下晶圆部分之间通过晶圆堆叠工艺键合为一体,且两部分之间设置有晶圆间通孔进行电学互连;

2.根据权利要求1所述的全局曝光光敏探测器,其特征在于,所述探测单元包括具有感光功能的复合介质栅mos-c部分和具有读取功能的复合介质栅mosfet部分,且这两部分形成在同一p型半导体衬底上;所述复合介质栅mos-c部分和复合介质栅mosfet部分之间通过浅槽隔离隔开,且p型半导体衬底的上方依次叠加底层介质层、电荷耦合层、顶层介质层和控制栅极,所述复合介质栅mosfet部分还设有源极和漏极,且源极连接至所对应的晶圆间通孔。

3.根据权利要求2所述的全局曝光光敏探测器,其特征在于,所述存储单元包括采样mos晶体管、存储电容、源跟随mos晶体管和行选mos晶体管,其中采样mos晶体管的源极连接至所对应的晶圆间通孔,漏极连接至存储电容的一端,且与源跟随mos晶体管的栅极相连,所述存储电容的另一端接地;所述源跟随mos晶体管的源极连接至行选mos晶体管的源极,漏极连接至电源电压。

4.根据权利要求3所述的全局曝光光敏探测器,其特征在于,若干个像素组成一组像素,同一组像素共同使用同一个晶圆间通孔;每一组像素具有相同的个数,对每个组内的像素分别进行编号,每个编号均对应各个组内的一个像素。

5.根据权利要求4所述的全局曝光光敏探测器,其特征在于,不同组内同一编号的所述探测单元的控制栅极之间电学相连形成字线;同一组内不同编号的所述探测单元的源极之间电学相连形成源线,且连接至所对应的晶圆间通孔;所有探测单元的漏极电学相连形成漏线,所有探测单元的衬底直接相连;不同组内同一编号的所述存储单元的采样mos晶体管的栅极之间电学相连构成转移线。

6.根据权利要求3所述的全局曝光光敏探测器,其特征在于,在所述存储部分中,对于每个晶圆间通孔,还设置有一个偏置mos晶体管与其对应,其中,每个偏置mos晶体管的漏极连接至对应的晶圆间通孔,源极接地,所有偏置mos晶体管的栅极全部相连形成偏置线。

7.根据权利要求3所述的全局曝光光敏探测器,其特征在于,同一行所述存储单元中的行选mos晶体管的栅极之间电学连接形成行线,同一列所述存储单元中的行选mos晶体管的漏极之间电学连接形成列线。

技术总结

本技术公开了一种基于复合介质栅的全局曝光光敏探测器,通过使用制作于上晶圆的复合介质栅双器件光敏探测单元进行感光,使用制作于下晶圆的存储单元进行存储,将一个探测单元和一个存储单元组合为一个像素,且在结束曝光时使用晶圆堆叠时制作的晶圆间通孔将探测单元得到的光电信号转移到对应的存储单元中,实现了全局快门的功能。本技术不改变复合介质栅双器件光敏探测单元的基本结构,且探测单元和存储单元均能够持续微缩至亚微米。由于快门关闭时存储的电信号位于下晶圆,不会受到寄生光信号的影响,因而该光敏探测器的PLS性能强于现有的探测器结构。

技术研发人员:王瑶

受保护的技术使用者:南京威派视半导体技术有限公司

技术研发日:20230417

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!