半导体结构的制作方法

本技术实施例涉及半导体结构,尤其涉及退火栅极结构或导电结构的钌以减少或消除其缝隙。

背景技术:

1、随着半导体装置的制造方法进展与技术工艺节点尺寸缩小,短通道效应如热载子劣化、势垒降低、量子限制、与其他问题将影响晶体管。此外,随着晶体管的栅极长度缩小以用于较小的技术节点,将增加源极/漏极电子穿隧,其亦增加晶体管的关闭电流(比如在晶体管关闭时流动穿过晶体管通道的电流)。硅/硅锗纳米结构晶体管如纳米线、纳米片、与全绕式栅极装置可能克服较小技术节点的短通道效应。纳米结构晶体管相对于其他种类的晶体管,为减少短通道效应与增加载子迁移率的有效结构。

技术实现思路

1、本公开的目的在于提出一种半导体结构,以解决上述至少一个问题。

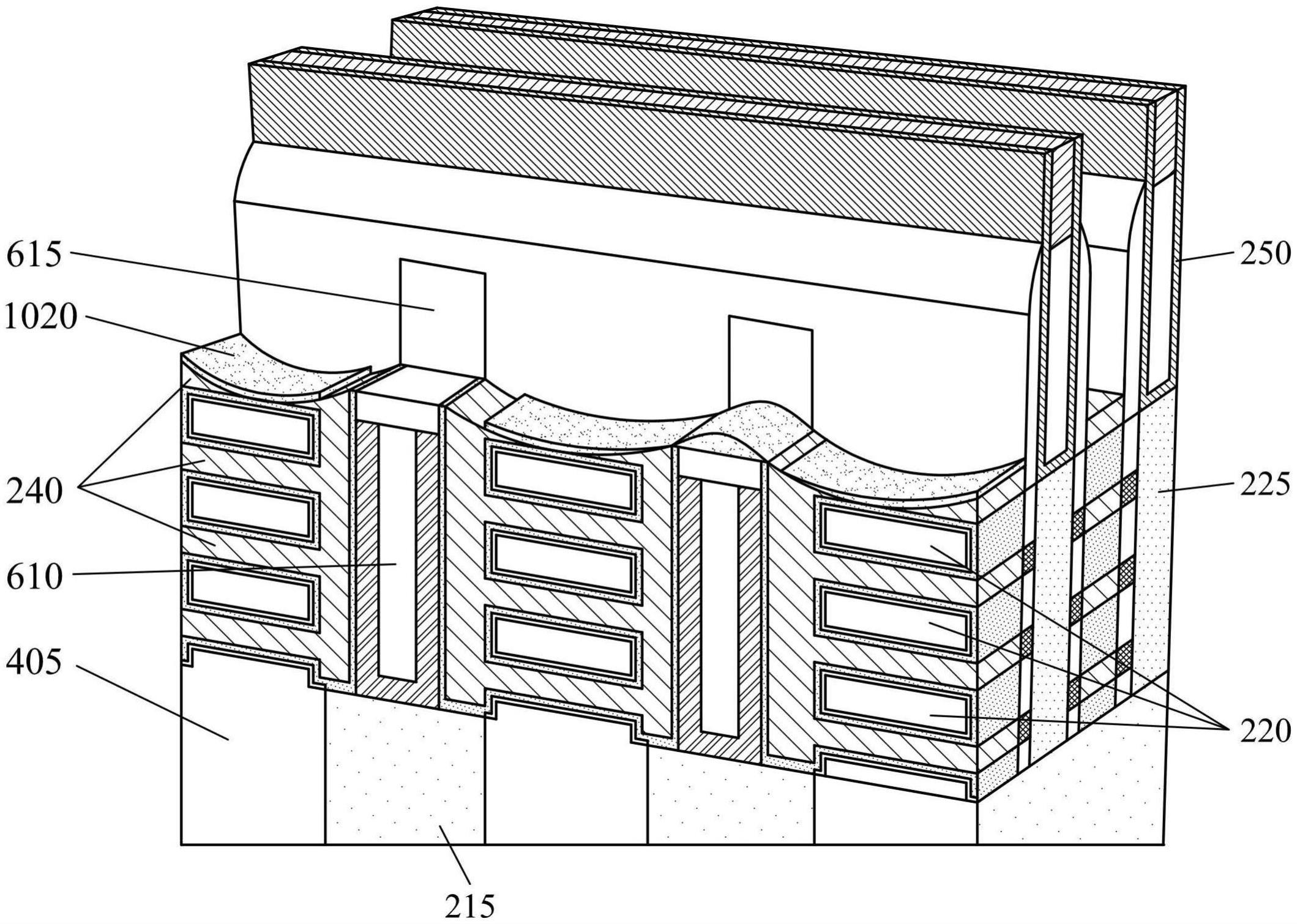

2、此处所述的一些实施方式提供半导体结构。半导体结构包括多个纳米结构通道,位于半导体基板上并沿着垂直于半导体基板的方向配置。半导体结构还包括栅极结构,包覆每一纳米结构通道,其中栅极结构包括钌,且钌中实质上无缝隙。

3、根据本公开其中的一个实施方式,钌包括的裸片数量为5至15。

4、根据本公开其中的一个实施方式,钌包括多个裸片,且多个所述裸片的中位数尺寸为6nm至15nm。

5、根据本公开其中的一个实施方式,每一多个所述纳米结构通道的高度为4nm至6nm。

6、根据本公开其中的一个实施方式,还包括:一盖沉积于该栅极结构上,其中该盖与该纳米结构通道物理地隔有该栅极结构。

7、此处所述的一些实施方式提供半导体结构。半导体结构包括凹陷,位于栅极接点或源极/漏极接点上的介电层中;以及导电结构,位于凹陷中,其中导电结构包括实质上无缝隙的钌。

8、根据本公开其中的一个实施方式,该栅极接点或该源极/漏极接点为前段工艺的接点,而该导电结构为中段工艺的接点。

9、根据本公开其中的一个实施方式,该导电结构与该介电层隔有一阻挡及/或衬垫层。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,钌包括的裸片数量为5至15。

3.如权利要求1所述的半导体结构,其特征在于,钌包括多个裸片,且多个所述裸片的中位数尺寸为6nm至15nm。

4.如权利要求1所述的半导体结构,其特征在于,每一多个所述纳米结构通道的高度为4nm至6nm。

5.如权利要求1所述的半导体结构,其特征在于,还包括:

6.一种半导体结构,其特征在于,包括:

7.如权利要求6所述的半导体结构,其特征在于,该导电结构的钌包括的裸片数量为5至15。

8.如权利要求6所述的半导体结构,其特征在于,该导电结构的钌包括多个裸片,且多个所述裸片的中位数尺寸为6nm至15nm。

9.如权利要求6所述的半导体结构,其特征在于,该栅极接点或该源极/漏极接点为前段工艺的接点,而该导电结构为中段工艺的接点。

10.如权利要求6所述的半导体结构,其特征在于,该导电结构与该介电层隔有一阻挡及/或衬垫层。

技术总结

一种半导体结构,在沉积钌之后,退火金属栅极及/或中段结构的钌以减少甚至消除缝隙。由于退火减少或移除沉积的钌中的缝隙,金属栅极及/或中断结构的电阻降低而增加电性效能。此外对金属栅极而言,退火可产生更一致的沉积轮廓,其可使时间控制的蚀刻工艺产生更一致的栅极高度。如此一来,蚀刻后的更多金属栅极可作用,其可在制造电子装置时增加良率。

技术研发人员:蔡昕翰,廖湘如,李易伦,洪正隆,张文,徐志安,洪若珺,李致葳,陈嘉伟

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230417

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!