半导体封装和功率模块的制作方法

本公开的实施例主要涉及半导体领域,并且更具体地,涉及半导体封装和包含该半导体封装的功率模块。

背景技术:

1、功率模块是指将功率管按照一定功能组合连接形成的模块。根据应用领域的不同,功率模块可实现变频、放大、稳压、整流、逆变等功能。对于多功率管(两个及以上)并联的功率模块中,各个功率管的源极需要统一连接至模块的ks信号端子再连接至驱动板,且ks信号端子有且只有一个;各个功率管的栅极需要统一连接至模块的栅极信号端子再连接至驱动板,且栅极信号端子有且只有一个。其中,ks信号是驱动板读取的信号,栅极信号是驱动板发出的控制信号,每个功率管导通和关断,则是通过栅极和ks的压差确定的。随着功率模块小型化趋势的发展以及现有的封装制造工艺的限制,多功率管并联的功率模块中,各功率管的电极(源极或栅极)只能先通过引线或铜夹电连接至基板,再由基板电连接至模块的信号端子,而由于每个功率管的电极(源极或栅极)到其相应的模块检测的信号端子的物理路径不同,使得驱动板读取和/或发出的信号不准确,最终导致功率模块的开关控制表现很差。

技术实现思路

1、根据本公开的示例实施例,提供了一种新的半导体封装方案。

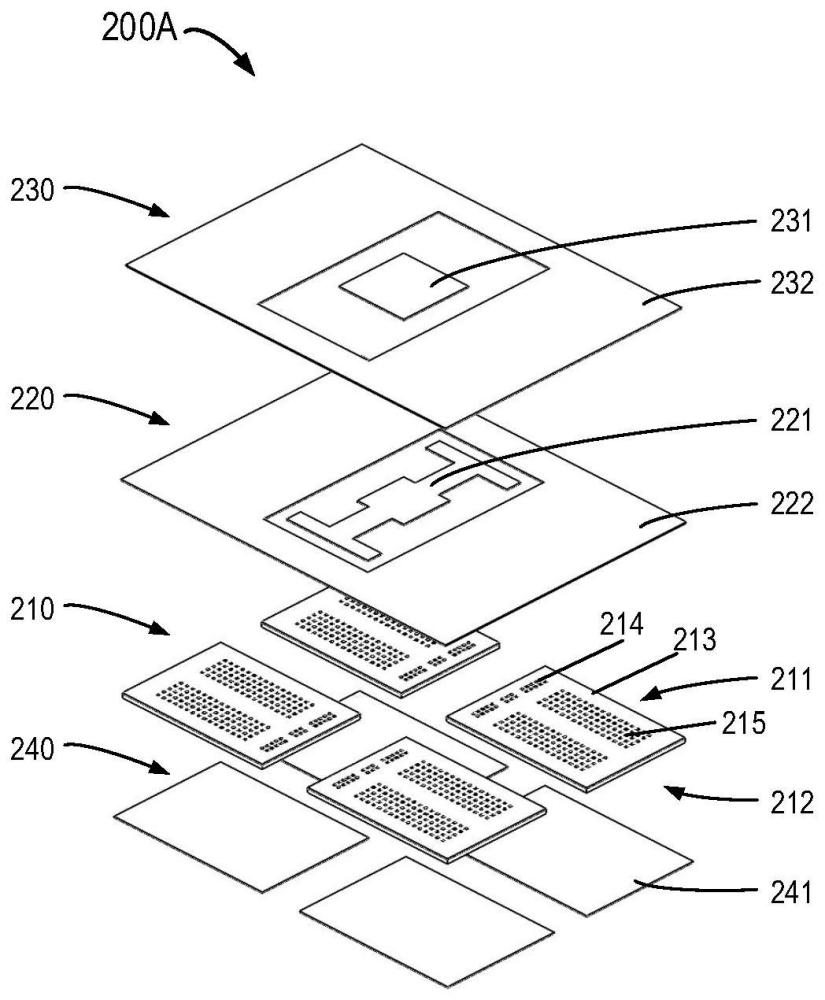

2、在本公开的第一方面中,提供了一种半导体封装。该半导体封装可以包括芯片层级,具有第一侧和与所述第一侧相对的第二侧,所述芯片层级包括多个功率管,每个功率管在所述第一侧处布置有源极和栅极。此外,该半导体封装还可以包括第一导电层级,在所述第一侧上,所述第一导电层级包括与所述栅极电连接的栅极连接部和与所述源极电连接的源极连接部。该半导体封装进一步包括第二导电层级,包括与所述栅极连接部电连接的栅极引出部和与所述源极连接部电连接的源极引出部,所述第一导电层级位于所述第二导电层级和所述芯片层级之间。

3、在本公开的第二方面中,提供了一种封装形成方法。该方法可以包括:形成芯片层级,所述芯片层级具有第一侧和与所述第一侧相对的第二侧,并且包括多个功率管,每个功率管在所述第一侧处布置有源极和栅极;在所述芯片层级的所述第一侧上形成第一导电层级,所述第一导电层级包括与所述栅极电连接的栅极连接部和与所述源极电连接的源极连接部;以及在所述第一导电层级的远离所述芯片层级的一侧上形成第二导电层级,所述第二导电层级包括与所述栅极连接部电连接的栅极引出部和与所述源极连接部电连接的源极引出部。

4、本公开的第三方面,提供了一种功率模块,包括:基板,至少布置有栅极接线板和源极接线板;以及如本公开的第一方面所描述的半导体封装,所述半导体封装位于所述基板上,并且所述栅极引出部通过栅极线电连接至所述栅极接线板,所述源极引出部通过源极线电连接至所述源极接线板。

5、提供

技术实现要素:

部分是为了以简化的形式来介绍一系列概念,它们在下文的具体实施方式中将被进一步描述。实用新型内容部分不旨在标识本公开的关键特征或必要特征,也不旨在限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

技术特征:

1.一种半导体封装,其特征在于,包括:

2.根据权利要求1所述的半导体封装,其特征在于,还包括:

3.根据权利要求1所述的半导体封装,其特征在于,每个所述功率管均包括:

4.根据权利要求1所述的半导体封装,其特征在于,所述栅极连接部包括:

5.根据权利要求4所述的半导体封装,其特征在于,所述多个连接分支被形成为使得所述多个功率管的栅极到达所述连接主体的导电路径一致。

6.根据权利要求3所述的半导体封装,其特征在于,所述源极区的面积大于所述栅极区的面积,并且所述源极连接部的面积大于或等于所述源极区的面积。

7.根据权利要求1所述的半导体封装,其特征在于,所述多个功率管的数目为四。

8.根据权利要求1所述的半导体封装,其特征在于,所述第一导电层级和所述第二导电层级是如下材料中的至少一种:

9.根据权利要求1所述的半导体封装,其特征在于,所述多个功率管包括第一组功率管和第二组功率管,并且所述第一导电层级包括:

10.根据权利要求9所述的半导体封装,其特征在于,还包括:

11.根据权利要求1所述的半导体封装,其特征在于,还包括:

12.一种功率模块,其特征在于,包括:

13.根据权利要求12所述的功率模块,其特征在于,所述栅极接线板和所述源极接线板分别经由引线框架的相应部分连接至驱动模块。

技术总结

本公开的实施例涉及半导体封装和功率模块。例如,提供了一种半导体封装。该半导体封装可以包括芯片层级,具有第一侧和与所述第一侧相对的第二侧,所述芯片层级包括多个功率管,每个功率管在第一侧处布置有源极和栅极。此外,该半导体封装还可以包括第一导电层级,第一导电层级包括与栅极电连接的栅极连接部和与源极电连接的源极连接部。该半导体封装进一步包括第二导电层级,包括与栅极连接部电连接的栅极引出部和与源极连接部电连接的源极引出部,第一导电层级位于第二导电层级和芯片层级之间。本公开的实施例可以通过改善半导体封装中的每个功率管的栅极和源极到达相应点位的导电路径的一致性来提升产品的工作性能表现。

技术研发人员:刘谦,R·蒂齐亚尼

受保护的技术使用者:深圳赛意法微电子有限公司

技术研发日:20230428

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!