降低沟槽MOSFET器件电容的结构的制作方法

本技术涉及功率mosfet器件,尤其是一种降低沟槽mosfet器件电容的结构。

背景技术:

1、功率mosfet器件的使用和发展已经有多年的历史,其在电子产业中的应用极其广泛,随着现代科技对电池、电机、电控的应用场景需求倍增,功率mosfet的需求量也越来越大,相应对功率mosfet器件的性能要求也不断提高。沟槽mosfet器件是常见的功率mosfet器件。

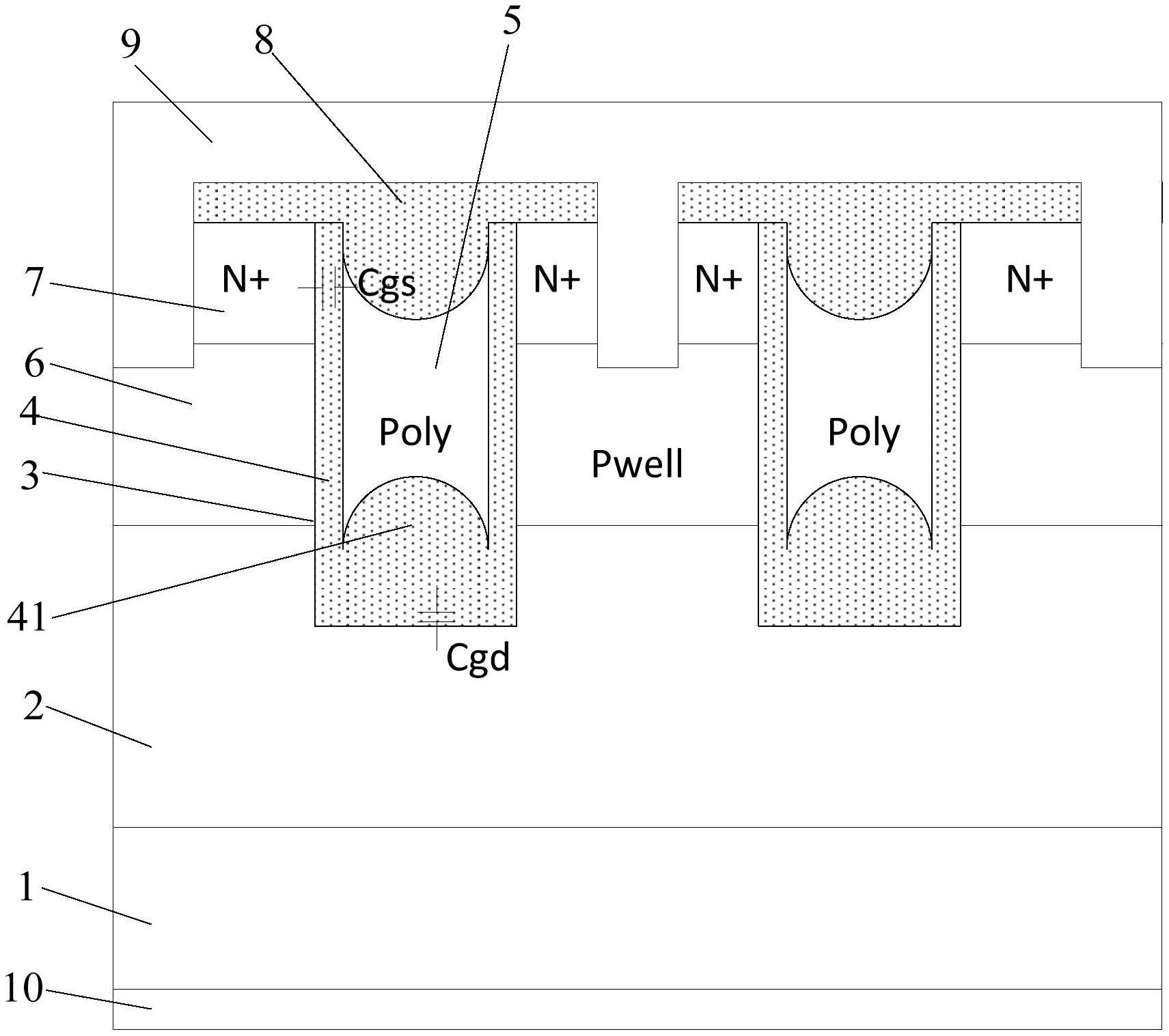

2、图1显示了一种沟槽mosfet器件,所述沟槽mosfet器件包括第一导电类型衬底1,在第一导电类型衬底1上设有第一导电类型外延层2;第一导电类型外延层2背离第一导电类型衬底1的表面为第一主面,第一导电类型衬底1背离第一导电类型外延层2的表面为第二主面;

3、在第一导电类型外延层2中设有第一类沟槽3,第一类沟槽3位于器件的元胞区;在第一类沟槽3内壁设有栅极氧化层4,且第一类沟槽3中填充有导电多晶硅5;第一类沟槽3中的导电多晶硅5作为栅极多晶硅;

4、在元胞区,第一导电类型外延层2上部形成自下而上分布的第二导电类型阱区6和重掺杂的第一导电类型源区7;

5、在第一主面设有绝缘介质层8,绝缘介质层8上设有源极金属9和栅极金属(图1中未画出栅极金属);源极金属9通过贯穿第一导电类型源区7的源极接触孔接触第二导电类型阱区6和第一导电类型源区7;栅极金属通过栅极接触孔(图1中未画出栅极接触孔)接触第一类沟槽3中的导电多晶硅;

6、在绝缘介质层8、源极金属9和栅极金属上还可以设置钝化层;

7、在第二主面设有漏极金属10。

8、普通沟槽mosfet器件的常规制造流程如下,以n型沟槽mosfet器件为例,第一导电类型为n型,第二导电类型为p型;

9、步骤s1,提供第一导电类型衬底1,如硅衬底,生长第一导电类型外延层2;在第一主面上淀积硬掩膜层,在硬掩膜层上涂光刻胶,通过第1掩膜光刻形成光刻胶沟槽图形,并刻蚀硬掩膜层,形成用于沟槽刻蚀的硬掩膜;然后刻蚀形成第一类沟槽3;生长栅极氧化层4;

10、此步骤需要用到第1掩膜(或称光刻板);

11、步骤s2,淀积导电多晶硅5并刻蚀,用于填充第一类沟槽3,形成栅极多晶硅;

12、步骤s3,硼离子注入并推阱形成第二导电类型阱区6,磷或砷离子注入并热退火形成第一导电类型源区7,其中磷或砷离子注入时需要在第一主面涂光刻胶,通过第2掩膜光刻形成光刻胶源区图形,以阻挡磷或砷离子在器件终端保护区的注入;

13、步骤s4,在第一主面淀积绝缘介质层8,通过第3掩膜光刻形成光刻胶接触孔图形,然后选择性刻蚀形成源极接触孔和栅极接触孔等各接触孔;

14、步骤s5,在绝缘介质层8上淀积金属层,再淀积光刻胶,通过第4掩膜光刻形成光刻胶源极金属图形、光刻胶栅极金属图形,刻蚀形成源极金属9和栅极金属;

15、有些可靠性要求高的场合还需要钝化层保护,制作钝化层时需要第5掩膜;

16、考量功率mosfet器件性能的两个主要参数,一个是导通电阻rdson,其决定了导通损耗的大小;一个是栅极电荷qg,其决定了开关损耗的大小。而qg参数又和mosfet寄生电容有直接的关系,mosfet寄生电容示意图如图2,其中,

17、输入电容ciss=cgd+cgs;

18、输出电容coss=cgd+cds;

19、反向电容crss=cgd

20、cgd为栅漏寄生电容,由栅漏之间氧化层决定;cgs为栅源寄生电容,由栅源之间氧化层决定;cds为源漏寄生电容,由mosfet的pn结电容决定;

21、在上述传统的沟槽mosfet器件结构中,电容参数和栅源电容、栅漏电容、漏源电容有直接的关系,为了降低整体的电容,必须想办法尽量降低cgs、cgd和cds。

22、cds由pn结电容决定,不会因为结构而改变;对于cgs,由于深沟槽的存在,栅极和源极的接触面积很大,而电容器之间的电介质(栅极氧化层)又很薄,根据公式c=εs/d可见,电容大小和面积成正比,和电介质厚度成反比,导致cgs很大,很难降低;对于cgd,由于在生长栅极氧化层的过程中,沟槽底部由于氧气含量低,其栅极氧化层厚度一般比侧壁更薄,根据同样的原理,cgd也是很难降低。

23、这样导致现有沟槽mosfet器件的电容参数很难降低,开关损耗很大,发热高,限制了其在高频领域的应用,局限明显。

24、近些年,为了降低mosfet的栅极电荷,分离栅mosfet器件在很多场合替代了普通沟槽mosfet器件成为主流,但分离栅mosfet器件的制造成本和难度远高于普通沟槽mosfet器件,特别是在40v n型以下的mosfet领域,沟槽mosfet器件依然占据主流地位。于是降低沟槽mosfet器件的电容参数依然是一个重要的课题。

技术实现思路

1、针对现有技术中存在的不足,本实用新型实施例提供一种降低沟槽mosfet器件电容的结构,在不增加制造成本的基础上,能够降低沟槽mosfet器件的电容。为实现以上技术目的,本实用新型实施例采用的技术方案是:

2、本实用新型实施例提供了一种降低沟槽mosfet器件电容的结构,包括第一导电类型衬底,在第一导电类型衬底上设有第一导电类型外延层;第一导电类型外延层背离第一导电类型衬底的表面为第一主面,第一导电类型衬底背离第一导电类型外延层的表面为第二主面;

3、在第一导电类型外延层中设有第一类沟槽,第一类沟槽位于器件的元胞区;在第一类沟槽的底部设有厚氧化层和栅极氧化层,第一类沟槽的侧壁设有栅极氧化层;第一类沟槽中填充有导电多晶硅;第一类沟槽中的导电多晶硅作为栅极多晶硅;

4、在元胞区,第一导电类型外延层上部形成自下而上分布的第二导电类型阱区和重掺杂的第一导电类型源区;

5、所述栅极多晶硅的顶部低于第一类沟槽的顶部,但高于第一导电类型源区的底部;

6、所述栅极多晶硅的底部低于第二导电类型阱区的底部;

7、在第一主面设有绝缘介质层,绝缘介质层填充第一类沟槽的顶部空间;绝缘介质层上设有源极金属和栅极金属;源极金属通过贯穿第一导电类型源区的源极接触孔接触第二导电类型阱区和第一导电类型源区;栅极金属通过栅极接触孔接触第一类沟槽中的导电多晶硅;

8、在第二主面设有漏极金属。

9、进一步地,在绝缘介质层、源极金属和栅极金属上还设有钝化层。

10、进一步地,所述第一类沟槽底部的厚氧化层呈现凸面弧度结构。

11、进一步地,所述栅极多晶硅的顶部呈现凹面弧度结构。

12、本实用新型实施例提供的技术方案带来的有益效果是:本申请通过改变沟槽内栅极多晶硅顶部和底部的形貌,从而降低了栅源寄生电容cgs和栅漏寄生电容cgd,达到了降低mosfet整体电容的目的;本申请的结构不仅没有增加制造成本,又起到了降低电容的效果。

技术特征:

1.一种降低沟槽mosfet器件电容的结构,包括第一导电类型衬底(1),在第一导电类型衬底(1)上设有第一导电类型外延层(2);第一导电类型外延层(2)背离第一导电类型衬底(1)的表面为第一主面,第一导电类型衬底(1)背离第一导电类型外延层(2)的表面为第二主面;

2.如权利要求1所述的降低沟槽mosfet器件电容的结构,其特征在于,

3.如权利要求1所述的降低沟槽mosfet器件电容的结构,其特征在于,

4.如权利要求1所述的降低沟槽mosfet器件电容的结构,其特征在于,

技术总结

本技术提供一种降低沟槽MOSFET器件电容的结构,包括第一导电类型衬底,在第一导电类型衬底上设有第一导电类型外延层;在第一导电类型外延层中设有第一类沟槽,第一类沟槽位于器件的元胞区;在第一类沟槽的底部设有厚氧化层和栅极氧化层,第一类沟槽的侧壁设有栅极氧化层;第一类沟槽中填充有导电多晶硅;第一类沟槽中的导电多晶硅作为栅极多晶硅;在元胞区,第一导电类型外延层上部形成自下而上分布的第二导电类型阱区和重掺杂的第一导电类型源区;所述栅极多晶硅的顶部低于第一类沟槽的顶部,但高于第一导电类型源区的底部;所述栅极多晶硅的底部低于第二导电类型阱区的底部;本申请能够降低沟槽MOSFET器件的电容。

技术研发人员:滕支刚

受保护的技术使用者:江苏临德半导体有限公司

技术研发日:20230511

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!