半导体量子芯片的栅极结构及载板的制作方法

本申请涉及量子计算机,特别是涉及一种半导体量子芯片的栅极结构及载板。

背景技术:

1、量子计算未来有望显著加速在传统计算机上几乎不可能解决的计算任务。在现有的量子计算物理体系中,由于量子比特尺寸小、局域化操控特性、与传统cmos制造工艺的兼容性较佳、较长的相干时间,以及潜在可超过1.5k以上应用的可能性等优势,使得基于自旋量子比特的半导体量子计算被视为有望实现大规模量子处理器的支持方案。

2、门控硅基自旋量子比特的自旋态信息难以借助有效的手段直接测量得到,当前比较成熟的测量方案是利用电荷探测器,将自旋态转化为可检测的电荷态,从而实现自旋量子比特的读出。电荷探测器通常位于量子比特非常近的地方(0-300nm),其输运电阻很大程度上依赖于其电荷状态。然而,在室温下利用放大器测量电荷探测器的直流电阻需要30μs-1ms的积分时间,由于受测量线路噪声,以及测量线路自身寄生电容和电荷探测器电阻所构成的rc时间常数的制约,从而导致了系统的测量带宽一直被局限在0-10khz量级,读取速度非常慢。在进行自旋量子比特实验时,由于初始化和操控都是在纳秒或微秒尺度上进行,因此这种缓慢的读出方式成为了主要的测量瓶颈。

3、对门控硅基自旋量子比特的自旋态信息的读取通常采用射频反射快速读出技术,可以在极短的时间内实现电子自旋状态的单发读出。但是,在硅基增强型晶体管量子器件中,单电子晶体管沟道的特征阻抗一般比较大,二维电子气形成的等效寄生电容也较大,并且门控电极下二维电子气也为用于读取的射频信号提供了一个低阻抗的泄露通道,使得射频反射读出技术在硅基体系中难以实现真正的应用。

技术实现思路

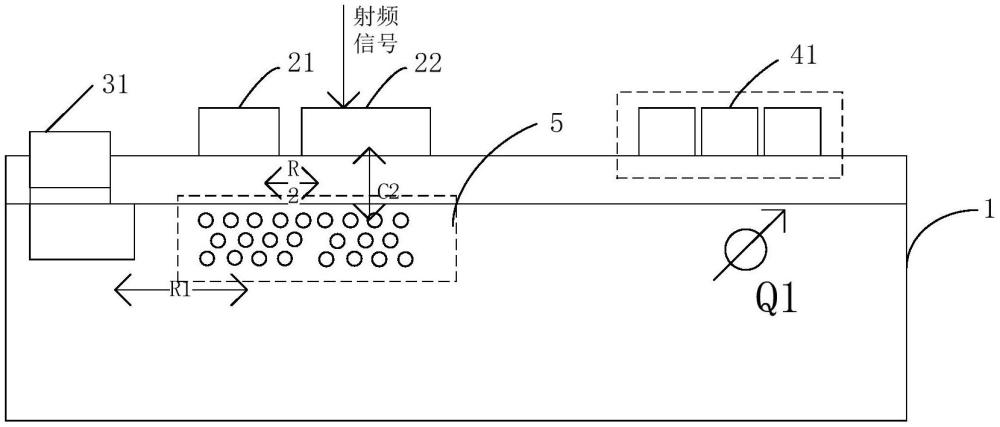

1、本申请提供一种半导体量子芯片的栅极结构及载板,用于解决现有技术中通过栅极施加射频信号对量子点进行读取时信号泄漏的问题,提高了对感应量子点的测量精度。

2、本申请一方面提供一种半导体量子芯片的栅极结构,包括:

3、第一栅极,用于施加第一直流电压信号以使所述第一栅极下方的沟道形成第一区域二维电子气;

4、第二栅极,用于施加第二直流电压信号调节所述第二栅极下方的沟道的第二区域二维电子气的电荷密度以形成感应量子点;

5、位于所述第一栅极和所述第二栅极之间的第三栅极,用于施加射频信号读取所述感应量子点的状态;

6、其中,所述第一栅极和所述第三栅极之间的电阻值为兆欧级。

7、如上所述的半导体量子芯片的栅极结构,优选的,所述第三栅极还用于施加第三直流电压信号以使所述第三栅极下方的沟道内形成第三区域二维电子气;

8、所述射频信号通过所述第三区域二维电子气输入至所述感应量子点。

9、如上所述的半导体量子芯片的栅极结构,优选的,所述第一栅极与所述第三栅极具有重叠端部,所述第一区域二维电子气与所述第三区域二维电子气通过所述重叠端部连通。

10、如上所述的半导体量子芯片的栅极结构,优选的,所述第一栅极和所述第三栅极在衬底上沿相对方向形成有第一延伸件和第二延伸件,在垂直延伸方向,所述第一延伸件的端部和所述第二延伸件的端部重叠形成所述重叠端部,所述重叠端部之间形成有绝缘介质层。

11、如上所述的半导体量子芯片的栅极结构,优选的,所述第一栅极和所述第三栅极均包括位于所述衬底周边的焊盘和一端连接所述焊盘的信号传输线,所述信号传输线的另一端延伸至所述感应量子点区域;

12、所述重叠端部位于所述信号传输线上靠近所述感应量子点区域的一端。

13、如上所述的半导体量子芯片的栅极结构,优选的,所述重叠端部的面积不小于10平方纳米且不大于100平方纳米。

14、如上所述的半导体量子芯片的栅极结构,优选的,所述第一栅极包括位于所述衬底周边的焊盘和一端连接所述焊盘的信号传输线,所述信号传输线的另一端延伸至所述感应量子点区域;

15、所述信号传输线靠近所述感应量子点的一端沿着所述信号传输线的延伸方向部分包括镂空孔。

16、如上所述的半导体量子芯片的栅极结构,优选的,所述信号传输线与所述镂空孔同轴,所述信号传输线上镂空孔两侧的信号传输线的宽度不大于60纳米。

17、如上所述的半导体量子芯片的栅极结构,优选的,所述第三栅极的阻抗小于所述感应量子点的阻抗。

18、本申请另一方面提供一种半导体量子芯片的载板,包括一pcb板,以及位于所述pcb板上的半导体量子芯片,所述半导体量子芯片采用任一项上述的栅极结构,所述半导体量子芯片的漏极电连接第一电阻,所述第一电阻的阻值不小于500千欧。

19、与现有技术相比,本申请通过将用于控制和测量的栅极按照功能进行拆分,采用相互独立的第一栅极和第三栅极分别用于控制和测量,且第一栅极和第三栅极之间的电阻值非常高,其阻抗非常大;当通过第三栅极施加射频信号对感应量子点进行读取时,避免射频信号沿着第一栅极的路径泄露,确保射频信号可以全部传输至感应量子点,提高对感应量子点的测量灵敏度和精确度。

20、本申请提供半导体量子芯片的载板包括上述半导体量子芯片的栅极结构,因此具有相同的有益效果,在此不再赘述。

技术特征:

1.一种半导体量子芯片的栅极结构,其特征在于,包括:

2.如权利要求1所述的半导体量子芯片的栅极结构,其特征在于,所述第三栅极还用于施加第三直流电压信号以使所述第三栅极下方的沟道内形成第三区域二维电子气;

3.如权利要求2所述的半导体量子芯片的栅极结构,其特征在于,所述第一栅极与所述第三栅极具有重叠端部,所述第一区域二维电子气与所述第三区域二维电子气通过所述重叠端部连通。

4.如权利要求3所述的半导体量子芯片的栅极结构,其特征在于,所述第一栅极和所述第三栅极在衬底上沿相对方向形成有第一延伸件和第二延伸件,在垂直延伸方向,所述第一延伸件的端部和所述第二延伸件的端部重叠形成所述重叠端部,所述重叠端部之间形成有绝缘介质层。

5.如权利要求4所述的半导体量子芯片的栅极结构,其特征在于,所述第一栅极和所述第三栅极均包括位于所述衬底周边的焊盘和一端连接所述焊盘的信号传输线,所述信号传输线的另一端延伸至所述感应量子点所在区域;

6.如权利要求4所述的半导体量子芯片的栅极结构,其特征在于,所述重叠端部的面积不小于10平方纳米且不大于100平方纳米。

7.如权利要求1所述的半导体量子芯片的栅极结构,其特征在于,所述第一栅极包括位于衬底周边的焊盘和一端连接所述焊盘的信号传输线,所述信号传输线的另一端延伸至所述感应量子点所在区域;

8.如权利要求7所述的半导体量子芯片的栅极结构,其特征在于,所述信号传输线与所述镂空孔同轴,所述信号传输线上镂空孔两侧的信号传输线的宽度不大于60纳米。

9.如权利要求1所述的半导体量子芯片的栅极结构,其特征在于,所述第三栅极的阻抗小于所述感应量子点的阻抗。

10.一种半导体量子芯片的载板,其特征在于,包括一pcb板,以及位于所述pcb板上的半导体量子芯片,所述半导体量子芯片采用如权利要求1-9任一项所述的栅极结构,所述半导体量子芯片的漏极电连接第一电阻,所述第一电阻的阻值不小于500千欧。

技术总结

本申请公开了一种半导体量子芯片的栅极结构及载板,栅极结构包括第一栅极,用于施加第一直流电压信号以使所述第一栅极下方的沟道形成第一区域二维电子气;第二栅极,用于施加第二直流电压信号调节所述第二栅极下方的沟道的第二区域二维电子气的电荷密度以形成感应量子点;位于所述第一栅极和所述第二栅极之间的第三栅极,用于施加射频信号读取所述感应量子点的状态;其中,所述第一栅极和所述第三栅极之间的电阻值为兆欧级。本申请解决了通过栅极施加射频信号对感应量子点进行读取时信号泄漏的问题,提高对感应量子点的测量灵敏度和精确度。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名,孔伟成

受保护的技术使用者:本源量子计算科技(合肥)股份有限公司

技术研发日:20230731

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!