半导体封装的制作方法

本技术实施例涉及一种半导体封装。更具体来说,本技术实施例涉及一种管芯之间具有有效的散热路径的半导体封装。

背景技术:

1、由于各种电子组件(即,晶体管、二极管、电阻器、电容器等)的集成密度的持续改善,半导体行业已经历快速增长。在很大程度上,集成密度的此种改善来自于最小特征大小(feature size)的重复减小,此使得更多更小的组件能够整合至给定面积中。该些更小的电子组件亦需要相较于以前的封装利用更少面积的更小的封装。用于半导体组件的一些较小类型的封装包括四方扁平封装(quad flat package,qfp)、引脚网格阵列(pin gridarray,pga)封装、球栅阵列(ball grid array,bga)封装、倒裝芯片(flip chip,fc)、三维集成电路(three-dimensional integrated circuit,3dic)、晶片级封装(waferlevelpackage,wlp)、叠层封装(package-on-package,pop)结构及集成扇出型(integrated fan-out,info)封装等。尽管现有的半导体封装一般已足以满足其预期目的,然而其尚未在所有方面皆完全令人满意。

技术实现思路

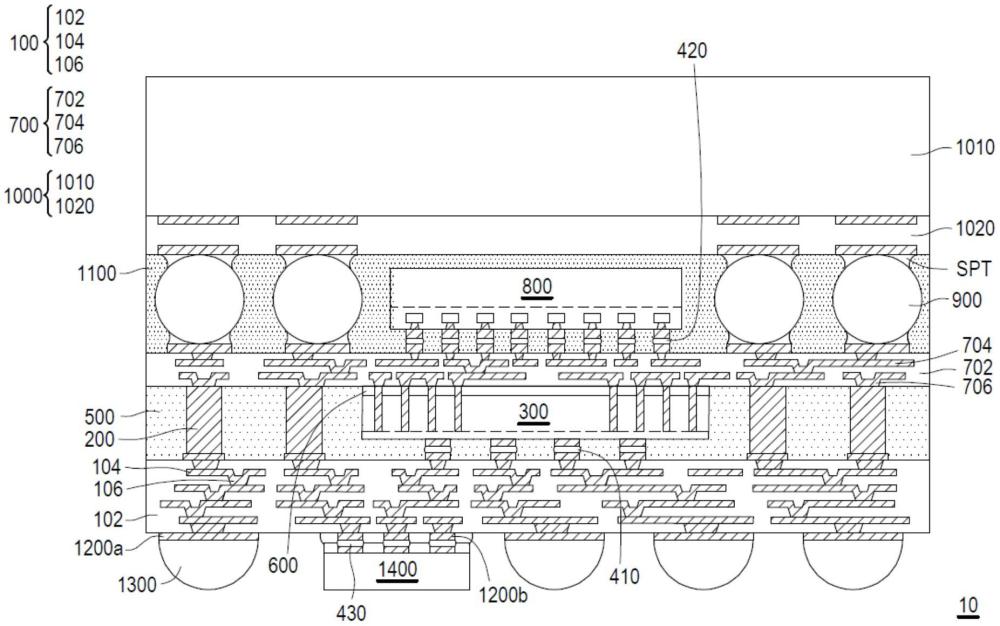

1、一种半导体封装包括第一重布线结构、第二重布线结构、第一管芯、第一包封体、第二管芯、第二包封体、导电连接件以及第三管芯。所述第二重布线结构位于所述第一重布线结构上。所述第一管芯位于所述第一重布线结构与所述第二重布线结构之间。所述第一包封体在侧向上包封所述第一管芯。所述第二管芯设置于所述第二重布线结构上且与所述第二重布线结构电连接。所述第二包封体在侧向上包封所述第二管芯。所述导电连接件环绕所述第二管芯且嵌入于所述第二包封体中。所述第三管芯设置于所述第二管芯上。所述第三管芯与所述第二包封体及所述导电连接件实体接触。

2、一种半导体封装包括第一重布线结构、第一管芯、第一包封体、第二重布线结构、第二管芯、导电连接件、第二包封体以及第三管芯。所述第一管芯具有有源表面及与所述有源表面相对的后表面。所述第一管芯设置于所述第一重布线结构上且与所述第一重布线结构电连接。所述第一包封体在侧向上包封所述第一管芯。所述第二重布线结构设置于所述第一管芯的所述后表面上。所述第二管芯设置于所述第二重布线结构上且与所述第二重布线结构电连接。所述导电连接件设置于所述第二重布线结构上且与所述第二重布线结构电连接。所述第二包封体在侧向上包封所述导电连接件及所述第二管芯。所述第二包封体完全覆盖所述导电连接件的侧壁。所述第三管芯设置于所述第二包封体及所述导电连接件上且与所述第二包封体及所述导电连接件实体接触。

技术特征:

1.一种半导体封装,其特征在于,包括:

2.根据权利要求1所述的半导体封装,其特征在于,所述第三管芯包括半导体衬底及设置于所述半导体衬底上的内连线结构,且所述内连线结构与所述第二包封体及所述导电连接件实体接触。

3.根据权利要求1所述的半导体封装,其特征在于,每一所述导电连接件包括导电球,所述导电球的一个端部与所述第二重布线结构实体接触,且所述导电球的另一端部与所述第三管芯实体接触。

4.根据权利要求1所述的半导体封装,其特征在于,每一所述导电连接件包括导电柱及与所述导电柱连接的导电球,其中所述导电柱与所述第二重布线结构实体接触,且所述导电球与所述第三管芯实体接触。

5.根据权利要求1所述的半导体封装,其特征在于,每一所述导电连接件包括第一导电球及与所述第一导电球连接的第二导电球,所述第一导电球与所述第二重布线结构实体接触,且所述第二导电球与所述第三管芯实体接触。

6.根据权利要求1所述的半导体封装,其特征在于,每一所述导电连接件包括导电柱及与所述导电柱连接的导电顶盖,所述导电顶盖与所述第二重布线结构实体接触,且所述导电柱与所述第三管芯实体接触。

7.一种半导体封装,其特征在于,包括:

8.根据权利要求7所述的半导体封装,其特征在于,所述第二管芯具有有源表面及与所述有源表面相对的后表面,所述第二管芯的所述有源表面面对所述第二重布线结构,且所述第二包封体的一部分夹置于所述第三管芯与所述第二管芯的所述后表面之间。

9.根据权利要求7所述的半导体封装,其特征在于,每一所述导电连接件包括导电球,所述导电球的一个端部与所述第二重布线结构实体接触,且所述导电球的另一端部与所述第三管芯实体接触。

10.根据权利要求7所述的半导体封装,其特征在于,每一所述导电连接件包括导电柱及与所述导电柱连接的导电球,其中所述导电柱与所述第二重布线结构实体接触,且所述导电球与所述第三管芯实体接触。

技术总结

本技术提供一种半导体封装包括第一重布线结构、第二重布线结构、第一管芯、第一包封体、第二管芯、第二包封体、导电连接件以及第三管芯。第二重布线结构位于第一重布线结构上。第一管芯位于第一重布线结构与第二重布线结构之间。第一包封体在侧向上包封第一管芯。第二管芯设置于第二重布线结构上且与第二重布线结构电连接。第二包封体在侧向上包封第二管芯。导电连接件环绕第二管芯且嵌入于第二包封体中。第三管芯设置于第二管芯上。第三管芯与第二包封体及导电连接件实体接触。

技术研发人员:刘醇鸿,蔡豪益

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230818

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!