半导体封装装置的制作方法

本技术涉及半导体封装,具体涉及一种半导体封装装置。

背景技术:

1、在高速差分信号线路的设计中,通孔(pth,plating through hole)和连接元件(如锡球)因为结构本身,会产生由于阻抗不连续而导致的信号反射现象,这会进一步导致额外的信号损耗。为了减缓阻抗不连续的现象,现有设计会在通孔衬垫和锡球衬垫的相对位置移除铜面,以减少寄生电容。

2、但是,在某些高速差分信号线路封装产品结合到基板时,需要通过使用底部填充胶来增加封装产品和基板之间的连接可靠度。这样,原先优化好的基板的电性(例如回波损耗s参数)会受到底部填充胶的介电系数特性的影响而产生劣化的效果。

3、因此,如何提升使用底部填充胶的基板的电性,是本领域技术人员亟需解决的技术问题。

技术实现思路

1、本实用新型提出了一种半导体封装装置。

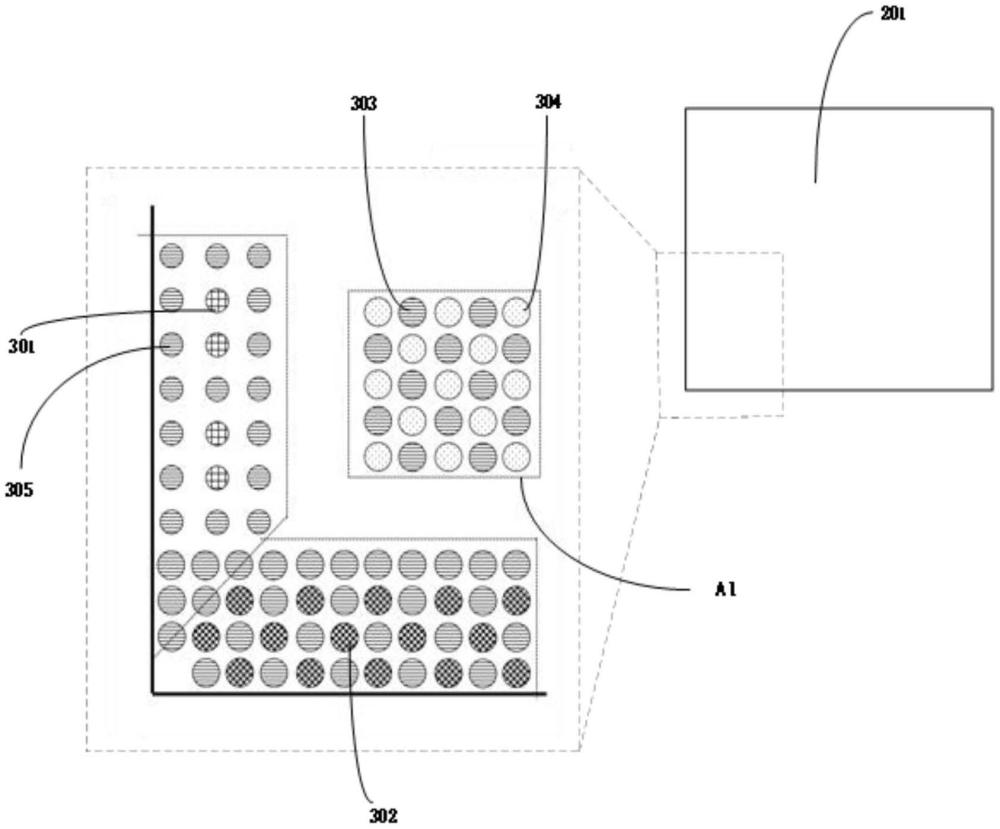

2、第一方面,本公开提供半导体封装装置,包括:电路结构,上述电路结构包括差分信号线衬垫和非差分信号线衬垫,上述差分信号线衬垫的尺寸小于上述非差分信号线衬垫的尺寸。

3、在一些可选的实施方式中,上述差分信号线衬垫设置在上述电路结构的边缘区域。

4、在一些可选的实施方式中,上述电路结构还包括:

5、电源区域;

6、上述电源区域设置在上述电路结构的中心区域,上述电源区域设置有电源接地衬垫和电源接电衬垫;其中,上述电源接地衬垫与相邻电源接电衬垫之间的间距小于相邻的差分信号线衬垫之间的间距。

7、在一些可选的实施方式中,上述电路结构还包括:

8、差分接地衬垫;

9、上述差分接地衬垫设置于上述差分信号线衬垫周围;其中,相邻的差分信号线衬垫之间的间距等于相邻的差分接地衬垫之间的间距。

10、在一些可选的实施方式中,还包括载板、第一连接元件和第二连接元件:

11、上述第一连接元件连接上述载板和上述差分信号线衬垫;

12、上述第二连接元件连接上述载板和上述非差分信号线衬垫。

13、在一些可选的实施方式中,其特征在于,还包括:

14、底部填充胶;

15、上述底部填充胶填充于上述载板和上述电路结构之间,且包覆上述第一连接元件和上述第二连接元件。

16、在一些可选的实施方式中,上述第一连接元件具有颈状特征。

17、在一些可选的实施方式中,相邻第一连接元件之间的间距大于相邻第二连接元件之间的间距。

18、在一些可选的实施方式中,上述电路结构具有相对的第一表面和第二表面,上述第一连接元件和上述第二连接元件设置于上述第一表面,上述半导体封装装置还包括:

19、电子元件,上述电子元件设置于上述电路结构的第二表面,上述电子元件通过上述电路结构连接上述载板。

20、在一些可选的实施方式中,还包括:

21、模封材料,上述模封材料包覆上述电子元件和上述电路结构。

22、为了解决提升使用底部填充胶的基板的电性,达到没有使用底部填充胶时的电性优化效果,本申请提供一种半导体封装装置,包括:电路结构,上述电路结构包括差分信号线衬垫和非差分信号线衬垫,上述差分信号线衬垫的尺寸小于上述非差分信号线衬垫的尺寸。这样,通过减少差分信号线衬垫的尺寸,减少差分信号连接元件的直径,增加差分信号连接元件之间的间距,以减少衬垫之间的寄生电容以及连接元件之间的寄生电容,使得阻抗匹配,整个差分信号线路的差模回波损耗符合预设需求。

技术特征:

1.一种半导体封装装置,其特征在于,包括:

2.根据权利要求1所述的半导体封装装置,其特征在于,所述差分信号线衬垫设置在所述电路结构的边缘区域。

3.根据权利要求2所述的半导体封装装置,其特征在于,所述电路结构还包括:

4.根据权利要求1所述的半导体封装装置,其特征在于,所述电路结构还包括:

5.根据权利要求1所述的半导体封装装置,其特征在于,还包括载板、第一连接元件和第二连接元件:

6.根据权利要求5所述的半导体封装装置,其特征在于,还包括:

7.根据权利要求5所述的半导体封装装置,其特征在于,所述第一连接元件具有颈状特征。

8.根据权利要求5所述的半导体封装装置,其特征在于,相邻第一连接元件之间的间距大于相邻第二连接元件之间的间距。

9.根据权利要求5所述的半导体封装装置,其特征在于,所述电路结构具有相对的第一表面和第二表面,所述第一连接元件和所述第二连接元件设置于所述第一表面,所述半导体封装装置还包括:

10.根据权利要求9所述的半导体封装装置,其特征在于,还包括:

技术总结

本公开提出了一种半导体封装装置,包括电路结构,所述电路结构包括差分信号线衬垫和非差分信号线衬垫,所述差分信号线衬垫的尺寸小于所述非差分信号线衬垫的尺寸。这样,通过减少差分信号线衬垫的尺寸,减少差分信号连接元件的直径,增加差分信号连接元件之间的间距,以减少衬垫之间的寄生电容以及连接元件之间的寄生电容,使得阻抗匹配,整个差分信号线路的差模回波损耗符合预设需求。

技术研发人员:蔡承佑,潘柏志,郭宏钧,钟明峰

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:20230831

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!