像素掺杂扩散的测试结构的制作方法

本技术涉及像素掺杂扩散的测试,特别是涉及一种像素掺杂扩散的测试结构。

背景技术:

1、图像传感器是指将光信号转换为电信号的装置,通常大规模商用的图像传感器芯片包括电荷耦合器件(ccd)和互补金属氧化物半导体(cmos)图像传感器芯片两大类。

2、cmos图像传感器和传统的ccd传感器相比,具有低功耗,低成本和与cmos工艺兼容等特点,因此得到越来越广泛的应用。现在cmos图像传感器不仅用于消费电子领域,例如微型数码相机(dsc),手机摄像头,摄像机和数码单反(dslr)中,而且在汽车电子,监控,生物技术和医学等领域也得到了广泛的应用。

3、cmos图像传感器按照入射光进入光电二极管的路径不同,可以分为前照式和背照式两种图像传感器,前照式是指入射光从靠近电路连接层的一面进入光电二极管的图像传感器,而背照式是指入射光从远离电路连接层的一面进入光电二极管的图像传感器。其中,光电二极管主要是由p型掺杂的硅基底进行n型掺杂形成,从而形成pn结,除此之外,像素单元中的晶体管的制备、像素单元之间的隔离的制备以及像素单元中晶体管之间的隔离的制备大多基于n型掺杂和p型掺杂形成。n型掺杂和p型掺杂的浓度需要进行准确控制,才能保证cmos图像传感器具有较好的性能。

4、为了准确控制n型掺杂的浓度和p型掺杂的浓度,通常需要事先测试n型掺杂和p型掺杂扩散的分布情况。大像素的掺杂校准一般采用在光片上做掺杂,即在干净的晶片(wafer)上采用i mp(离子注入)进行n型掺杂或p型掺杂,然后采用sims(二次离子质谱)测试的方式来校准掺杂扩散的纵向分布,仿真中通常设置掺杂扩散各向同性。然而,现在像素尺寸逐渐变小,对像素掺杂仿真的挑战逐渐变大,掺杂浓度变大,甚至扩散温度较高,还是沿用大像素的校准参数进行仿真的精度已经没法达到要求。而且,在cmos图像传感器的实际制作中,还存在其他结构对掺杂浓度的影响,在干净的晶片上进行掺杂测试,其测试结果和校准结果不准确,与实际的掺杂效果存在偏差。

技术实现思路

1、为了克服现有技术中存在的缺点和不足,本实用新型的目的在于提供一种像素掺杂扩散的测试结构,以解决现有技术中对像素的掺杂扩散测试不准确的问题。

2、本实用新型的目的通过下述技术方案实现:

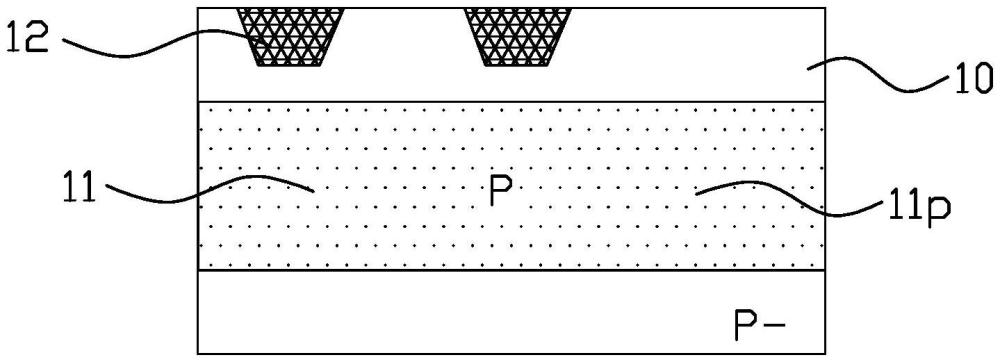

3、本实用新型提供一种像素掺杂扩散的测试结构,适于如上所述的像素掺杂扩散的测试方法,所述测试结构包括:

4、测试晶片,所述测试晶片内设有掺杂区;

5、所述测试晶片的正面设有测试调制结构,以对所述测试晶片的掺杂进行调制。

6、在其中一实施例中,所述测试调制结构包括沟槽隔离结构和光阻挡结构中的至少一种。

7、在其中一实施例中,所述沟槽隔离结构延伸至所述测试晶片内,以基于位于所述测试晶片内部的所述沟槽隔离结构调制所述掺杂处理;和/或,所述光阻挡结构至少位于所述测试晶片上,以基于位于所述测试晶片上的所述光阻挡结构调制所述掺杂处理。

8、在其中一实施例中,所述沟槽隔离结构与所述掺杂区以及所述光阻挡结构与所述掺杂区之间的布置方式包括如下方式中的至少一种:所述沟槽隔离结构与所述掺杂区在所述测试晶片表面的投影至少部分交叠;以及,所述掺杂区在所述测试晶片表面的投影覆盖相邻的所述沟槽隔离结构之间的开口在所述测试晶片表面的投影;以及,所述光阻挡结构与所述掺杂区在所述测试晶片表面的投影相互错开。

9、在其中一实施例中,所述沟槽隔离结构与所述掺杂区在所述测试晶片表面的投影部分交叠,所述掺杂区在所述测试晶片表面的投影覆盖相邻的所述沟槽隔离结构之间的开口在所述测试晶片表面的投影,所述光阻挡结构在所述测试晶片表面的投影位于所述掺杂区外围。

10、在其中一实施例中,所述沟槽隔离结构包括与所述光阻挡结构完全错开的第一沟槽隔离结构、与所述光阻挡结构部分重叠的第二沟槽隔离结构以及与所述光阻挡结构完全重叠的第三沟槽隔离结构中的至少之一。

11、在其中一实施例中,所述光阻挡结构包括与所述沟槽隔离结构完全错开的第一光阻挡结构、与所述沟槽隔离结构部分重叠的第二光阻挡结构以及与所述沟槽隔离结构完全重叠的第三光阻挡结构中的至少之一和/或,所述沟槽隔离结构采用浅沟槽隔离结构,所述光阻挡结构采用光刻胶。

12、在其中一实施例中,所述图像传感器包括若干呈阵列排布的尺寸小于3μm×3μm的像素单元;和/或,所述测试晶片制备得到的测试结构包括若干个测试单元,所述测试单元与图像传感器的像素单元对应;和/或,所述测试调制结构的布置方式包括所述测试调制结构占所述测试单元的比例随着所述测试单元的尺寸减小而增大。

13、在其中一实施例中,所述掺杂区包括n型掺杂层和p型掺杂层中的至少之一。

14、在其中一实施例中,所述掺杂区包括一层n型掺杂层和两层p型掺杂层,一层所述n型掺杂层位于两层所述p型掺杂层之间;和/或,所述掺杂区包括一层n型掺杂层和一层p型掺杂层,所述n型掺杂层位于所述p型掺杂层下方;和/或,所述掺杂区包括具有第一相对原子质量掺杂的第一掺杂层和小于第一相对原子质量的第二相对原子质量掺杂的第二掺杂层,所述第二掺杂层位于所述第一掺杂层上方。

15、本实用新型有益效果在于:通过在测试晶片的正面设置测试调制结构对测试晶片的掺杂进行调制,再对设有测试调制结构的测试晶片进行掺杂扩散测试,从而可以测试出测试调制结构对测试晶片中掺杂区的掺杂分布的影响,使得测试结果更加接近实际中的掺杂效果,以便于更好的对掺杂进行校准。

技术特征:

1.一种像素掺杂扩散的测试结构,其特征在于,所述测试结构包括:

2.根据权利要求1所述的像素掺杂扩散的测试结构,其特征在于,所述测试调制结构包括沟槽隔离结构和光阻挡结构中的至少一种。

3.根据权利要求2所述的像素掺杂扩散的测试结构,其特征在于,所述沟槽隔离结构延伸至所述测试晶片内,以基于位于所述测试晶片内部的所述沟槽隔离结构调制掺杂处理;和/或,所述光阻挡结构至少位于所述测试晶片上,以基于位于所述测试晶片上的所述光阻挡结构调制掺杂处理。

4.根据权利要求2所述的像素掺杂扩散的测试结构,其特征在于,所述沟槽隔离结构与所述掺杂区以及所述光阻挡结构与所述掺杂区之间的布置方式包括如下方式中的至少一种:

5.根据权利要求4所述的像素掺杂扩散的测试结构,其特征在于,所述沟槽隔离结构与所述掺杂区在所述测试晶片表面的投影部分交叠,所述掺杂区在所述测试晶片表面的投影覆盖相邻的所述沟槽隔离结构之间的开口在所述测试晶片表面的投影,所述光阻挡结构在所述测试晶片表面的投影位于所述掺杂区外围。

6.根据权利要求2所述的像素掺杂扩散的测试结构,其特征在于,所述沟槽隔离结构包括与所述光阻挡结构完全错开的第一沟槽隔离结构、与所述光阻挡结构部分重叠的第二沟槽隔离结构以及与所述光阻挡结构完全重叠的第三沟槽隔离结构中的至少之一。

7.根据权利要求2所述的像素掺杂扩散的测试结构,其特征在于,所述光阻挡结构包括与所述沟槽隔离结构完全错开的第一光阻挡结构、与所述沟槽隔离结构部分重叠的第二光阻挡结构以及与所述沟槽隔离结构完全重叠的第三光阻挡结构中的至少之一和/或,所述沟槽隔离结构采用浅沟槽隔离结构,所述光阻挡结构采用光刻胶。

8.根据权利要求1所述的像素掺杂扩散的测试结构,其特征在于,所述测试晶片制备得到的测试结构包括若干个测试单元,所述测试单元与图像传感器的像素单元对应;和/或,所述测试调制结构的布置方式包括所述测试调制结构占所述测试单元的比例随着所述测试单元的尺寸减小而增大。

9.根据权利要求1-8任一项所述的像素掺杂扩散的测试结构,其特征在于,所述掺杂区包括n型掺杂层和p型掺杂层中的至少之一。

10.根据权利要求9所述的像素掺杂扩散的测试结构,其特征在于,所述掺杂区包括一层n型掺杂层和两层p型掺杂层,一层所述n型掺杂层位于两层所述p型掺杂层之间;和/或,所述掺杂区包括一层n型掺杂层和一层p型掺杂层,所述n型掺杂层位于所述p型掺杂层下方;和/或,所述掺杂区包括具有第一相对原子质量掺杂的第一掺杂层和小于第一相对原子质量的第二相对原子质量掺杂的第二掺杂层,所述第二掺杂层位于所述第一掺杂层上方。

技术总结

本技术公开了一种像素掺杂扩散的测试结构,测试结构包括:提供测试晶片,测试晶片内设有掺杂区;测试晶片的正面设有测试调制结构,以对测试晶片的掺杂进行调制。通过在测试晶片的正面设置测试调制结构对测试晶片的掺杂进行调制,再对设有测试调制结构的测试晶片进行掺杂扩散测试,从而可以测试出测试调制结构对测试晶片中掺杂区的掺杂分布的影响,使得测试结果更加接近实际中的掺杂效果,以便于更好的对掺杂进行校准。

技术研发人员:王倩,邵泽旭

受保护的技术使用者:思特威(上海)电子科技股份有限公司

技术研发日:20231211

技术公布日:2024/10/31

- 还没有人留言评论。精彩留言会获得点赞!