半导体测试器件、半导体晶片以及迁移率测试方法与流程

本申请涉及半导体,尤其涉及一种半导体测试器件、半导体晶片以及迁移率测试方法。

背景技术:

1、半导体器件(mosfet)的元胞尺寸微缩以及迁移率提升,是进一步减小器件的导通电阻的简单方法。

2、现有的半导体器件,因为源漏极分别位于器件上下两侧,其垂直结构的特点导致其在电流路径上会有很多寄生电阻,如接触电阻、n型重掺杂层电阻、漂移区层电阻、衬底电阻等,寄生电阻的引入,特别是漂移区电阻的存在导致真实的电流减小,因此,准确表征器件迁移率是一个难点。

技术实现思路

1、本申请提供一种半导体测试器件、半导体晶片以及迁移率测试方法,能够准确表征半导体器件的迁移率。

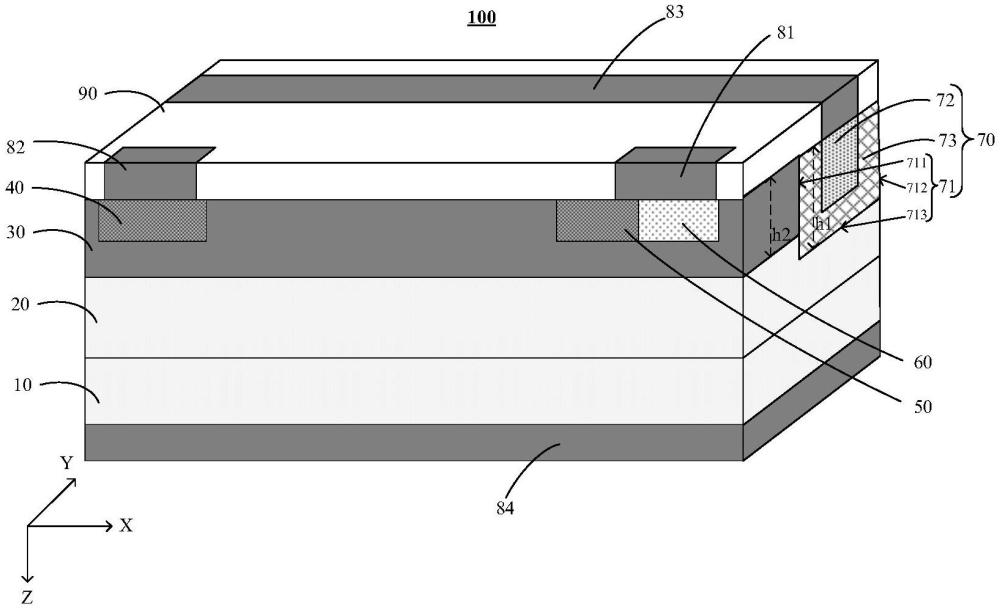

2、为解决上述技术问题,本申请采用的第一个技术方案是:提供一种半导体测试器件,用于表征沟槽型栅极结构功率器件的迁移率;包括:所述半导体测试器件包括:衬底;外延层,设置在所述衬底的表面,所述衬底和所述外延层为第一导电类型;沟槽电极,所述沟槽电极包括设置于所述外延层中的沟槽,设置于所述沟槽中的导电电极,以及设置于所述沟槽中将所述导电电极与所述外延层绝缘的电极绝缘层,所述沟槽具有沿第一方向延伸的第一侧壁、第二侧壁和一底壁,所述第一方向为平行于所述衬底的方向,所述导电电极用于接入第一电压的输出端;第一掺杂区,设置于所述外延层中且与所述第一侧壁相连,所述第一掺杂区为第二导电类型;第二掺杂区、第三掺杂区,设置于所述第一掺杂区中且与所述第一侧壁相连,并且,所述第二掺杂区和所述第三掺杂区在所述第一方向间隔设置,所述第二掺杂区和所述第三掺杂区为第一导电类型;第四掺杂区,在所述第一方向上,设置于所述第三掺杂区远离所述第二掺杂区的一侧,所述第四掺杂区分别与所述第三掺杂区和所述第一侧壁相连,所述第四掺杂区为第二导电类型,所述第四掺杂区的掺杂浓度大于第一掺杂区的掺杂浓度;第一金属层,设置于所述第三掺杂区和所述第四掺杂区的上方;所述第一金属层用于接地;第二金属层,设置于所述第二掺杂区的上方;所述第二金属层用于接入第二电压的输出端。

3、为解决上述技术问题,本申请采用的第二个技术方案是:提供一种半导体晶片,所述半导体晶片,包括:若干半导体器件区域,所述半导体器件区域中的半导体器件为沟槽型栅极结构功率器件;若干监测区域,设置有至少一个用于测试所述沟槽型栅极结构功率器件沟道迁移率的半导体测试器件,所述半导体测试器件,包括:衬底;外延层,设置在所述衬底的表面,所述衬底和所述外延层为第一导电类型;沟槽电极,所述沟槽电极包括设置于所述外延层中的沟槽,设置于所述沟槽中的导电电极,以及设置于所述沟槽中将所述导电电极与所述外延层绝缘的电极绝缘层,所述沟槽具有沿第一方向延伸的第一侧壁、第二侧壁和一底壁,所述第一方向为平行于所述衬底的方向,所述导电电极用于接入第一电压的输出端;第一掺杂区,设置于所述外延层中且与所述第一侧壁相连,所述第一掺杂区为第二导电类型;第二掺杂区、第三掺杂区,设置于所述第一掺杂区中且与所述第一侧壁相连,并且,所述第二掺杂区和所述第三掺杂区在所述第一方向间隔设置,所述第二掺杂区和所述第三掺杂区为第一导电类型;第四掺杂区,在所述第一方向上,设置于所述第三掺杂区远离所述第二掺杂区之间的一侧,所述第四掺杂区分别与所述第三掺杂区和所述第一侧壁相连,所述第四掺杂区为第二导电类型,所述第四掺杂区的掺杂浓度大于第一掺杂区的掺杂浓度;第一金属层,设置于所述第三掺杂区和所述第四掺杂区的上方;所述第一金属层用于接地;第二金属层,设置于所述第二掺杂区的上方;所述第二金属层用于接入第二电压的输出端。

4、为解决上述技术问题,本申请采用的第三个技术方案是:提供一种迁移率测试方法,应用于半导体晶片中,所述半导体晶片,包括:若干半导体器件区域,所述半导体器件区域中的半导体器件为沟槽型栅极结构功率器件;若干监测区域,设置有至少一个用于测试所述沟槽型栅极结构功率器件沟道迁移率的半导体测试器件,所述半导体测试器件,包括:衬底;外延层,设置在所述衬底的表面,所述衬底和所述外延层为第一导电类型;沟槽电极,所述沟槽电极包括设置于所述外延层中的沟槽,设置于所述沟槽中的导电电极,以及设置于所述沟槽中将所述导电电极与所述外延层绝缘的电极绝缘层,所述沟槽具有沿第一方向延伸的第一侧壁、第二侧壁和一底壁,所述第一方向为平行于所述衬底的方向,所述导电电极用于接入第一电压的输出端;第一掺杂区,设置于所述外延层中且与所述第一侧壁相连,所述第一掺杂区为第二导电类型;第二掺杂区、第三掺杂区,设置于所述第一掺杂区中且与所述第一侧壁相连,并且,所述第二掺杂区和所述第三掺杂区在所述第一方向间隔设置,所述第二掺杂区和所述第三掺杂区为第一导电类型;第四掺杂区,在所述第一方向上,设置于所述第三掺杂区远离所述第二掺杂区之间的一侧,所述第四掺杂区分别与所述第三掺杂区和所述第一侧壁相连,所述第四掺杂区为第二导电类型,所述第四掺杂区的掺杂浓度大于第一掺杂区的掺杂浓度;第一金属层,设置于所述第三掺杂区和所述第四掺杂区的上;所述第一金属层用于接地;第二金属层,设置于所述第二掺杂区的上;所述第二金属层用于接入第二电压的输出端;所述测试方法包括:所述半导体测试器件中的导电电极接收所述第一电压的输出端输出的第一电压v1,其中,所述第一电压v1大于所述沟槽电极的阈值电压vth;所述半导体测试器件的第二金属层接收所述第二电压的输出端输出的第二电压v2,其中,第二电压v2大于0v;基于所述第二电压v2,检测出所述第二金属层和/或第一金属层上的测试电流i;基于所述第一电压v1和所述阈值电压vth、所述第二电压v2和所述测试电流i,确定所述半导体测试器件的沟道迁移率μ;基于所述半导体测试器件的沟道迁移率μ,确定所述半导体晶片中所述沟槽型栅极结构功率器件的沟道迁移。

5、本申请的有益效果是,区别于现有技术,本申请提供的半导体测试器件、半导体晶片以及迁移率测试方法,半导体测试器件包括衬底、设置于衬底表面的外延层、沟槽电极、第一掺杂区、第二掺杂区、第三掺杂区、第四掺杂区、第一金属层、第二金属层;其中,沟槽电极包括设置于外延层中的沟槽、设置于沟槽内的导电电极以及将导电电极与外延层绝缘的电极绝缘层,沟槽具有沿第一方向延伸的第一侧壁、第二侧壁和一底壁,导电电极用于接入第一电压的输出端;第一掺杂区设置于外延层中且与第一侧壁相连;第二掺杂区和第三掺杂区设置于第一掺杂区中且与第一侧壁相连,并且,第二掺杂区和第三掺杂区在第一方向间隔设置;第四掺杂区在第一方向上,设置于第三掺杂区远离第二掺杂区的一侧,第四掺杂区分别与第三掺杂区和第一侧壁相连,第四掺杂区的掺杂浓度大于第一掺杂区的掺杂浓度;第一金属层设置于第三掺杂区和第四掺杂区的上方;第一金属层用于接地;第二金属层设置于第二掺杂区的上方;第二金属层用于接入第二电压的输出端。具体的,本申请提供的半导体测试器件的结构,能够使电流路径经由第二掺杂区沿沟槽电极的沟槽的第一侧壁流向第三掺杂区,消除了第一掺杂区下方的漂移区(即外延层)电阻、衬底电阻等寄生电阻对迁移率的影响,进而实现准确表征半导体器件迁移率的目的。

技术特征:

1.一种半导体测试器件,其中,所述半导体测试器件包括:

2.根据权利要求1所述的半导体测试器件,其中,所述半导体测试器件还包括:

3.根据权利要求1或2所述的半导体测试器件,其中,在测试条件下,所述第一电压被配置为大于所述沟槽电极的阈值电压,所述第二电压被配置为大于0v。

4.根据权利要求1或2所述的半导体测试器件,其中,在测试条件下,所述第一电压和所述第二电压被配置为使所述半导体测试器件导通。

5.根据权利要求1或2所述的半导体测试器件,其中,所述半导体测试器件用于测试沟槽型栅极结构功率器件的迁移率。

6.根据权利要求1所述的半导体测试器件,其中,所述第一侧壁的表面粗糙度小于1nm。

7.根据权利要求1所述的半导体测试器件,其中,在第三方向上,与所述第一侧壁相接所述电极绝缘层的宽度为1~200nm,所述第三方向为所述第一掺杂区到所述沟槽电极的方向。

8.根据权利要求1所述的半导体测试器件,其中,在第二方向上,所述沟槽在所述外延层中的深度大于所述第一掺杂区在所述外延层内的深度,其中,所述第二方向为所述外延层到所述衬底的方向。

9.根据权利要求1所述的半导体测试器件,其中,在所述第一方向上,所述第二掺杂区与所述第三掺杂区之间的距离为40~1000μm。

10.根据权利要求8所述的半导体测试器件,其中,所述第一掺杂区沿所述第二方向的第一深度为0.3~8μm。

11.根据权利要求1所述的半导体测试器件,其中,所述第一金属层和所述第二金属层的电阻率小于1e-5ω*cm2。

12.一种半导体晶片,其中,所述半导体晶片,包括:

13.根据权利要求12所述的半导体晶片,其中,所述半导体测试器件还包括:

14.根据权利要求12所述的半导体晶片,其中,所述第一侧壁的表面粗糙度小于1nm。

15.根据权利要求12所述的半导体晶片,其中,在第三方向上,与所述第一侧壁相接的所述电极绝缘层的宽度为1~200nm,所述第三方向为所述第一掺杂区到所述沟槽电极的方向。

16.根据权利要求15所述的半导体晶片,其中,在第二方向上,所述沟槽在所述外延层中的深度大于所述第一掺杂区在所述外延层内的深度,其中,所述第二方向为所述外延层到所述衬底的方向。

17.根据权利要求12所述的半导体晶片,其中,在所述第一方向上,所述第二掺杂区与所述第三掺杂区之间的第一距离为40~1000μm。

18.根据权利要求16所述的半导体晶片,其中,所述第一掺杂区沿所述第二方向的第一深度为0.3~8μm。

19.一种迁移率测试方法,其中,应用于半导体晶片中,所述半导体晶片,包括:若干半导体器件区域,所述半导体器件区域中的半导体器件为沟槽型栅极结构功率器件;若干监测区域,设置有至少一个用于测试所述沟槽型栅极结构功率器件沟道迁移率的半导体测试器件,所述半导体测试器件,包括:衬底;外延层,设置在所述衬底的表面,所述衬底和所述外延层为第一导电类型;沟槽电极,所述沟槽电极包括设置于所述外延层中的沟槽,设置于所述沟槽中的导电电极,以及设置于所述沟槽中将所述导电电极与所述外延层绝缘的电极绝缘层,所述沟槽具有沿第一方向延伸的第一侧壁、第二侧壁和一底壁,所述第一方向为平行于所述衬底的方向,所述导电电极用于接入第一电压的输出端;第一掺杂区,设置于所述外延层中且与所述第一侧壁相连,所述第一掺杂区为第二导电类型;第二掺杂区、第三掺杂区,设置于所述第一掺杂区中且与所述第一侧壁相连,并且,所述第二掺杂区和所述第三掺杂区在所述第一方向间隔设置,所述第二掺杂区和所述第三掺杂区为第一导电类型;第四掺杂区,在所述第一方向上,设置于所述第三掺杂区远离所述第二掺杂区之间的一侧,所述第四掺杂区分别与所述第三掺杂区和所述第一侧壁相连,所述第四掺杂区为第二导电类型,所述第四掺杂区的掺杂浓度大于第一掺杂区的掺杂浓度;第一金属层,设置于所述第三掺杂区和所述第四掺杂区的上;所述第一金属层用于接地;第二金属层,设置于所述第二掺杂区的上;所述第二金属层用于接入第二电压的输出端;

20.根据权利要求19所述的方法,其中,沿所述第一方向,所述第二掺杂区与所述第三掺杂区之间的所述第一掺杂区被定义为沟道所在区,所述导电电极在所述第一侧壁的投影区与所述沟道所在区的重叠区域被定义为沟道区;

21.根据权利要求20所述的方法,其中,所述方法还包括:

技术总结

本申请提供一种半导体测试器件、半导体晶片以及迁移率测试方法,半导体测试器件包括衬底、设置于衬底表面的外延层、沟槽电极、第一掺杂区、第二掺杂区、第三掺杂区、第四掺杂区、第一金属层、第二金属层;沟槽电极包括设置于外延层中的沟槽,设置于沟槽中的导电电极和电极绝缘层,沟槽具有沿第一方向延伸的第一侧壁、第二侧壁和一底壁,第一掺杂区、第二掺杂区、第三掺杂区及第四掺杂区设置于沟槽电极的一侧且与第一侧壁相连,第一金属层设置于第三掺杂区和第四掺杂区的上方;第一金属层用于接地;第二金属层设置于第二掺杂区的上方;第二金属层用于接入第二电压的输出端。该结构使电流路径不经过外延层和衬底,实现准确表征器件迁移率的目的。

技术研发人员:韩忠霖,吴怡清,邱志祥,刘冰冰

受保护的技术使用者:厦门市三安集成电路有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!