半导体模块、半导体装置以及车辆的制作方法

本发明涉及半导体模块、半导体装置以及车辆。

背景技术:

1、在逆变器装置等电力转换装置中利用的半导体模块具备igbt(insulated gatebipolar transistor:绝缘栅双极晶体管)、功率mosfet(metal oxide semiconductorfield effect transistor:金属氧化物半导体场效应晶体管)、fwd(free wheelingdiode:续流二极管)等半导体元件。

2、在这种半导体模块中,将在布线板搭载有半导体元件等电路部件的电路板收纳于壳体内之后,向壳体内填充密封材料而将电路板密封。

3、另外,在这种半导体模块中,例如为了防止电路板中的半导体元件等电路部件、布线构件等的由腐蚀性气体导致的腐蚀、由尘埃、水分等导致的绝缘性的降低,而采取了各种对策。

4、例如,在专利文献1中记载了一种电力转换装置,该电力转换装置具备:功率电路模块,其通过在引线端子被引出到外部的状态下将搭载有功率半导体的功率电路基板利用绝缘树脂密封而成;以及控制电路模块,其通过在连接部暴露于外部的状态下将功率半导体的驱动、控制用的控制电路基板利用绝缘树脂密封填埋而成,功率电路模块的引线端子安装于控制电路模块的连接部并电连接,并且以机械的方式一体化。

5、另外,例如,在专利文献2中,记载有在将壳体内的功率器件以及控制电路密封的有机硅凝胶的上表面侧还填充有环氧树脂的半导体装置。

6、现有技术文献

7、专利文献

8、专利文献1:日本特开2006-121861号公报

9、专利文献2:日本特开平7-335800号公报

技术实现思路

1、发明要解决的问题

2、在上述的半导体模块的壳体中,有时将包围搭载于电路板的半导体元件等电路部件的侧面部与在电路板的上方成为盖的盖部一体化,并在盖部设有注入密封材料的注入孔。在使用这样的壳体的情况下,在盖上电路板之上的壳体之后,自注入孔注入密封材料而将电路板的电路部件等密封。

3、在使用了具有盖部的壳体的半导体模块中,有时利用设于壳体的靠收纳电路部件的空间侧的面的分隔件、梁等突出的部分和自注入孔注入的密封材料,将收纳电路部件的空间分割成两个以上的空间而确保端子间的绝缘。然而,在这样的半导体模块中,在注入密封材料而将收纳电路部件的空间分割成两个以上的空间之后,例如难以将用于防止由腐蚀性气体导致的腐蚀的追加的密封材料自注入孔注入并均匀地填充于分割出的各空间。

4、在一个方面,本发明的目的在于,减少使用了一体地设有盖部的壳体的半导体模块中的密封材料的填充不均。

5、用于解决问题的方案

6、一技术方案的半导体模块包括:基座,其搭载有电路板;壳体,其覆盖搭载于所述基座的所述电路板,该壳体具有包围所述电路板的外周的侧面部和位于所述电路板的上方的盖部;多个导体板,其各自与所述电路板的导体图案电连接,并经由设于所述壳体的狭缝而延伸到所述壳体的外部;以及密封材料,其将所述电路板密封,所述壳体具有分隔部,该分隔部配置于由所述盖部、所述侧面部以及所述电路板包围的区域,并配置于所述多个导体板之间而使所述多个导体板之间绝缘,从与所述多个导体板和所述分隔部各自平行地延伸的面垂直的方向观察时,所述分隔部在与所述多个导体板不重叠的位置具有缺口区间,从而与所述多个导体板不重叠的第2部分的高度低于与所述多个导体板重叠的第1部分的高度。

7、发明的效果

8、根据上述技术方案,能够减少使用了一体地设有盖部的壳体的半导体模块中的密封材料的填充不均。

技术特征:

1.一种半导体模块,其特征在于,

2.根据权利要求1所述的半导体模块,其特征在于,

3.根据权利要求1所述的半导体模块,其特征在于,

4.根据权利要求1所述的半导体模块,其特征在于,

5.根据权利要求1所述的半导体模块,其特征在于,

6.根据权利要求1所述的半导体模块,其特征在于,

7.一种半导体装置,其特征在于,

8.一种车辆,其特征在于,

技术总结

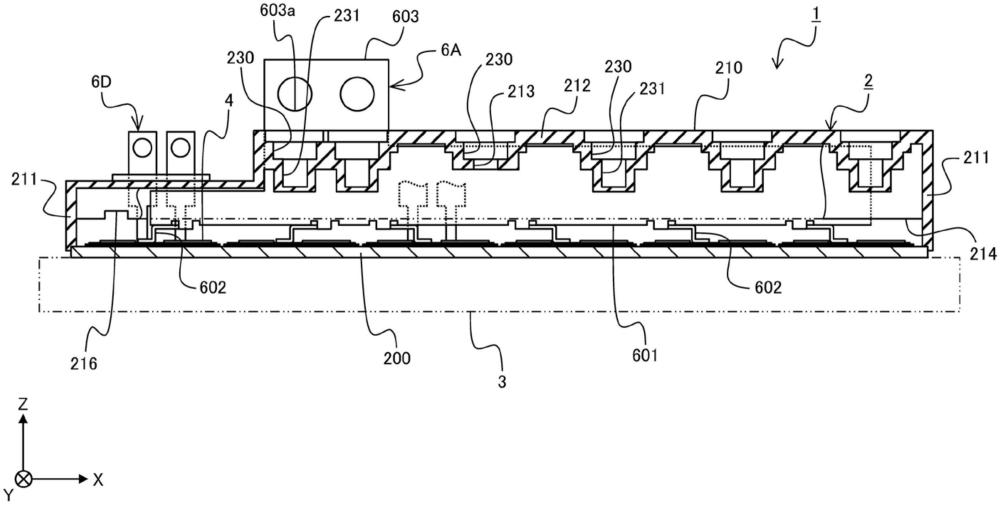

减少使用了一体地设有盖部的壳体的半导体模块中的密封材料的填充不均。半导体模块(2)包括:壳体(210),其覆盖搭载于基座(200)的电路板(4),该壳体具有包围电路板的外周的侧面部(211)和位于电路板的上方的盖部(212);多个导体板(6A~6D),其各自与电路板的导体图案电连接,并经由设于壳体的狭缝(220)而延伸到壳体的外部;以及密封材料(701、702),其将电路板密封,壳体具有分隔部(214、215),该分隔部配置于由盖部、侧面部以及电路板包围的区域,并配置于多个导体板之间而使多个导体板之间绝缘,分隔部在与多个导体板不重叠的位置具有缺口区间(216、217),从而与多个导体板不重叠的部分的高度低于与多个导体板重叠的部分的高度。

技术研发人员:伊藤太一,小平悦宏

受保护的技术使用者:富士电机株式会社

技术研发日:

技术公布日:2024/10/28

- 还没有人留言评论。精彩留言会获得点赞!