半导体装置和半导体装置的制造方法与流程

本发明涉及半导体装置和半导体装置的制造方法。

背景技术:

1、在固体摄像装置中密集地布置诸如光接收元件等电控元件的情况下,需要使每个元件的布置面积小型化。为了实现固体摄像装置的进一步小型化,在一些情况下,将配线、逻辑电路等布置在与布置有光接收元件的像素阵列的半导体层不同的半导体层中,并且可以采用其中通过混合接合将这些半导体层层叠以适当地彼此电气连接的三维结构。

2、为了提高要拍摄的图像的分辨率或者为了使摄像元件所属的半导体芯片小型化,需要进一步使包括光接收元件的光接收像素小型化。在以高密度布置光接收像素的情况下,用于半导体层间的连接的连接面以及到该连接面的配线(信号线)也需要微细化。因此,还需要使配线之间的氧化物膜的宽度微细化,但是该微细化可能导致诸如寄生电容等问题。为了避免这种情况,例如,可以想到在配线之间布置接地的导体配线(屏蔽)。

3、然而,当适当地布置屏蔽(shield)时,存在这样的可能性:在将半导体层彼此连接的时刻,设置为一个半导体层的信号线的接触面的焊盘可能与另一半导体层的屏蔽接触。这会导致所要求的对准精度会非常高的问题。

4、引用文献列表

5、专利文件

6、专利文件1:日本专利申请特开第2020-088380号公报

技术实现思路

1、发明要解决的技术问题

2、因此,本公开提供一种半导体装置,其降低了布置屏蔽所要求的对准精度。

3、技术问题的解决方案

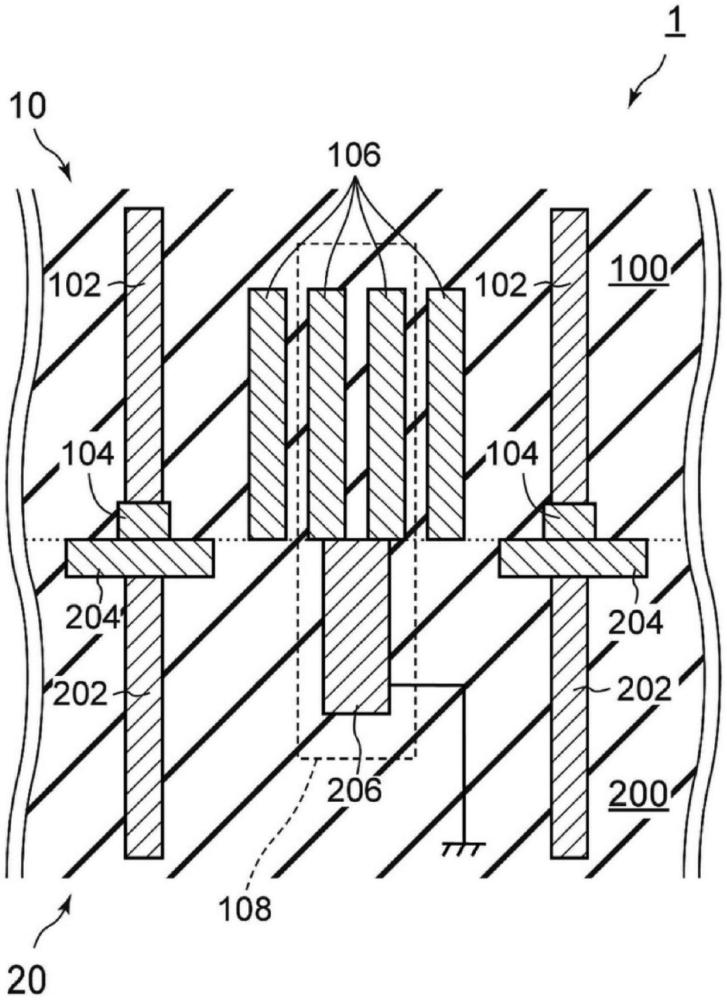

4、根据一个实施方案,半导体装置包括第一基板和第二基板。所述第一基板包括:

5、多个彼此绝缘的第一配线;

6、连接至所述第一配线并且彼此绝缘的多个第一电极;和

7、第一屏蔽电极,所述第一屏蔽电极与所述第一电极绝缘并且至少布置在所述多个第一电极之间。

8、所述第二基板包括:

9、多个彼此绝缘的第二配线;

10、连接至所述第二配线并且彼此绝缘的多个第二电极;和

11、第二屏蔽电极,所述第二屏蔽电极与所述第二电极绝缘并且至少布置在所述多个第二电极之间。

12、所述第一电极和所述第二电极通过混合接合而被电气连接,并且

13、所述第一屏蔽电极和所述第二屏蔽电极通过混合接合而被电气连接以形成第一屏蔽。

14、所述第一基板在所述第一屏蔽与所述第一配线之间,或者在所述第一屏蔽与所述第一配线和所述第一电极之间还可以包括第二屏蔽,所述第二屏蔽是与所述第一配线、所述第一电极、所述第一屏蔽以及在所述第一基板与所述第二基板之间的接合面绝缘的导体。

15、所述第二屏蔽可以接地。

16、所述第二屏蔽可以布置在绝缘体中,从而不连接至任何电位。

17、所述第一屏蔽的电位可以被控制为预定电位。

18、所述第一屏蔽可以接地。

19、所述第一屏蔽可以被控制为在所述第二基板侧的预定电位。

20、所述第一屏蔽可以接地。

21、所述多个第一屏蔽电极可以布置为在相邻的第一电极之间是绝缘的,并且所述第二屏蔽电极可以电气连接至所述多个第一屏蔽电极中的至少一个。

22、在所述第一基板与所述第二基板之间的接合面处,所述第一屏蔽电极之间的距离可以比所述第二屏蔽电极的宽度短。

23、在所述第一基板与所述第二基板之间的接合面处,所述第一电极的宽度可以比所述第二电极的宽度窄,并且所述第二电极与所述第二屏蔽电极之间的距离可以比所述第一电极的宽度短。

24、所述第一配线、所述第一电极、所述第一屏蔽电极、所述第二配线、所述第二电极、所述第二屏蔽电极以及所述第一屏蔽可以由铜形成。

25、所述第二屏蔽可以由铜形成。

26、所述第一基板可以包括多个像素,各像素包括光电二极管,并且各所述像素可以经由所述第一配线连接至所述第一电极。

27、所述第二基板可以包括处理从所述像素输出的信号的多个像素电路,并且各像素电路可以经由所述第二配线连接至所述第二电极。

28、所述混合接合可以是其中在所述第一基板的接合面上的层间绝缘膜中形成的电极和在所述第二基板的接合面上的层间绝缘膜中形成的电极的至少一部分彼此直接连接的接合。

29、根据一个实施方案,半导体装置的制造方法是通过层叠第一基板和第二基板而形成的半导体装置的制造方法,所述方法包括:

30、在所述第一基板上形成多个第一配线、连接至所述第一配线的多个第一电极以及在相邻的所述第一电极之间与所述第一配线和所述第一电极绝缘的多个第一屏蔽电极;

31、在所述第二基板上形成多个第二配线、连接至所述第二配线的多个第二电极以及在相邻的所述第二电极之间与所述第二配线和所述第二电极绝缘的所述第二屏蔽电极;和

32、电气连接所述第一电极和所述第二电极以及所述第一电极中的至少一者和所述第二屏蔽电极。

33、所述第一基板的电极和所述第二基板的电极可以通过混合接合而被电气连接。

34、所述第一基板和所述第二基板可以以芯片上芯片(coc)、晶片上芯片(cow)或晶片上晶片(wow)的形式接合。

35、在所述第一基板上可以形成有光电二极管,在所述第二基板上可以形成有像素电路,并且经由所述第一配线连接至所述光电二极管的所述第一电极和经由所述第二配线连接至所述像素电路的所述第二电极可以电气连接。

技术特征:

1.一种半导体装置,其包括:

2.根据权利要求1所述的半导体装置,其中

3.根据权利要求2所述的半导体装置,其中

4.根据权利要求2所述的半导体装置,其中

5.根据权利要求1所述的半导体装置,其中

6.根据权利要求5所述的半导体装置,其中

7.根据权利要求2所述的半导体装置,其中

8.根据权利要求7所述的半导体装置,其中

9.根据权利要求1所述的半导体装置,其中

10.根据权利要求9所述的半导体装置,其中

11.根据权利要求10所述的半导体装置,其中

12.根据权利要求1所述的半导体装置,其中

13.根据权利要求3所述的半导体装置,其中

14.根据权利要求1所述的半导体装置,其中

15.根据权利要求14所述的半导体装置,其中

16.根据权利要求1所述的半导体装置,其中

17.一种通过层叠第一基板和第二基板而形成的半导体装置的制造方法,所述方法包括:

18.根据权利要求17所述的半导体装置的制造方法,其中

19.根据权利要求17所述的半导体装置的制造方法,其中

20.根据权利要求17所述的半导体装置的制造方法,其中:

技术总结

[技术问题]为了抑制屏蔽布置中所需的对准精度。[技术方案]一种半导体装置,包括第一基板和第二基板。所述第一基板包括:彼此绝缘的多个第一配线;彼此绝缘并且分别连接至所述第一配线的多个第一电极;以及第一屏蔽电极,所述第一屏蔽电极至少布置在所述多个第一电极之间并且与所述第一电极绝缘。所述第二基板包括:彼此绝缘的多个第二配线;彼此绝缘并且分别连接至所述第二配线的多个第二电极;以及第二屏蔽电极,所述第二屏蔽电极至少布置在所述多个第二电极之间并且与所述第二电极绝缘。所述第一电极和所述第二电极通过混合接合而被电气连接。所述第一屏蔽电极和所述第二屏蔽电极通过混合接合而被电气连接并且形成第一屏蔽。

技术研发人员:藤井宣年,斋藤卓,金口时久,盐山正真

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/10/24

- 还没有人留言评论。精彩留言会获得点赞!