蚀刻组成物的制作方法

本申请有关于一种蚀刻组成物及使用蚀刻组成物的方法。特别是,本申请有关于可在其他暴露或底层材料,如金属导体(如,铜)、栅极材料(如,sige)、阻挡材料、绝缘材料(如,低k介电材料)的存在下,选择性地蚀刻硅的蚀刻组成物。

背景技术:

1、半导体工业一直快速地缩小微电子装置、硅芯片、液晶显示器、微机电系统(mems,micro electro mechanical system)、印刷线路板等中的电子电路及电子组件的尺寸并增加密度。其中的集成电路被分层或堆叠,每个电路层之间的绝缘层厚度不断减小,特征尺寸越来越小。随着特征尺寸的缩小,图案变得更小,并且装置性能参数更紧密且更可靠。因此,迄今为止可以容忍的各种问题,不再能够被容忍或由于较小的特征尺寸而成为更加严重的问题。

2、在先进集成电路的生产中,为了使与更高密度相关的问题最小化并优化性能,已经采用了高k及低k绝缘体以及各种阻挡层材料。

3、硅(si)可用于半导体装置、液晶显示器、mems(微机电系统)、印刷线路板等的制造。例如,其可用作制造多栅极装置,如多栅极场效电晶体(fet,field effecttransistor)(如,栅极全环绕fet(gaa fet))的制程中的牺牲材料。特别是,可以形成交替的硅(si)与硅锗合金(sige)层的外延堆(即,外延生长堆),其中si层是牺牲层,而sige层是沟道层。该si层之后可通过选择性蚀刻(例如通过湿法蚀刻方法)去除,由于该牺牲层的材料组成与衬底材料组成相似,蚀刻也可能无意地在大块衬底中产生沟槽。随后,可将sige层形成在悬挂在沟槽上的纳米线沟道中。然后,在sige纳米线沟道周围及衬底的凹陷沟槽上设置薄栅极介电质。然后在介电质上设置金属,以形成gaa mosfet的金属栅极电极。

技术实现思路

1、在半导体装置的建构中,经常需要蚀刻硅(si)。在si的各种用途和装置环境中,在蚀刻此材料的同时会有其它层与其接触或以其它方式暴露。在这些其它材料(如,金属导体、介电质、沟道材料、栅极材料及硬掩膜)存在的情况下,通常需要高度选择性的si蚀刻,以达到装置良率及较长的寿命。

2、本申请有关相对于存在半导体装置中的硬掩膜层、栅极材料(如,sige、sin或siox)、及/或低k介电层(如,sin、siox、碳掺杂氧化物或sico),选择性地蚀刻si(如,多晶硅)的组成物及方法。更具体地,本申请有关相对于siox及/或sin,选择性地蚀刻si的组成物及方法。

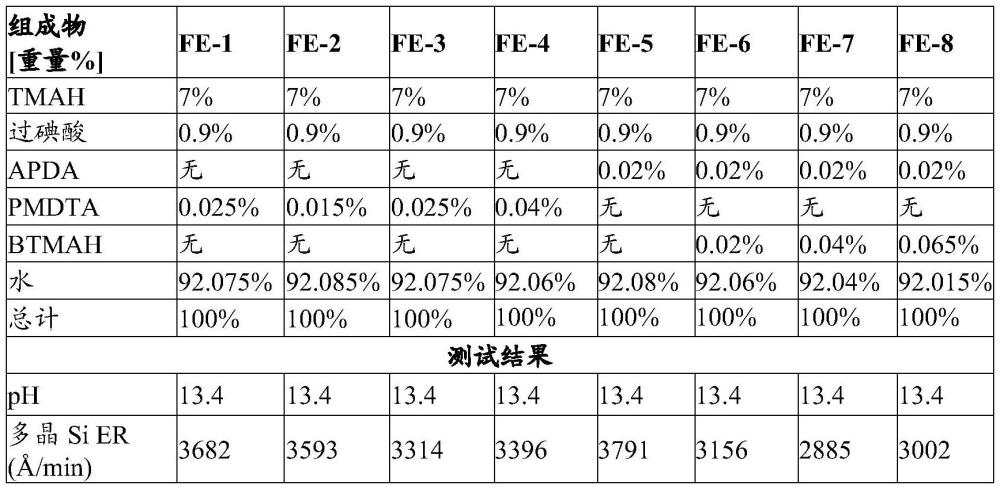

3、一方面,本申请的特征在于一种蚀刻组成物,其包括至少一种氢氧化季铵或其盐、至少一种氧化剂、至少一种多胺及水,其中该组成物具有至少约13的ph。

4、另一方面,本申请的特征在于一种方法,其包括使支撑含si形貌体的半导体衬底与本文所述的蚀刻组成物接触,以基本上去除该含si形貌体。

5、又一方面,本申请的特征在于一种由上述方法形成的物品,其中该物品是半导体装置(如,集成电路)。

技术特征:

1.一种蚀刻组成物,包括:

2.如权利要求1所述的组成物,其中,所述至少一种氢氧化季铵或其盐包括氢氧化四烷铵或其盐。

3.如权利要求1所述的组成物,其中,所述至少一种氢氧化季铵或其盐包括氢氧化四甲铵、氢氧化四乙铵、氢氧化四丙铵、氢氧化四丁铵、氢氧化苯甲基三甲铵、氢氧化甲基三乙铵、氢氧化乙基三甲铵、氢氧化二甲基二乙铵、氢氧化2-羟乙基三甲铵、氢氧化四乙醇铵、氢氧化苯甲基三乙铵、氢氧化苯甲基三丁铵、氢氧化十六烷基三甲铵,或其盐。

4.如权利要求1所述的组成物,其中,所述至少一种氢氧化季铵或其盐的量占该组成物的约0.1重量%至约20重量%。

5.如权利要求1所述的组成物,其中,所述至少一种氧化剂包括过碘酸、过氯酸或过氧化氢。

6.如权利要求1所述的组成物,其中,所述至少一种氧化剂的量占该组成物的约0.01重量%至约5重量%。

7.如权利要求1所述的组成物,其中,所述至少一种多胺包括二胺、三胺或包括至少二个胺基的烷醇胺。

8.如权利要求1所述的组成物,其中,所述至少一种多胺包括n-(3-胺丙基)-二乙醇胺或五甲基二乙烯三胺。

9.如权利要求1所述的组成物,其中,所述至少一种多胺的量占该组成物的约0.001重量%至约1重量%。

10.如权利要求1所述的组成物,其中,所述水的量占该组成物的约70重量%至约99重量%。

11.如权利要求1所述的组成物,其中,所述组成物具有最高约14的ph。

12.如权利要求1所述的组成物,其中,所述组成物基本上不含有机溶剂、季铵盐以外的盐或腐蚀抑制剂。

13.如权利要求1所述的组成物,其中,所述组成物由至少一种氢氧化季铵或其盐、至少一种氧化剂、至少一种多胺及水组成。

14.一种方法,包括:

15.如权利要求14的方法,其中,在所述半导体衬底的表面形成图案,及所述含si形貌体是该图案的一部分。

16.如权利要求14的方法,其中,所述方法基本上不会去除sin或siox。

17.一种由如权利要求14的方法形成的物品,其中,所述物品是半导体装置。

18.如权利要求17的物品,其中,所述半导体装置是集成电路。

技术总结

本申请是针对蚀刻组成物,其可用于如选择性地从半导体衬底上去除硅,作为多步骤半导体制程中的中间步骤。更具体地,本申请涉及相对于SiOx及/或SiN,选择性地化学蚀刻Si的组成物及方法。

技术研发人员:D·迪内加,T·多瑞

受保护的技术使用者:富士胶片电子材料美国有限公司

技术研发日:

技术公布日:2024/11/26

- 还没有人留言评论。精彩留言会获得点赞!