具有增大接触面积的自对准背面接触的制作方法

背景技术:

1、本发明一般涉及半导体制造领域,尤其涉及背面接触。

2、互补金属氧化物半导体(cmos)技术通常用于作为先进集成电路(下文简称“ic”)的一部分的场效应晶体管(下文简称“fet”),所述先进集成电路诸如中央处理单元(下文简称“cpu”)、存储器、存储器件等。随着对减小晶体管器件的尺寸的需求的持续,纳米片fet有助于实现更小的fet器件占用面积,同时保持fet器件的性能。纳米片器件包含一层或多层半导体沟道材料部分,所述半导体沟道材料部分具有基本上小于其宽度的垂直厚度。纳米片fet包括在一对源极/漏极外延区之间延伸的多个堆叠的纳米片。所述器件可以是全环绕栅极器件或晶体管,其中栅极围绕纳米片沟道的一部分。

技术实现思路

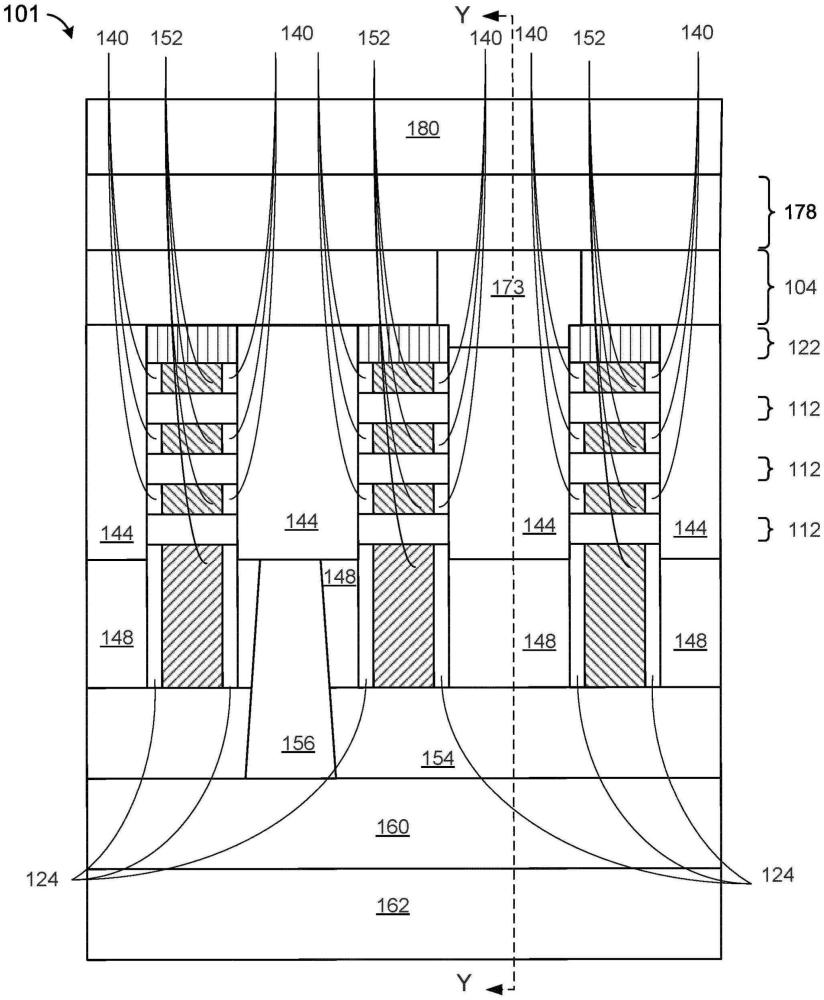

1、根据实施例,提供了一种半导体器件。所述半导体器件包括:第一源漏区,其与衬底上的第一晶体管相邻;第二源漏区,其与衬底上的第二晶体管相邻;上源漏接触,其垂直对准第一源漏区上方并且电连接至第一源漏区;以及底部源漏接触,其垂直对准第二源漏区下方并且电连接至第二源漏区,其中底部源漏接触和上源漏接触位于所述半导体器件的相对侧上,其中底部源漏接触的水平表面与围绕第二源漏区的介电侧间隔体的水平表面相邻,其中底部源漏接触的宽度比第二源漏的宽度更宽。

2、根据实施例,提供了一种半导体器件。所述半导体器件包括第一源漏区和底部源漏接触,所述底部源漏接触垂直对准第一源漏区下方并且电连接至第一源漏区,其中底部源漏接触围绕第二源漏区的垂直侧。

3、根据实施例,提供了一种方法。所述方法包括在衬底上形成第一纳米片堆叠和第二纳米片堆叠,形成到与第一纳米片堆叠相邻的第一源漏区的上水平表面的顶部源漏接触,在第一纳米片堆叠和第二纳米片堆叠上方的衬底上表面接合载体晶片,以及形成到与第二纳米片堆叠相邻的第二源漏区的下水平表面的底部源漏接触,底部源漏接触和第二源漏区垂直对准,其中底部源漏接触围绕第二源漏区的垂直侧。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中

3.根据权利要求1所述的半导体器件,其中

4.根据权利要求1所述的半导体器件,还包括:

5.根据权利要求5所述的半导体器件,还包括:

6.一种方法,包括:

7.根据权利要求6所述的方法,其中

8.根据权利要求7所述的方法,其中

9.根据权利要求6所述的方法,还包括:

10.根据权利要求9所述的方法,其中

11.根据权利要求6所述的方法,还包括:

12.根据权利要求6所述的方法,还包括:

13.根据权利要求6所述的方法,其中

14.根据权利要求6所述的方法,还包括:

15.根据权利要求6所述的方法,还包括:

技术总结

与第一晶体管相邻的第一源漏区、与第二晶体管相邻的第二源漏区、在第一源漏区上方的上源漏接触、在第二源漏区下方的底部源漏接触,底部源漏接触和上源漏接触在相对两侧上,底部源漏接触的水平表面与围绕第二源漏区的介电侧间隔体的水平表面相邻。在实施例中,底部源漏接触围绕源漏区的垂直侧。一种方法,包括形成第一和第二纳米片堆叠,形成与第一纳米片堆叠相邻的第一源漏区的顶部源漏接触,形成与第二纳米片堆叠相邻的第二源漏区的下水平表面的底部源漏接触。

技术研发人员:谢瑞龙,崔起植,王俊利,S·戈什,J·福罗吉尔,成敏圭,T·斯坦达尔特,N·J·劳贝特,卜惠明

受保护的技术使用者:国际商业机器公司

技术研发日:

技术公布日:2025/1/2

- 还没有人留言评论。精彩留言会获得点赞!