半导体器件的制作方法

本发明的实施方式之一涉及半导体器件。

背景技术:

1、近来,代替非晶硅、低温多晶硅及单晶硅而将氧化物半导体用于沟道的晶体管的开发在不断发展(例如,专利文献1及2)。氧化物半导体用于沟道的晶体管与非晶硅用于沟道的晶体管同样地,以简单的构造且以低温工艺形成。已知与非晶硅用于沟道的晶体管相比,氧化物半导体用于沟道的晶体管具有更高的移动度,截止电流非常低。

2、近年来,显示装置的像素尺寸缩小化在不断发展。与像素尺寸的缩小化相伴,正在研究布线宽度、晶体管尺寸的缩小化。但是,上述缩小化存在极限,起因于构成像素电路的金属层及半导体层的配置而开口率变小。因而,正在进行即使晶体管尺寸小也能够获得足以驱动像素电路的特性的、将在沟道中使用了氧化物半导体层的晶体管用于像素电路的晶体管的开发。现有技术文献

3、专利文献

4、专利文献1:日本特开2014-146819号公报

5、专利文献2:日本特开2015-159315号公报

技术实现思路

1、发明要解决的课题

2、在低温多晶硅作为沟道使用的晶体管中,无法使硅层与作为像素电极使用的透明导电层(例如,氧化铟及氧化锡的混合物(ito))直接接触。因此,需要在硅层与透明导电层之间设置金属层的基座。若这样的基座配置于像素的显示区域,则存在像素的开口率降低的问题。关于这种接触构造的技术思想在氧化物半导体作为沟道使用的晶体管中也通用,通常使用将透明导电层形成在金属层的基座之上的构成。此外,即使是氧化物半导体层作为沟道使用的晶体管,在透明导电层与源极区域及漏极区域的氧化物半导体层直接相接的构造中,根据制造工艺而存在氧化物半导体层与透明导电层之间的接触电阻会变高的情况。

3、本发明的实施方式之一以不降低半导体器件的电气特性而增大工艺余量(process margin)为课题之一。

4、用于解决课题的手段

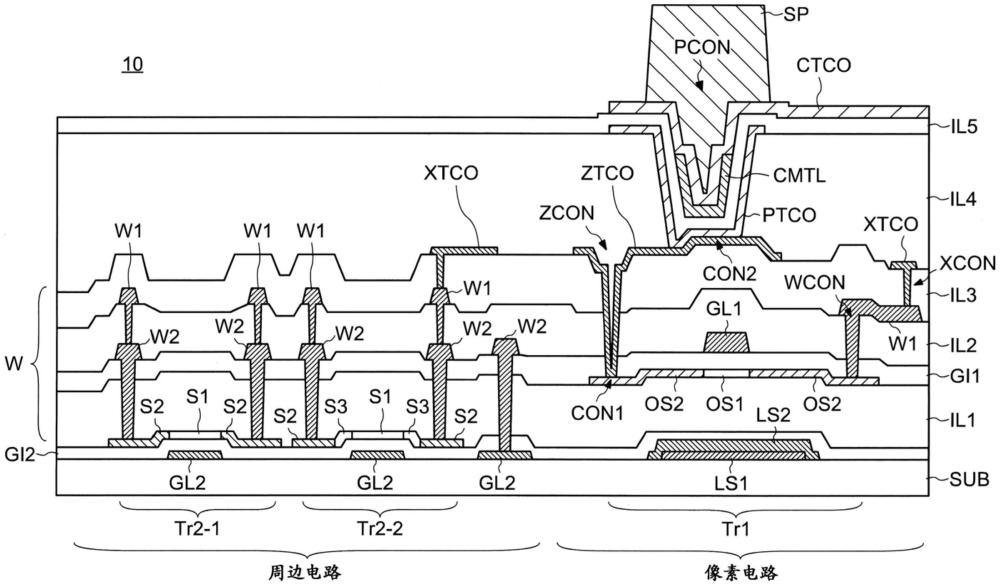

5、本发明一个实施方式涉及的半导体器件包含:氧化物半导体层,其包含多晶构造;栅电极,其与所述氧化物半导体层相对;所述氧化物半导体层与所述栅电极之间的栅极绝缘层;第1透明导电层,其与所述氧化物半导体层连接;和第2透明导电层,其设置在与所述第1透明导电层的同一层、并与所述第1透明导电层分离,所述第1透明导电层的结晶性与所述第2透明导电层的结晶性不同。

技术特征:

1.半导体器件,其包含:

2.根据权利要求1所述的半导体器件,其中,所述第1透明导电层及所述第2透明导电层分别包含铟及锡。

3.根据权利要求1所述的半导体器件,其中,所述氧化物半导体层包含含有铟的两种以上的金属,

4.根据权利要求1所述的半导体器件,其中,所述栅电极、所述第1透明导电层及所述第2透明导电层设置在所述氧化物半导体层的上方。

5.根据权利要求1所述的半导体器件,其进一步包含:第1绝缘层,其设置在所述氧化物半导体层及所述栅电极的上方、并设有第1开口;

6.根据权利要求1所述的半导体器件,其进一步包含与所述第1透明导电层及所述第2透明导电层的下表面相接的绝缘层。

7.半导体器件,其包含:

8.根据权利要求7所述的半导体器件,其中,所述第1透明导电层包含铟及锡。

9.根据权利要求7所述的半导体器件,其中,所述氧化物半导体层包含含有铟的两种以上的金属,

10.根据权利要求7所述的半导体器件,其中,所述栅电极及所述第1透明导电层设置在所述氧化物半导体层的上方。

11.根据权利要求7所述的半导体器件,其进一步包含:

12.根据权利要求7所述的半导体器件,其中,所述第1区域中的所述第1透明导电层与所述第2区域中的所述第1透明导电层连续。

技术总结

本发明涉及半导体器件。本发明能够不降低半导体器件的电气特性而增大工艺余量。半导体器件包含:氧化物半导体层,其包含多晶构造;栅电极,其与所述氧化物半导体层相对;所述氧化物半导体层与所述栅电极之间的栅极绝缘层;第1透明导电层,其与所述氧化物半导体层连接;和第2透明导电层,其设置在与所述第1透明导电层的同一层、并与所述第1透明导电层分离,所述第1透明导电层的结晶性与所述第2透明导电层的结晶性不同。

技术研发人员:渡部将弘,渡壁创,津吹将志,佐佐木俊成,望月真里奈,田丸尊也,小野寺凉

受保护的技术使用者:株式会社日本显示器

技术研发日:

技术公布日:2024/7/29

- 还没有人留言评论。精彩留言会获得点赞!