一种半导体结构及其制造方法

本发明涉及半导体制造,特别涉及一种半导体结构及其制造方法。

背景技术:

1、在半导体产品中,pmos器件所受到的压应力越大,越有利于提升pmos器件的驱动电流。而nmos器件所受到的拉应力最大,越有利于提升nmos器件的驱动电流。其中,采用锗硅(sige)外延技术可以加大pmos器件的压应力。

2、在锗硅外延工艺中,不可避免地会使用到光刻胶。而图案负载大易导致pmos器件的蚀刻损伤,因此pmos器件成型质量差,半导体产品的稳定性变差。

技术实现思路

1、本发明的目的在于提供一种半导体结构及其制造方法,能够提升半导体结构的成型质量和制程良率,并且更有利于提升pmos器件的驱动电流。

2、为解决上述技术问题,本发明是通过以下技术方案实现的:

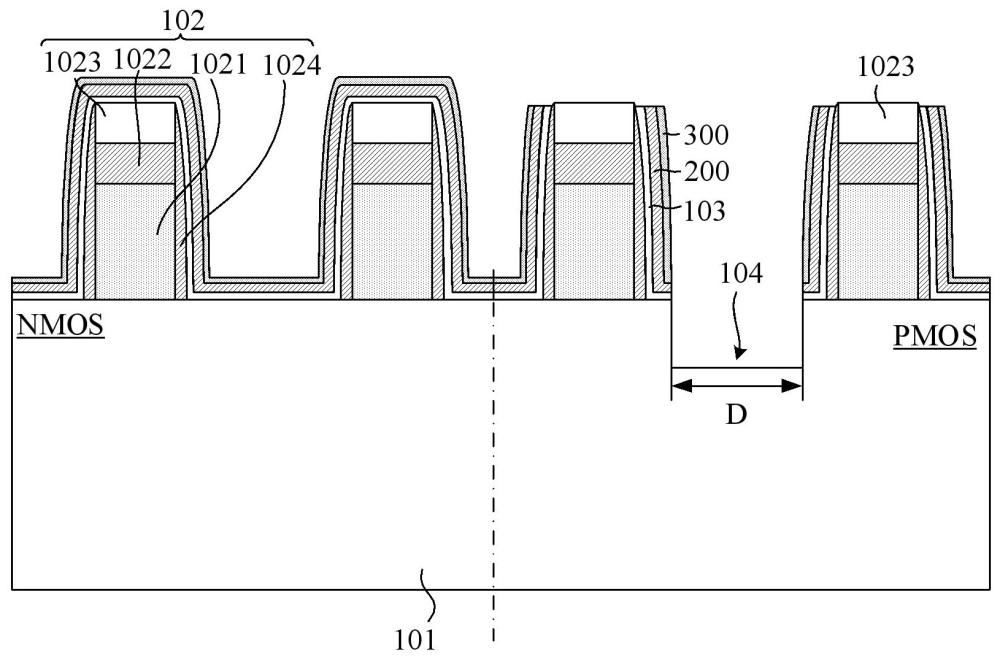

3、本发明提供了一种半导体结构,包括:

4、衬底,所述衬底包括nmos器件区和pmos器件区,其中pmos器件区包括预留区域,所述预留区域为pmos器件区的源漏区域;

5、栅极结构,设置在所述nmos器件区上和所述pmos器件区上;

6、氮化层,覆盖所述nmos器件区、所述pmos器件区中所述栅极结构的侧部,以及所述pmos器件区的部分所述衬底;

7、氮氧化层,覆盖在所述氮化层上;以及

8、预备沟槽,设置在所述衬底上,所述预备沟槽位于所述预留区域。

9、在本发明一实施例中,所述半导体结构包括西格玛沟槽,所述西格玛沟槽设置在所述衬底上,且所述西格玛沟槽形成于所述预备沟槽中。

10、在本发明一实施例中,在形成所述预备沟槽前,所述半导体结构包括光阻层,所述光阻层覆盖于所述氮氧化层上,且所述光阻层位于所述nmos器件区。

11、在本发明一实施例中,所述半导体结构包括表面氧化层,所述表面氧化层位于所述栅极结构和所述氮化层之间。

12、本发明提供了一种半导体结构的制造方法,包括以下步骤:

13、提供一衬底,所述衬底包括nmos器件区和pmos器件区,其中所述pmos器件区包括预留区域,所述预留区域为pmos器件区的源漏区域;

14、形成栅极结构于所述nmos器件区上和所述pmos器件区上;

15、形成氮化层于所述栅极结构上和所述衬底上,并氧化部分所述氮化层,形成氮氧化层,其中所述氮氧化层覆盖在所述氮化层上;

16、同步蚀刻所述预留区域上的所述氮氧化层和所述氮化层,以及所述栅极结构上的所述氮氧化层和所述氮化层,直到露出所述衬底的表面和所述栅极结构的顶面;以及

17、形成预备沟槽于所述预留区域上。

18、在本发明一实施例中,在形成所述栅极结构后,形成所述氮化层之前,形成表面氧化层于所述栅极结构上。

19、在本发明一实施例中,在形成所述氮氧化层后,且在蚀刻所述氮化层和所述氮氧化层之前,形成光阻层于所述氮氧化层上,其中所述光阻层覆盖所述nmos器件区和所述pmos器件区。

20、在本发明一实施例中,形成所述光阻层后,移除所述pmos器件区上的所述氮氧化层。

21、在本发明一实施例中,在蚀刻所述氮化层和所述氮氧化层后,且在形成所述预备沟槽前,移除所述光阻层。

22、在本发明一实施例中,形成所述预备沟槽后,蚀刻拓宽所述预备沟槽,形成西格玛沟槽。

23、如上所述,本发明提供了一种半导体结构及其制造方法,本发明意想不到的技术效果是:本发明能够得到关键尺寸更加准确,且形貌完整的半导体结构,能够大大减少缺陷的发生,提升了制程良率。并且根据本发明提供的半导体结构的制造方法,能够降低光刻胶图形负载对蚀刻造成的影响,减少蚀刻过程中氮化物和氧化层的非预期损失,从而提升制程中氮化物对pmos器件的栅极结构,以及对nmos器件的保护力度,进而提升了半导体结构的制造良率。根据本发明提供的半导体结构的制造方法,在进行锗硅外延工艺时,关键尺寸的误差更小,更有利于调整和控制半导体的关键尺寸,因此本发明提供的半导体结构,能够更加有效地提升pmos器件的拉应力,从而提升pmos器件的驱动电流。

24、当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的一种半导体结构,其特征在于,所述半导体结构包括西格玛沟槽,所述西格玛沟槽设置在所述衬底上,且所述西格玛沟槽形成于所述预备沟槽中。

3.根据权利要求1所述的一种半导体结构,其特征在于,在形成所述预备沟槽前,所述半导体结构包括光阻层,所述光阻层覆盖于所述氮氧化层上,且所述光阻层位于所述nmos器件区。

4.根据权利要求1所述的一种半导体结构,其特征在于,所述半导体结构包括表面氧化层,所述表面氧化层位于所述栅极结构和所述氮化层之间。

5.一种半导体结构的制造方法,其特征在于,包括以下步骤:

6.根据权利要求5所述的一种半导体结构的制造方法,其特征在于,在形成所述栅极结构后,形成所述氮化层之前,形成表面氧化层于所述栅极结构上。

7.根据权利要求5所述的一种半导体结构的制造方法,其特征在于,在形成所述氮氧化层后,且在蚀刻所述氮化层和所述氮氧化层之前,形成光阻层于所述氮氧化层上,其中所述光阻层覆盖所述nmos器件区和所述pmos器件区。

8.根据权利要求7所述的一种半导体结构的制造方法,其特征在于,形成所述光阻层后,移除所述pmos器件区上的所述氮氧化层。

9.根据权利要求8所述的一种半导体结构的制造方法,其特征在于,在蚀刻所述氮化层和所述氮氧化层后,且在形成所述预备沟槽前,移除所述光阻层。

10.根据权利要求5所述的一种半导体结构的制造方法,其特征在于,形成所述预备沟槽后,蚀刻拓宽所述预备沟槽,形成西格玛沟槽。

技术总结

本发明提供了一种半导体结构及其制造方法,其中半导体结构包括:衬底,衬底包括NMOS器件区和PMOS器件区,其中PMOS器件区包括预留区域,预留区域为PMOS器件区的源漏区域;栅极结构,设置在NMOS器件区上和PMOS器件区上;氮化层,覆盖NMOS器件区、PMOS器件区中栅极结构的侧部,以及PMOS器件区的部分衬底;氮氧化层,覆盖在氮化层上;预备沟槽,设置在衬底上,预备沟槽位于预留区域。本发明提供了一种半导体结构及其制造方法,能够提升半导体结构的成型质量和制程良率,并且更有利于提升PMOS器件的驱动电流。

技术研发人员:朱名杰,黄祥,张基东

受保护的技术使用者:安徽大学

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!