一种低噪声SiGe双极晶体管及其制造方法与流程

本发明涉及半导体,具体涉及一种低噪声sige双极晶体管及其制造方法。

背景技术:

1、sige bicmos工艺是在制造双极晶体管时,在硅基区材料中加入一定含量的锗,形成应变硅异质结构晶体管以改善双极晶体管特性的一种硅基集成工艺技术。sige hbt结构能够与硅cmos工艺兼容,可将宽带、高增益、低噪声电路与高密度、低功耗cmos数字逻辑阵列集成到一个芯片上,具有高速度、低噪声等高性能特点。因此,sige bicmos工艺是现代微波、射频以及毫米波电路以及超高速、高精度数据转换器电路的首选工艺之一。然而,低频噪声是半导体器件的本征物理特性,表现为半导体或金属电导的涨落,起源于载流子数目和/或迁移率的涨落。低频噪声通过晶体管本征的电流-电压(i-v)和电容-电压(i-v)关系的非线性特性转化成相位噪声,从而引起射频电路例如压控型振荡器(vco)电路线性特性的退化和电路频谱的纯度;此外,噪声对实际信号的干扰限制了器件的最小信号水平,降低系统的信噪比。现代sige工艺中,发射极内侧墙多采用氮化硅结构,以实现其良好的电隔离特性,提升sige hbt器件的直流和频率特性,但氮化硅与硅之间较大的晶格失配会引起发射极/基极界面处应力增大导致界面缺陷态增加引起sige hbt器件的噪声增加,限制了其在低频电路以及射频电路中的应用。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明提供一种低噪声sige双极晶体管及其制造方法,以解决现有技术中的至少其中一个问题。

2、为实现上述目的以及其他目的,本发明提供一种低噪声sige双极晶体管的制造方法,包括:

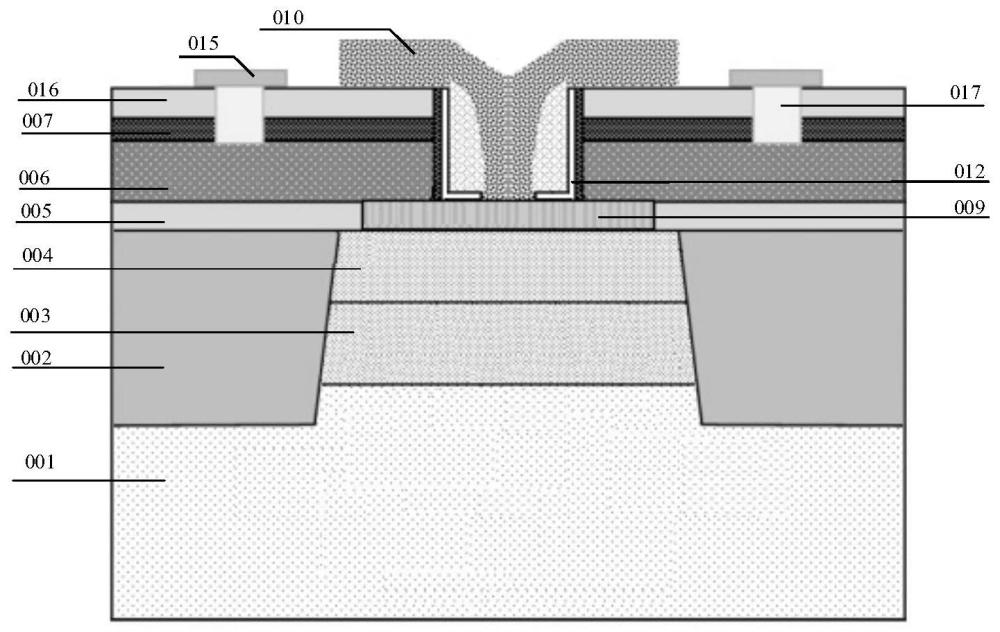

3、提供衬底,并在所述衬底上形成外延层,所述外延层包括有源区;

4、在所述外延层中有源区的两端分别形成一sti浅槽隔离结构,所述sti浅槽隔离结构由所述外延层的第一表面向所述衬底延伸,并穿透所述外延层延伸至所述衬底中;

5、在所述外延层上依次形成氧化层、p型多晶硅层、第一介质层;

6、依次对所述第一介质层、所述p型多晶硅进行刻蚀至氧化层,形成发射极窗口;

7、对位于发射极窗口底部的氧化层进行腐蚀,形成悬空的基区结构,通过选择性外延形成sige基区;

8、在所述发射极窗口内形成侧墙复合结构,所述侧墙复合结构贴附于所述发射极窗口侧壁与底部,所述侧墙复合结构的材料由氮化硅、氧化硅和多晶硅复合而成;

9、在所述发射极窗口内形成发射极,且使所述发射极覆盖部分所述第一介质层;

10、在第一介质层上形成第三介质层;

11、在所述第三介质层上形成基极,并与所述sige基区电接触。

12、于本发明一实施例中,所述在所述发射极窗口内形成侧墙复合结构的步骤包括:

13、淀积氮化硅薄膜,刻蚀所述氮化硅薄膜,在发射极窗口侧壁形成第一薄膜层;

14、依次淀积氧化硅薄膜和多晶硅薄膜,刻蚀所述多晶硅薄膜形成掩蔽层;

15、以所述掩蔽层作为腐蚀阻挡层,刻蚀氧化硅薄膜,形成发射极有效窗口;

16、湿法剥离所述掩蔽层,以暴露所述氧化硅薄膜,在发射极窗口侧壁形成第二薄膜层;

17、再次淀积多晶硅薄膜,刻蚀多晶硅薄膜,在发射极窗口侧壁形成第三薄膜层。

18、于本发明一实施例中,所述第一薄膜层的材料为氮化硅,所述第二薄膜层的材料为氧化硅,所述第三薄膜层的材料为多晶硅。

19、于本发明一实施例中,通过薄膜淀积工艺在所述外延层上形成所述氧化层。

20、于本发明一实施例中,所述方法还包括:

21、在所述衬底与所述外延层之间形成埋层。

22、于本发明一实施例中,通过重掺杂工艺在所述氧化层上形成p型多晶硅层。

23、于本发明一实施例中,所述第三薄膜层的材料与所述发射极的材料相同。

24、为实现上述目的以及其他目的,本发明提供一种低噪声sige双极晶体管,包括:

25、衬底;

26、外延层,设置于所述衬底上,所述外延层包括有源区;

27、设置在所述外延层中有源区的两端的sti浅槽隔离结构,所述sti浅槽隔离结构由所述外延层的第一表面向所述衬底延伸,并穿透所述外延层延伸至所述衬底中;

28、氧化层,设置于所述外延层上;

29、p型多晶硅层,设置于所述氧化层上;

30、第一介质层,设置于所述p型多晶硅层上;

31、sige基区,通过对位于发射极窗口底部的氧化层进行腐蚀,以及通过选择性外延在氧化层上形成;

32、发射极窗口,通过依次对所述介质层、所述p型多晶硅层进行刻蚀形成;所述发射极窗口内设置有两个贴附于所述发射极窗口侧壁与底部的侧墙复合结构,所述侧墙复合结构的材料由氮化硅、氧化硅和多晶硅复合而成;

33、发射极,形成于所述发射极窗口内,且使所述发射极覆盖部分所述第一介质层;

34、第三介质层,设置于所述第一介质层上;

35、基极,设置于所述第三介质层上,并与所述sige基区电接触。

36、于本发明一实施例中,所述侧壁结构包括:

37、第一薄膜层,贴附于所述发射极窗口的侧壁上;

38、第二薄膜层,覆盖所述第一薄膜层,且与所述sige基区电接触;

39、第三薄膜层,形成于所述第二薄膜层上。

40、于本发明一实施例中,所述第一薄膜层的材料为氮化硅,所述第二薄膜层的材料为氧化硅,所述第三薄膜层的材料为多晶硅。

41、本发明的有益效果:

42、本发明通过氮化硅/氧化硅/多晶硅来构成侧墙结构,氮化硅与氧化硅复合薄膜形成了发射极/基极的电绝缘层,一方面实现了发射极/基极的电学隔离,另一方面氮化硅层明显降低了硅与硅之间晶格失配带来的应力,抑制了基极/发射极界面缺陷的形成,降低了sige hbt器件载流子在电流传输路径上由于界面缺陷引起的载流子俘获和释放的几率,进而有效抑制了载流子在输运过程中与陷阱缺陷的随机电报噪声的产生,达到抑制器件低频噪声的作用。此外,在sige hbt器件发射极内侧墙形成的多晶硅薄膜带来应力小,减小了界面缺陷密度降低了器件噪声;另一方面多晶硅薄膜与掺杂多晶硅发射极为相同材料,一定程度上减小了发射极电阻,有助于提升器件的频率特性。同时,该抑制低频噪声的sige hbt异质结双极晶体管结构的工艺与现有工艺完全兼容,不增加工艺复杂度及制造成本,该抑制低频噪声的sige hbt异质结双极晶体管结构适用于研制生产低噪声放大器lna、射频本振电路等特殊需求的电路设计而不额外需要单独的电路级冗余设计措施。

43、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种低噪声sige双极晶体管的制造方法,其特征在于,包括:

2.根据权利要求1所述的低噪声sige双极晶体管的制造方法,其特征在于,所述在所述发射极窗口内形成侧墙复合结构的步骤包括:

3.根据权利要求2所述的低噪声sige双极晶体管的制造方法,其特征在于,所述第一薄膜层的材料为氮化硅,所述第二薄膜层的材料为氧化硅,所述第三薄膜层的材料为多晶硅。

4.根据权利要求1所述的低噪声sige双极晶体管的制造方法,其特征在于,通过薄膜淀积工艺在所述外延层上形成所述氧化层。

5.根据权利要求1所述的低噪声sige双极晶体管的制造方法,其特征在于,所述方法还包括:

6.根据权利要求1所述的低噪声sige双极晶体管的制造方法,其特征在于,通过重掺杂工艺在所述氧化层上形成p型多晶硅层。

7.根据权利要求2或3所述的低噪声sige双极晶体管的制造方法,其特征在于,所述第三薄膜层的材料与所述发射极的材料相同。

8.一种低噪声sige双极晶体管,其特征在于,包括:

9.根据权利要求8所述的低噪声sige双极晶体管,其特征在于,所述侧壁结构包括:

10.根据权利要求9所述的低噪声sige双极晶体管,其特征在于,所述第一薄膜层的材料为氮化硅,所述第二薄膜层的材料为氧化硅,所述第三薄膜层的材料为多晶硅。

技术总结

本发明公开了一种低噪声SiGe双极晶体管及其制造方法,双极晶体管包括:衬底、设置在衬底上的外延层、设置在外延层中且位于外延层的顶部的基区、设置在基区中且位于基区的顶部的发射区,发射区中包括侧墙复合结构,侧墙复合结构的材料由氮化硅、氧化硅和多晶硅复合而成。通过将侧墙结构中常用的氮化硅Spacer更改为氮化硅/氧化硅/多晶硅的侧墙结构,降低了SiGe HBT器件载流子在电流传输路径上由于界面缺陷引起的载流子俘获和释放的几率,进而有效抑制了载流子在输运过程中与陷阱缺陷的随机电报噪声的产额,达到抑制器件低频噪声的作用。

技术研发人员:张培健,易孝辉,洪敏,朱坤峰,魏佳男,张广胜,唐新悦,钱坤,廖文龙,罗婷,杨倩

受保护的技术使用者:中国电子科技集团公司第二十四研究所

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!