一种碳化硅沟槽型MOSFET器件及其制备工艺的制作方法

本发明涉及碳化硅mosfet器件制造,具体涉及一种碳化硅沟槽型mosfet器件及其制备工艺。

背景技术:

1、碳化硅mosfet技术是一种基于碳化硅材料的功率半导体器件技术,具有高温、高压、高频等优异的特性,逐渐成为下一代功率电子器件的研究热点之一。作为第三代半导体材料,碳化硅(sic)其具有禁带宽度大、熔点高、介电常数低、击穿场强高、饱和电子漂移速率高、热导率高以及化学性质稳定等诸多优点,使得碳化硅基功率器件在高压、高温、高频、大功率、以及强辐射等方面都有着极大的应用前景,特别适合于制作高压大功率电子器件。碳化硅是一种颠覆性的技术,随着新能源汽车、光伏储能领域的发展,它正在取代硅基技术的地位,开始受到市场的广泛关注。

2、然而,在碳化硅材料中任何种类的掺杂剂都难以扩散。因此,对于碳化硅器件,就需要以不同的注入能量多次注入掺杂剂,以在碳化硅的外延层中形成结。特别是对于碳化硅沟槽型mosfet工艺,由于需要非常高的注入能量,所以jfet结难以形成。沟槽型栅极工艺中的沟道长度被定义为p阱深度。通常,沟槽型栅极的p阱结深比平面栅极的p阱深。沟槽型栅的jfet结应在p阱的底部。因此,需要更高的能量注入在p阱的底部形成jfet结结构。正因如此,jfet结工艺难以形成,故通常在碳化硅沟槽型mosfet工艺中跳过jfet结结构。

技术实现思路

1、本发明的目的在于:针对碳化硅沟槽型mosfet器件中由于p阱较深导致难以在p阱的底部形成jfet结构的问题,而提供了一种碳化硅沟槽型mosfet器件的制备工艺,有效解决了上述问题。

2、为解决上述问题,本发明是通过如下技术方案实现的:

3、提供一种碳化硅沟槽型mosfet器件的制备工艺,包括如下步骤:

4、s1、提供半导体衬底,且所述的半导体衬底其具有相对的第一表面和第二表面;

5、s2、在所述半导体衬底的第一表面上外延生长,形成一层外延层;

6、s3、在所述外延层的上表面沉积第一氧化层;

7、s4、对所述第一氧化层进行光刻,形成若干凹槽,凹槽的底部即为外延层;

8、s5、以所述凹槽为基准对所述外延层进行刻蚀,从而在所述外延层中刻蚀形成若干沟槽;

9、s6、去除所述外延层上残余的第一氧化层,即获得了具有沟槽结构的外延层;

10、s7、继续氧化层的沉积,以在所述外延层的上表面和所述沟槽的内部形成连续的第二氧化层;

11、s8、采用相对于所述外延层的上表面倾斜的方式进行n型掺杂注入,以在第二氧化层下方的外延层中形成jfet区;

12、s9、在所述的沟槽中进行多晶硅沉积并平整化;

13、s10、采用相对于所述外延层的上表面垂直的方式进行p型掺杂注入,以在所述外延层中形成pwell区;其中:所述的pwell区覆盖掉部分jfet区;

14、s11、在所述pwell区中进行离子注入并退火,从而形成n+源区;

15、s12、在所述外延层上进行源极的制备,以及在所述半导体衬底的第二表面上形成漏极,完成mosfet器件的制备。

16、具体的,本发明提供的是一种具有自对准jfet结构的碳化硅沟槽型mosfet器件的制备工艺。

17、进一步的,步骤s1中所述的半导体衬底为n型重掺杂氮化硅衬底(n+衬底),衬底的掺杂离子为磷离子。

18、进一步的,步骤s2中所述外延层的厚度与mosfet器件的耐压要求正相关,耐压要求越高,则所述外延层的厚度越厚。

19、进一步的,步骤s3和s7中所述第一氧化层和第二氧化层的材质均为二氧化硅,所述的第一氧化层和第二氧化层采用高温炉管工艺生长形成,其厚度设置分别为1.0~2.0μm。

20、进一步的,步骤s5中所述沟槽的深度为6.0~10.0μm。

21、进一步的,步骤s8中n型掺杂注入的倾斜角度为α,且满足30°≤α≤60°,所述jfet区的厚度为1.0μm~2.0μm。

22、进一步的,步骤s10中p型掺杂注入的剂量高于n型掺杂注入的剂量,经过p型掺杂注入后所形成的pwell区将会覆盖掉部分jfet区,仅保留靠近所述沟槽侧壁底部的部分jfet区,此时剩余的所述jfet区的厚度为1.0~2.0μm、高度为2.0~4.0μm。由于多晶硅的阻挡作用,在对应沟槽底部位置的外延层中不会形成pwell区。此外,由于p型掺杂注入的剂量要高于n型掺杂注入,因此在p型掺杂注入后jfet区和pwell区之间的重叠区域则会变成pwell区。

23、进一步的,步骤s11中的退火温度为850~900℃,退火时间为90~120分钟。

24、进一步的,步骤s12中采用磁控溅射或电子束蒸发工艺分别形成所述源极和漏极。

25、一种碳化硅沟槽型mosfet器件,采用上述的制备工艺制得。

26、本发明的有益效果:

27、针对碳化硅沟槽型mosfet器件中因p阱较深而难以在p阱的底部形成jfet结构的问题,本发明提供了一种具有自对准jfet结构的碳化硅沟槽型mosfet器件的制备工艺,在本发明中通过对工艺的改进,以及通过沟槽结构和倾斜注入相结合的方式实现了自对准jfet结构,在没有任何掩膜层的情况下,通过沟槽结构和倾斜注入的阴影效应就可以使jfet结构处于我们想要的位置。本发明的工艺可以通过调整注入角度实现在不同位置形成jfet结构,解决了现有技术难以在碳化硅沟槽型mosfet器件p阱底部形成jfet结构的问题。

技术特征:

1.一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,该工艺包括如下步骤:

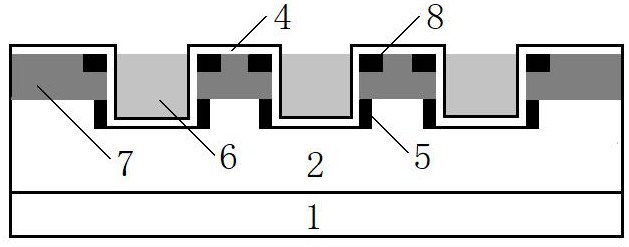

2.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s1中所述的半导体衬底(1)为n型重掺杂氮化硅衬底。

3.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s2中所述外延层(2)的厚度与mosfet器件的耐压要求正相关。

4.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s3和s7中所述第一氧化层(3)和第二氧化层(4)的材质均为二氧化硅,所述第一氧化层(3)和第二氧化层(4)采用高温炉管工艺生长形成,其厚度设置分别为1.0~2.0μm。

5.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s5中所述沟槽(21)的深度为6.0~10.0μm。

6.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s8中n型掺杂注入的倾斜角度为α,且满足30°≤α≤60°,所述jfet区(5)的厚度为1.0μm~2.0μm。

7.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s10中p型掺杂注入的剂量高于n型掺杂注入的剂量,经过p型掺杂注入所形成的pwell区(7)将覆盖掉部分jfet区(5),仅保留靠近所述沟槽(21)侧壁底部的jfet区(5)。

8.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s11中的退火温度为850~900℃,退火时间为90~120分钟。

9.根据权利要求1所述的一种碳化硅沟槽型mosfet器件的制备工艺,其特征在于,步骤s12中采用磁控溅射或电子束蒸发工艺分别形成所述源极和漏极。

10.一种碳化硅沟槽型mosfet器件,其特征在于,采用权利要求1~9任一项所述的制备工艺制得。

技术总结

本发明涉及碳化硅MOSFET器件制造领域,公开了一种碳化硅沟槽型MOSFET器件及制备工艺;S1提供具有第一表面和第二表面的半导体衬底;S2在第一表面形成外延层;S3外延层沉积第一氧化层;S4第一氧化层光刻形成凹槽;S5以凹槽为基准进行刻蚀,形成沟槽;S6去除第一氧化层;S7在外延层和沟槽中形成第二氧化层;S8采用倾斜的方式进行N型掺杂注入,在外延层中形成JFET区;S9在沟槽中沉积多晶硅;S10采用垂直的方式进行P型掺杂注入,在外延层中形成Pwell区;Pwell区覆盖部分JFET区;S11在Pwell区中离子注入并退火,形成N+源区;S12在外延层上制备源极,在第二表面形成漏极,完成制备。

技术研发人员:金恩泽,尹锺晚,李承浩,夏凯,陶磊,朱世荣

受保护的技术使用者:爱特微(张家港)半导体技术有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!