堆叠器件结构及其形成方法与流程

本申请的实施例涉及堆叠器件结构及其形成方法。

背景技术:

1、电子工业经历了对更小且更快的电子器件的不断增长的需求,这些电子器件同时能够支持更多的日益复杂和精密的功能。为了满足这些需求,在集成电路(ic)工业中存在制造低成本、高性能和低功率ic的持续趋势。迄今为止,这些目标在很大程度上通过减小ic尺寸(例如,通过减小最小ic部件尺寸)来实现,从而改进生产效率并且降低相关成本。但是,这样的缩放也增加了ic制造工艺的复杂性。因此,实现ic器件及其性能的持续进步需要ic制造工艺和技术的类似进步。

技术实现思路

1、本申请的一些实施例提供了一种形成堆叠器件结构的方法,包括:在第一器件组件上形成第一材料的第一绝缘层;在第二器件组件上形成第二材料的第二绝缘层,其中,所述第二材料与所述第一材料相同;对所述第一绝缘层和所述第二绝缘层实施等离子体活化工艺,以提供具有第一等离子体活化表面的所述第一绝缘层和具有第二等离子体活化表面的所述第二绝缘层;接合所述第一绝缘层的所述第一等离子体活化表面和所述第二绝缘层的所述第二等离子体活化表面,以形成堆叠结构,所述堆叠结构包括位于所述第二器件组件上方的第一器件组件,其中,接合至所述第二绝缘层的所述第一绝缘层在所述第一器件组件和所述第二器件组件之间形成隔离结构;以及处理所述堆叠结构以形成设置在第二器件上方的第一器件,其中,所述隔离结构将所述第一器件和所述第二器件分隔开。

2、本申请的另一些实施例提供了一种形成堆叠器件结构的方法,包括:在第一器件组件上形成第一材料的第一绝缘层;在第二器件组件上形成第二材料的第二绝缘层,其中,所述第二材料与所述第一材料不同;接合所述第一绝缘层和所述第二绝缘层以形成堆叠结构,所述堆叠结构包括位于所述第二器件组件上方的所述第一器件组件,其中,接合至所述第二绝缘层的所述第一绝缘层在所述第一器件组件和所述第二器件组件之间形成隔离结构;以及处理所述堆叠结构以形成设置在第二器件上方的第一器件,其中,所述隔离结构将所述第一器件和所述第二器件分隔开。

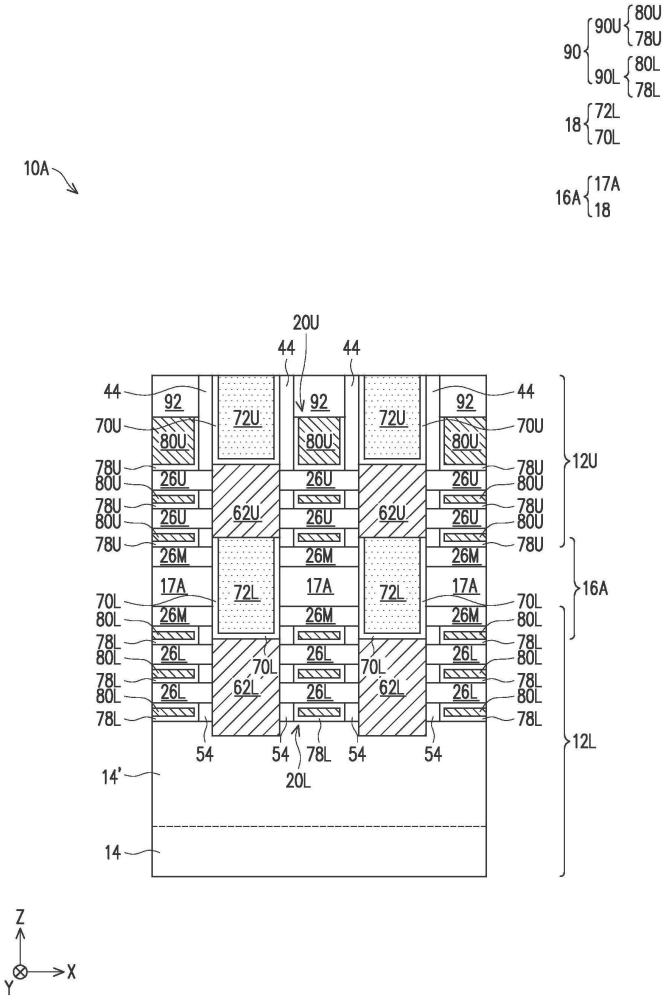

3、本申请的又一些实施例提供了一种堆叠器件结构,包括:晶体管堆叠件,具有设置在第二晶体管上方的第一晶体管,其中:所述第一晶体管具有第一半导体层、第一栅极堆叠件和第一源极/漏极,其中,所述第一半导体层设置在所述第一源极/漏极之间,所述第一栅极堆叠件设置在所述第一源极/漏极之间,并且所述第一栅极堆叠件包裹所述第一半导体层,所述第二晶体管具有第二半导体层、第二栅极堆叠件和第二源极/漏极,其中,所述第二半导体层设置在所述第二源极/漏极之间,所述第二栅极堆叠件设置在所述第二源极/漏极之间,并且所述第二栅极堆叠件包裹所述第二半导体层,并且所述第一源极/漏极设置在所述第二源极/漏极上方,并且所述第一栅极堆叠件设置在所述第二栅极堆叠件上方;以及接合层,设置在所述第一栅极堆叠件和所述第二栅极堆叠件之间,其中,所述接合层具有:具有第一成分的第一部分和具有与所述第一成分不同的第二成分的第二部分。

技术特征:

1.一种形成堆叠器件结构的方法,包括:

2.根据权利要求1所述的方法,其中:

3.根据权利要求1所述的方法,其中:

4.根据权利要求1所述的方法,其中,所述第一绝缘层的所述第一等离子体活化表面和所述第二绝缘层的所述第二等离子体活化表面分别是第一硅烷醇表面和第二硅烷醇表面。

5.根据权利要求1所述的方法,其中,所述隔离结构的厚度小于约10nm,所述第一绝缘层的厚度小于约5nm,并且所述第二绝缘层的厚度小于约5nm。

6.根据权利要求1所述的方法,还包括:在所述接合之前,用去离子水清洁所述第一绝缘层的所述第一等离子体活化表面和所述第二绝缘层的所述第二等离子体活化表面。

7.根据权利要求1所述的方法,其中,将所述第一绝缘层的所述第一等离子体活化表面接合至所述第二绝缘层的所述第二等离子体活化表面以形成所述堆叠结构包括:

8.根据权利要求1所述的方法,其中:

9.一种形成堆叠器件结构的方法,包括:

10.一种堆叠器件结构,包括:

技术总结

本文公开了用于堆叠器件结构的接合和隔离技术。示例性方法包括:在第一器件组件上形成第一绝缘层;在第二器件组件上形成第二绝缘层;以及接合第一绝缘层和第二绝缘层。接合提供了堆叠结构,堆叠结构包括位于第二器件组件上方的第一器件组件以及它们之间的隔离结构(由接合至第二绝缘层的第一绝缘层形成)。隔离结构包括具有第一成分的第一部分和具有与第一成分不同的第二成分的第二部分。方法还包括处理堆叠结构以形成设置在第二器件上方的第一器件,其中隔离结构将第一器件和第二器件分隔开。第一绝缘层和第二绝缘层可以包括相同或不同的材料。本申请的实施例还涉及堆叠器件结构及其形成方法。

技术研发人员:胡宽侃,陈翰德,杨固峰,蔡承峯,徐志安,廖思雅

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/6/13

- 还没有人留言评论。精彩留言会获得点赞!