一种阵列基板、显示面板和显示装置的制作方法

本发明涉及半导体,尤其涉及一种阵列基板、显示面板和显示装置。

背景技术:

1、双栅(dual gate)产品设计能够减半显示面板数据线数量需求,从而减少源极覆晶膜(source cof)使用数量,可以显著降低面板生产成本,因而在近年来受到人们的广泛关注。

2、现有dual gate显示产品,在阵列基板实际制作过程中,数据线层可能会相对像素电极层发生偏移,在两层发生偏移时,相邻两个像素电极会存在与数据线之间的耦合电容cpd差异,导致横纹不良问题。

技术实现思路

1、本发明提供一种阵列基板、显示面板和显示装置,以改善现有技术中相邻两个像素电极与数据线之间的耦合电容差异,导致横纹不良问题。

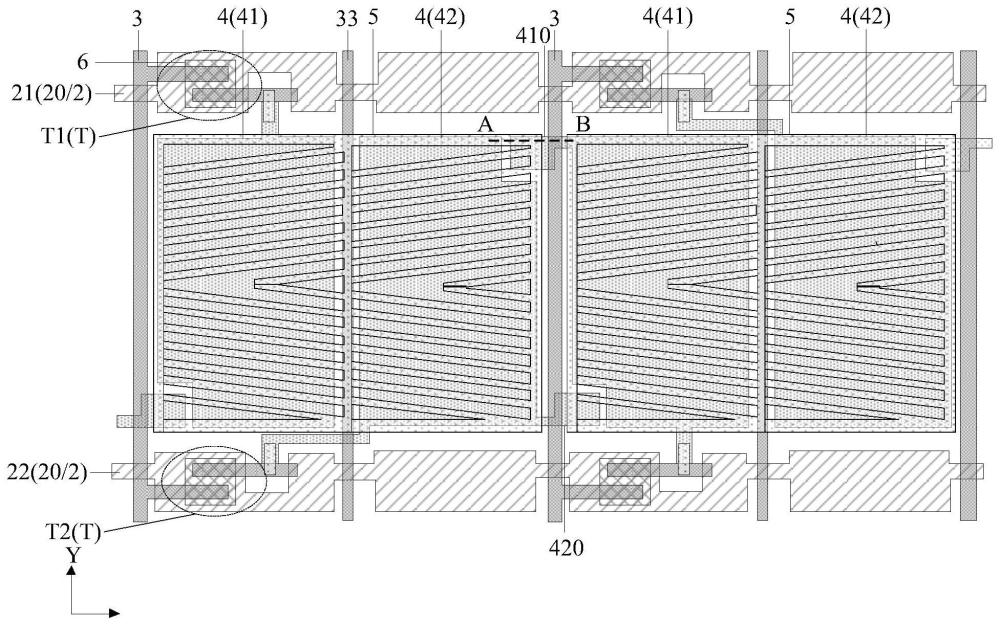

2、本发明实施例提供一种阵列基板,包括:衬底,以及位于所述衬底一侧的:多个沿第一方向延伸的栅线组,多个沿第二方向延伸的数据线,多个像素电极,以及多个晶体管;

3、所述栅线组包括:两条沿所述第一方向延伸的栅线;两条所述栅线包括:位于所述像素电极一侧的第一栅线,以及位于所述像素电极另一侧的第二栅线,其中,所述第二栅线加载的信号延迟于所述第一栅线加载的信号;所述多个像素电极包括:位于所述栅线组与所述数据线交叉形成的区域内、且通过所述晶体管连接于同一所述数据线的第一像素电极和第二像素电极,所述第二像素电极位于第一像素电极远离通过所述晶体管连接的所述数据线的一侧;

4、位于同一所述数据线不同侧且相邻的所述第一像素电极和所述第二像素电极中,所述第一像素电极朝向所述第二像素电极的一侧具有向所述第二像素电极一侧延伸的第一外延部,所述第二像素电极朝向所述第一像素电极的一侧具有向所述第一像素电极一侧延伸的第二外延部;所述第一外延部在所述衬底的正投影,与所述数据线在所述衬底的正投影具有交叠区域,所述第二外延部在所述衬底的正投影,与所述数据线在所述衬底的正投影具有交叠区域。

5、在一种可能的实施方式中,所述第一外延部包括:第一外延主部,以及连接所述第一外延主部与所述第一像素电极的第一外延连接部;所述第一外延主部在所述第二方向上的宽度,大于所述第一外延连接部在所述第二方向上的宽度;

6、所述第二外延部包括:第二外延主部,以及连接所述第二外延主部与所述第二像素电极的第二外延连接部;所述第二外延主部在所述第二方向上的宽度,大于所述第二外延连接部在所述第二方向上的宽度。

7、在一种可能的实施方式中,所述第一外延部在所述衬底的正投影形状,与所述第二外延部在所述衬底的正投影形状相同;所述第一外延部在所述衬底的正投影面积,与所述第二外延部在所述衬底的正投影面积相同。

8、在一种可能的实施方式中,所述像素电极在所述第二方向上具有第一端部以及第二端部;所述第一外延部位于所述第一像素电极的所述第一端部;所述第二外延部位于所述第二像素电极在所述第二方向的第二端部。

9、在一种可能的实施方式中,所述第一像素电极朝向所述第二像素电极的一侧具有第一缺口,所述第二外延部位于所述第一缺口所在区域;所述第二像素电极朝向所述第一像素电极的一侧具有第二缺口,所述第一外延部位于所述第二缺口所在区域。

10、在一种可能的实施方式中,所述数据线位于所述像素电极背离所述衬底的一侧;所述多个像素电极具有沿所述第一方向延伸且沿所述第二方向排布的多个像素电极行;所述像素电极行包括多个沿所述第一方向排布的所述像素电极;

11、所述数据线包括:沿所述第二方向依次分布的第一数据部以及第二数据部;所述第一数据部在所述衬底的正投影,位于所述像素电极行在所述衬底正投影的所在区域;所述第二数据部在所述衬底的正投影,位于相邻两个所述像素电极行在所述衬底的正投影之间;

12、所述阵列基板还包括:位于所述数据线所在层朝向所述衬底一侧的多个第一走线;所述第一走线在所述衬底的正投影,与所述第一数据部在所述衬底的正投影重叠。

13、在一种可能的实施方式中,所述第一走线与所述像素电极同层同材料。

14、在一种可能的实施方式中,所述阵列基板还包括:位于所述数据线所在层与所述第一走线所在层之间的多个第二走线;所述第二走线在所述衬底的正投影,与所述第一数据部在所述衬底的正投影重叠。

15、在一种可能的实施方式中,所述第二走线与所述栅线同层同材料。

16、在一种可能的实施方式中,所述第二走线在所述衬底的正投影,与所述第一走线在所述衬底的正投影重叠,且所述第二走线与所述第一走线直接接触。

17、在一种可能的实施方式中,所述第一像素电极与所述数据线在所述第一方向上的间距范围为5μm~10μm;所述第二像素电极与所述数据线在所述第一方向上的间距范围为5μm~10μm。

18、在一种可能的实施方式中,所述栅线位于所述数据线所在层与所述像素电极所在层之间;所述阵列基板还包括:位于所述数据线背离所述像素电极一侧的公共电极层。

19、在一种可能的实施方式中,所述阵列基板还包括:位于所述数据线所在层与所述栅线所在层之间、且与所述数据线直接接触的有源层;所述有源层在所述衬底的正投影,与所述数据线在所述衬底的正投影交叠。

20、本公开实施例还提供一种显示面板,包括如本公开实施例提供的所述阵列基板,还包括与所述阵列基板相对设置的对向基板。

21、本公开实施例还提供一种显示装置,包括如本公开实施例提供的所述显示面板。

22、本发明实施例有益效果如下:本发明实施例中,第一像素电极具有第一外延部,第二像素电极具有第二外延部,也即像素电极在与数据线交叠的位置处增加了层间偏移补偿结构,当像素电极所在层与数据线所在层发生层间偏移时,数据线两侧的像素电极与该数据线之间的侧向电容与交叠电容分别发生差异,但两者差异的方向相反,即像素电极与数据线之间侧向电容增加的子像素,其交叠电容减小,而像素电极与数据线之间侧向电容减小的子像素,其交叠电容增大,每个子像素增大与减小的电容值相互抵消,从而确保数据线与其两侧像素电极之间的耦合电容基本不变,从而大幅度减轻甚至消除横纹不良问题,除此之外,此设计可减小数据线与像素电极之间距离,增大像素有效开口区,进而显著提升像素透过率。

技术特征:

1.一种阵列基板,其特征在于,包括:衬底,以及位于所述衬底一侧的:多个沿第一方向延伸的栅线组,多个沿第二方向延伸的数据线,多个像素电极,以及多个晶体管;

2.如权利要求1所述的阵列基板,其特征在于,所述第一外延部包括:第一外延主部,以及连接所述第一外延主部与所述第一像素电极的第一外延连接部;所述第一外延主部在所述第二方向上的宽度,大于所述第一外延连接部在所述第二方向上的宽度;

3.如权利要求2所述的阵列基板,其特征在于,所述第一外延部在所述衬底的正投影形状,与所述第二外延部在所述衬底的正投影形状相同;所述第一外延部在所述衬底的正投影面积,与所述第二外延部在所述衬底的正投影面积相同。

4.如权利要求2所述的阵列基板,其特征在于,所述像素电极在所述第二方向上具有第一端部以及第二端部;所述第一外延部位于所述第一像素电极的所述第一端部;所述第二外延部位于所述第二像素电极在所述第二方向的第二端部。

5.如权利要求1所述的阵列基板,其特征在于,所述第一像素电极朝向所述第二像素电极的一侧具有第一缺口,所述第二外延部位于所述第一缺口所在区域;所述第二像素电极朝向所述第一像素电极的一侧具有第二缺口,所述第一外延部位于所述第二缺口所在区域。

6.如权利要求1-5任一项所述的阵列基板,其特征在于,所述数据线位于所述像素电极背离所述衬底的一侧;所述多个像素电极具有沿所述第一方向延伸且沿所述第二方向排布的多个像素电极行;所述像素电极行包括多个沿所述第一方向排布的所述像素电极;

7.如权利要求6所述的阵列基板,其特征在于,所述第一走线与所述像素电极同层同材料。

8.如权利要求6所述的阵列基板,其特征在于,所述阵列基板还包括:位于所述数据线所在层与所述第一走线所在层之间的多个第二走线;所述第二走线在所述衬底的正投影,与所述第一数据部在所述衬底的正投影重叠。

9.如权利要求8所述的阵列基板,其特征在于,所述第二走线与所述栅线同层同材料。

10.如权利要求9所述的阵列基板,其特征在于,所述第二走线在所述衬底的正投影,与所述第一走线在所述衬底的正投影重叠,且所述第二走线与所述第一走线直接接触。

11.如权利要求8所述的阵列基板,其特征在于,所述第一像素电极与所述数据线在所述第一方向上的间距范围为5μm~10μm;所述第二像素电极与所述数据线在所述第一方向上的间距范围为5μm~10μm。

12.如权利要求6所述的阵列基板,其特征在于,所述栅线位于所述数据线所在层与所述像素电极所在层之间;所述阵列基板还包括:位于所述数据线背离所述像素电极一侧的公共电极层。

13.如权利要求12所述的阵列基板,其特征在于,所述阵列基板还包括:位于所述数据线所在层与所述栅线所在层之间、且与所述数据线直接接触的有源层;所述有源层在所述衬底的正投影,与所述数据线在所述衬底的正投影交叠。

14.一种显示面板,其特征在于,包括如权利要求1-13任一项所述的阵列基板,还包括与所述阵列基板相对设置的对向基板。

15.一种显示装置,其特征在于,包括如权利要求14所述的显示面板。

技术总结

本发明公开了一种阵列基板、显示面板和显示装置,以改善现有技术中相邻两个像素电极与数据线之间的耦合电容差异,导致横纹不良问题。所述阵列基板中,所述第一像素电极朝向所述第二像素电极的一侧具有向所述第二像素电极一侧延伸的第一外延部,所述第二像素电极朝向所述第一像素电极的一侧具有向所述第一像素电极一侧延伸的第二外延部;所述第一外延部在所述衬底的正投影,与所述数据线在所述衬底的正投影具有交叠区域,所述第二外延部在所述衬底的正投影,与所述数据线在所述衬底的正投影具有交叠区域。

技术研发人员:侯文杰,缪应蒙,陈东川,杨越

受保护的技术使用者:北京京东方显示技术有限公司

技术研发日:

技术公布日:2024/5/19

- 还没有人留言评论。精彩留言会获得点赞!