静电防护装置、静电防护半导体器件及静电防护方法与流程

本发明涉及半导体,具体地,涉及一种静电防护装置、静电防护半导体器件及静电防护方法。

背景技术:

1、esd(electro-static discharge,静电放电)是一种客观存在的自然现象,伴随着产品的整个周期。esd不易被人体感知,却会对集成电路产品造成严重威胁。在芯片的制造、封装、测试到应用阶段,其外部环境和内部结构都会积累一定的电荷,会随时受到静电的威胁。因此,在芯片设计中需要在各个引脚(pin)放置esd防护器件。例如使用nmos结构或pmos结构作为esd防护器件。

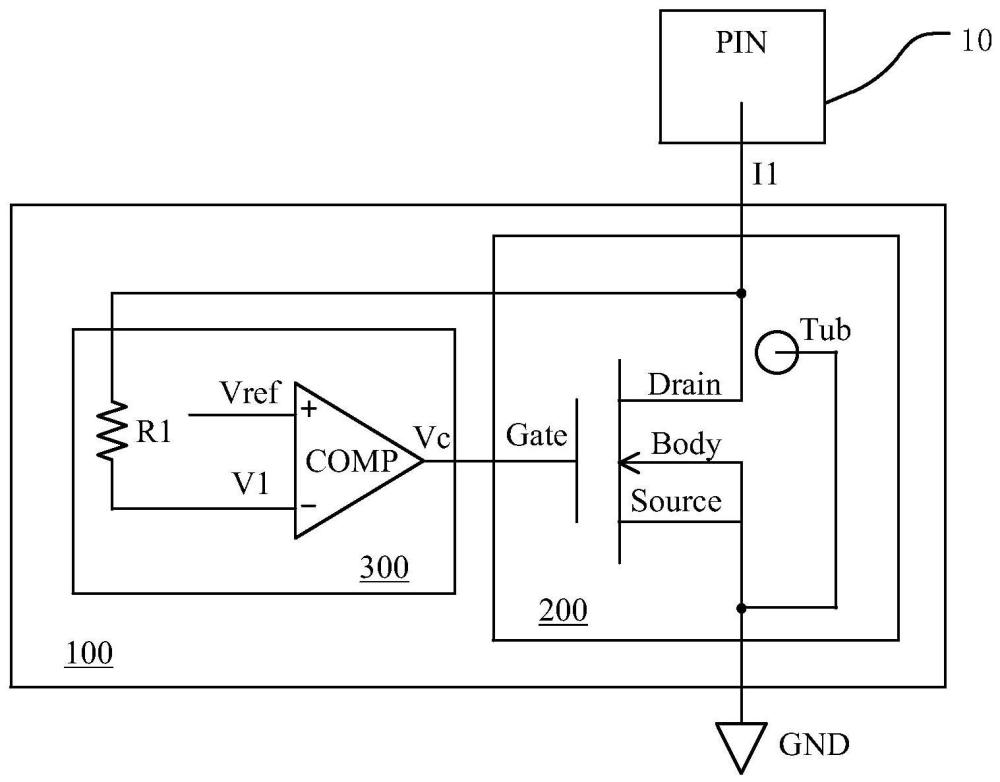

2、图1示出了现有技术的芯片的静电防护装置的示意图。如图1所示,该静电防护装置20连接在芯片的引脚(pin)10上,静电防护装置20例如是nmos器件。其漏极drain连接至引脚(pin)10,体区body、源极source和栅极gate都接地,包围nmos的有源区的盆状阱区tub也接地。在芯片应用时,各个引脚都会遭遇到电流冲击,例如在进行闩锁(latch up)实验时,通常会由引脚(pin)10向外拉取一个电流,按照电流流向将该拉取的电流视为负电流。那么引脚(pin)10在遭受负电流冲击时,由于nmos器件20本身的结构特性,其内部会产生一些三极管等寄生结构。漏极drain会向内部的盆状阱区tub拉取电流,造成较大的电流路径,甚至形成闩锁效应而造成芯片的损坏。因此目前的nmos器件的静电防护性能还有待提升。

技术实现思路

1、鉴于上述问题,本发明的目的在于提供一种静电防护装置、静电防护半导体器件及静电防护方法,以解决现有技术中的问题。

2、根据本发明的一方面,提供一种静电防护装置,连接在芯片的引脚上,其中,所述静电防护装置包括:静电防护半导体器件,用于泄放所述引脚上产生的电流,包括源极、漏极和栅极,所述漏极连接所述引脚,所述源极连接参考地;以及比较电路,连接在所述引脚和所述静电防护半导体器件的栅极之间,获取引脚上的电压得到电压信号,将所述电压信号与参考信号进行比较,根据比较结果控制所述静电防护半导体器件的导通状态,其中,当所述电压信号小于所述参考信号时,表征所述引脚上产生的负电流达到阈值电流,所述比较电路控制所述静电防护半导体器件的源极和漏极之间的沟道打开,所述参考信号为负电压。

3、可选地,所述静电防护半导体器件为nmos器件,所述参考信号处于-0.1v至-2v之间。

4、可选地,所述比较电路包括:比较器,所述比较器的正向输入端和反向输入端分别接收所述参考信号和所述电压信号,所述比较器的输出端连接至所述栅极;以及电阻,连接在所述引脚和所述比较器的反向输入端之间,用于获取所述引脚上的电压得到所述电压信号,提供至所述比较器。

5、根据本发明的另一方面,提供一种静电防护半导体器件,连接在芯片的引脚和参考地之间,其中,所述静电防护半导体器件包括:衬底;第一阱区,分布在所述衬底中,具有第一掺杂类型;第二阱区,位于所述第一阱区中,具有第二掺杂类型,所述第一掺杂类型和所述第二掺杂类型相反;多个第一注入区和多个第二注入区,间隔分布在所述第一阱区至所述第二阱区内以及阱区之间的空隙处,分别具有第一掺杂类型和第二掺杂类型;以及场板层,位于所述第二阱区上方,引出栅极电极,所述场板层两侧邻接的所述第一注入区分别引出为漏极电极和源极电极,其中,所述漏极电极连接所述引脚,所述源极电极连接参考地,所述栅极电极接收控制信号,当所述引脚上的电压信号小于预设的负电压的参考信号时,所述控制信号使源极和漏极之间的沟道打开。

6、可选地,所述静电防护半导体器件为nmos器件,所述第一掺杂类型为n型掺杂,所述第二掺杂类型为p型掺杂。

7、可选地,所述参考信号处于-0.1v至-2v之间。

8、可选地,当所述引脚上产生正电流时,所述漏极、所述第二阱区和所述第一阱区之间的第一寄生三极管打开,泄放电流。

9、可选地,当所述引脚上产生负电流时,所述第一阱区、所述第二阱区和所述漏极之间的第一寄生三极管打开,或者,所述衬底中的第一注入区、所述衬底和所述第一阱区之间的第二寄生三极管和所述第一阱区、所述第二阱区和所述漏极之间的第一寄生三极管同时打开,形成第一电流泄放路径,以泄放电流。

10、可选地,当所述引脚上的电压信号小于预设的负电压的参考信号时,所述源极和漏极之间的沟道打开形成第二电流泄放路径。

11、根据本发明的另一方面,提供一种静电防护方法,应用至上述的静电防护半导体器件中,所述静电防护方法包括:获取所述引脚上的电压,得到电压信号;将所述电压信号与预设的负电压的参考信号进行比较,根据比较结果控制所述静电防护半导体器件的导通状态;当所述电压信号小于所述参考信号时,表征所述引脚上产生的负电流达到阈值电流,控制所述静电防护半导体器件的源极和漏极之间的沟道打开。

12、本发明提供的静电防护装置、静电防护半导体器件及静电防护方法,使静电防护半导体器件的栅极接收控制信号,控制信号又与引脚上的电流大小相关,当引脚上的电压信号小于预设的负电压的参考信号时,表征引脚上产生的负电流达到阈值电流,控制信号使静电防护半导体器件的源极和漏极之间的沟道打开,从而增加了一条从源极到漏极之间的电流泄放路径。即当引脚受到较大的负电流冲击时,不仅可以由静电防护半导体器件内部的寄生结构泄放电流,还可以将沟道打开形成另一条泄放路径,避免静电防护半导体器件内部产生大电流损坏芯片,也有效避免了闩锁效应,提升静电防护能力。

13、进一步地,在引脚受到正电流冲击时可以由寄生结构形成从引脚到参考地的电流泄放路径;而在引脚受到负电流冲击时,也可以由寄生结构形成从供电电极到引脚的电流泄放路径;当引脚受到更大的负电流冲击时,还可以打开源极和漏极之间的沟道,增加一条从参考地到引脚的电流泄放路径。增强静电防护半导体器件和装置的esd防护能力和抗闩锁能力,在闩锁实验时对静电防护半导体器件起到很好的保护作用,同时也增强了正常静电放电时的泄放能力。

技术特征:

1.一种静电防护装置,连接在芯片的引脚上,其中,所述静电防护装置包括:

2.根据权利要求1所述的静电防护装置,其中,所述静电防护半导体器件为nmos器件,所述参考信号处于-0.1v至-2v之间。

3.根据权利要求1所述的静电防护装置,其中,所述比较电路包括:

4.一种静电防护半导体器件,连接在芯片的引脚和参考地之间,其中,所述静电防护半导体器件包括:

5.根据权利要求4所述的静电防护半导体器件,其中,所述静电防护半导体器件为nmos器件,所述第一掺杂类型为n型掺杂,所述第二掺杂类型为p型掺杂。

6.根据权利要求4所述的静电防护半导体器件,其中,所述参考信号处于-0.1v至-2v之间。

7.根据权利要求4所述的静电防护半导体器件,其中,当所述引脚上产生正电流时,所述漏极、所述第二阱区和所述第一阱区之间的第一寄生三极管打开,泄放电流。

8.根据权利要求4所述的静电防护半导体器件,当所述引脚上产生负电流时,所述第一阱区、所述第二阱区和所述漏极之间的第一寄生三极管打开,或者,所述衬底中的第一注入区、所述衬底和所述第一阱区之间的第二寄生三极管和所述第一阱区、所述第二阱区和所述漏极之间的第一寄生三极管同时打开,形成第一电流泄放路径,以泄放电流。

9.根据权利要求8所述的静电防护半导体器件,其中,当所述引脚上的电压信号小于预设的负电压的参考信号时,所述源极和漏极之间的沟道打开形成第二电流泄放路径。

10.一种静电防护方法,应用至根据权利要求4-9中任一项所述的静电防护半导体器件中,所述静电防护方法包括:

技术总结

本申请公开了一种静电防护装置、静电防护半导体器件及静电防护方法,静电防护装置连接在芯片的引脚上,包括:静电防护半导体器件,其漏极连接引脚,泄放引脚上的电流,源极连接参考地;以及比较电路,连接在引脚和静电防护半导体器件的栅极之间,获取引脚上的电压得到电压信号,将电压信号与负电压的参考信号进行比较,根据比较结果控制静电防护半导体器件的导通状态。当电压信号小于参考信号时,比较电路控制静电防护半导体器件的源极和漏极之间的沟道打开。从而在芯片的引脚遭受负电流冲击时,不仅可以通过静电防护半导体器件内部的寄生结构分担电流,还可以由源极和漏极之间的沟道分担电流,加强对芯片的保护,提升ESD防护性能和抗闩锁性能。

技术研发人员:姚丰,周孙泽

受保护的技术使用者:杰华特微电子股份有限公司

技术研发日:

技术公布日:2024/10/14

- 还没有人留言评论。精彩留言会获得点赞!