本发明一般涉及金属氧化物半导体场效应晶体管(mosfet)器件,并且具体地涉及分裂栅(split-gate)沟槽功率mosfet器件。

背景技术:

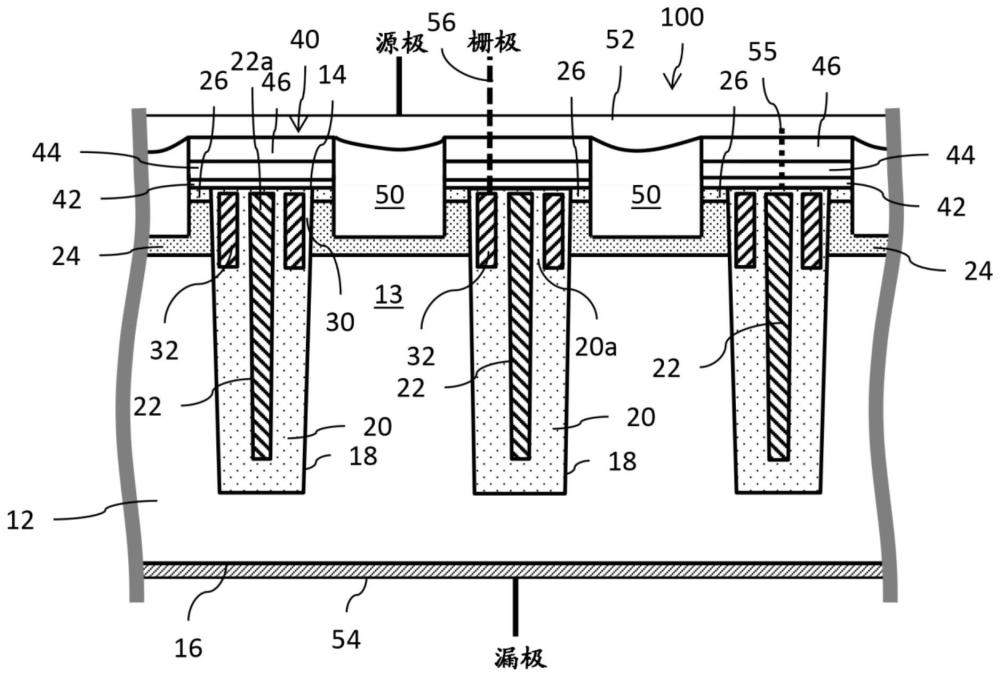

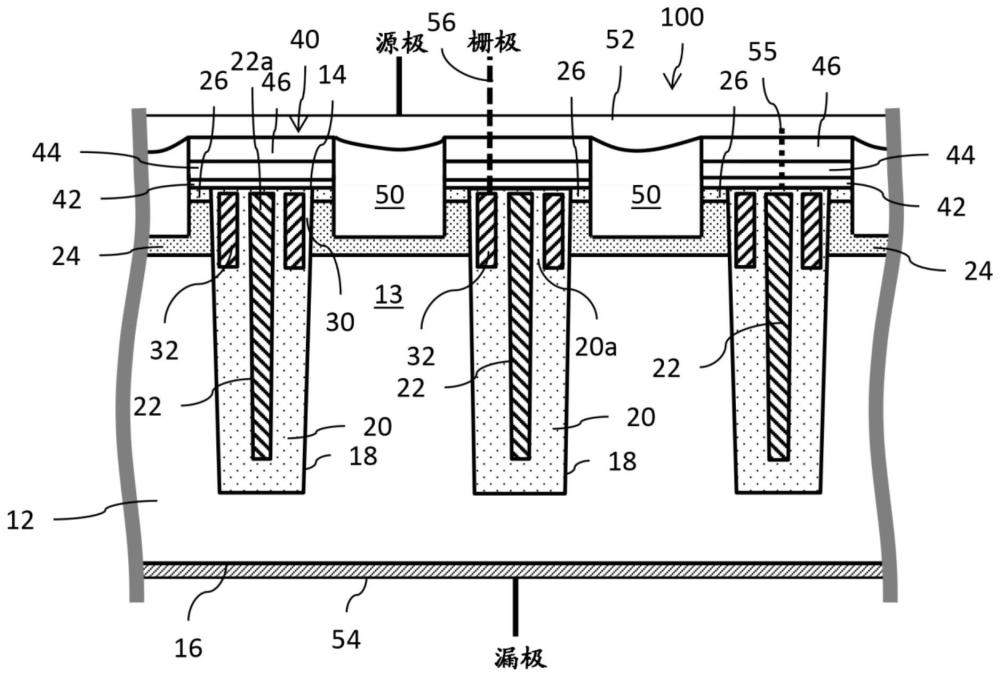

1、参考图1,图1示出了分裂栅沟槽功率金属氧化物半导体场效应晶体管(mosfet)器件10的截面的实施例。在该示例中,mosfet器件10是形成在半导体衬底12(例如,硅)中和上的n沟道(nmos)型晶体管,该半导体衬底掺杂有提供晶体管10的漏极区的n型掺杂剂。衬底12具有前侧14和后侧16。多个沟槽18从前侧14沿深度方向延伸到衬底12中。沟槽18在垂直于截面的方向上彼此平行地纵向延伸(即,进入和离开图示的页面),其中相邻沟槽界定形成条带的晶体管的台面(mesa)区13的侧边缘(此类型的晶体管器件在所属领域中通常称为条带fet型晶体管)。

2、掺杂有p型掺杂剂的区域24被掩埋在衬底12的台面区域13中,其深度从前侧14偏移(即,在下方),并且被定位成在每个沟槽18的相对侧上平行于前侧14延伸。掺杂区24形成晶体管的体(沟道)区,沟槽18完全穿过掺杂体区24并进入掺杂体区24下方的衬底12。用n型掺杂剂重掺杂的表面区域26被提供在衬底12的前侧14处的台面区域13中,并且被定位成在每个沟槽18的相对侧上平行于前侧14延伸并且与掺杂体区域24的顶部接触。掺杂区26形成晶体管的源极区,沟槽18完全穿过掺杂源极区26,并且如上所述,进一步完全穿过掺杂体区24延伸到掺杂体区24下方的衬底12中。

3、每个沟槽18的侧壁和底部加衬(lined)有第一绝缘层20。每个沟槽18由第一多晶硅材料22填充,第一绝缘层20使第一多晶硅材料22与衬底12绝缘。沟槽18中的第一多晶硅材料22形成晶体管10的场板电极。从沟槽18的上部去除第一绝缘层20的上部(例如,其将与掺杂体区24和掺杂区26两者相邻),以形成围绕第一多晶硅材料22的相应上部22a的环形沟槽。然后用第二绝缘层30a和第三绝缘层30b作为环形沟槽的侧壁(内侧和外侧)的加衬。例如,第二和第三绝缘层30a,30b可以各自包括氧化物层(在一个实施例中,其从每个环形沟槽中的衬底12的暴露表面和第一多晶硅材料22的上部22a的暴露表面热生长)。然后用第二多晶硅材料32填充每个环形沟槽的剩余开口部分。沟槽18的上部中的第二多晶硅材料32形成晶体管10的栅极。第二绝缘层30a使第二多晶硅材料(栅极)32与衬底12绝缘,并形成晶体管的栅极氧化物层。第三绝缘层30b使第二多晶硅材料(栅极)32与第一多晶硅材料(场板)22的上部22a绝缘,从而形成多晶硅间(interpoly)绝缘层。栅极氧化物层通常具有比多晶硅间绝缘层薄的厚度。

4、层的堆叠40形成在每个沟槽18上,并且在每个沟槽18的相对侧上在用于源极的掺杂区26的至少一部分上方横向延伸。每个堆叠40包括由未掺杂的氧化物(例如,原硅酸四乙酯(teos))层44和玻璃(例如,硼磷硅酸盐玻璃(bpsg))层46形成的电介质区。

5、源极金属接触50位于相邻堆叠40之间,以与每个掺杂源极区26电接触。每个源极金属接触50从前侧14沿深度方向延伸到衬底中,以穿过掺杂的源极区26并进入掺杂的体区24(从而为系接到源极的晶体管10提供体接触)。源极金属层52在堆叠40和源极金属接触50二者上延伸以提供到所有源极金属接触50的金属连接。堆叠40使源极金属层52和源极金属接触50与栅极(多晶硅区32)绝缘。提供电连接(未明确示出但由虚线55示意性示出)以将源极金属层52电连接到场板(多晶硅区22a)。漏极金属层54在衬底12的后侧16上延伸以提供到漏极的金属连接。栅极金属层(未明确示出,因为其在垂直于截面的方向上偏移)与每个沟槽18中的栅极(多晶硅区域32)形成电连接,该栅极金属层和电连接由虚线56示意性示出。

6、晶体管10也可以是pmos型晶体管,其中衬底12和掺杂源极区16都是p型掺杂的,而体区14是n型掺杂的。

7、图2a和图2b示出了晶体管10的单个单元的扫描电子显微照片(sem)截面图像。期望降低功率mosfet10的阈值电压。为了实现这一点,在沟槽18的上部(特别是在环形沟槽区域中)中由栅极(多晶硅区域32)与衬底12之间的第二绝缘层30a形成的栅极氧化物的厚度必须薄(例如,约)。随着栅极氧化物厚度的减小,阈值电压相应地从约3.5v减小到约1.75v。用于形成第二绝缘层30a的热氧化工艺不仅影响栅极氧化物的厚度,而且影响由第三绝缘层30b提供的在栅极(多晶硅区32)与场板电极(多晶硅区22)之间的多晶硅间隔离(interpoly isolation)。特别地,要关注的是,在提供薄的第二绝缘层30a以降低阈值电压时,在区域70中将存在第三绝缘层30b的相应变薄(例如,具有的厚度),其中此变薄的绝缘层30b导致弱的多晶硅-多晶硅(poly-to-poly)隔离。然后,晶体管10响应于栅极电压的施加而经历不可接受电平的栅极-源极漏电流(igss)。

8、因此,在本领域中需要一种改进的工艺来制造支持较低阈值电压同时继续满足栅极到源极漏电流要求的分裂栅极沟槽mosfet结构。

技术实现思路

1、在一个实施例中,一种方法包括:在半导体衬底中形成衬底沟槽;用第一绝缘层给衬底沟槽加衬;用通过所述第一绝缘层与所述半导体衬底绝缘的第一导电材料填充所述衬底沟槽;在所述第一绝缘层中形成栅极沟槽,所述栅极沟槽去除所述衬底沟槽的上部中与侧壁相邻的所述第一绝缘层的一部分,并将所述第一绝缘层的整体(integral)部分保留在围绕所述第一导电材料的适当位置;用第二绝缘层在所述栅极沟槽处给衬底沟槽的上部的侧壁加衬;以及在所述栅极沟槽中沉积第二导电材料,所述第二导电材料通过所述第二绝缘层与所述半导体衬底绝缘,并且第二导电材料通过所述第一绝缘层的所述整体部分与所述第一导电材料绝缘。

2、在一个实施例中,一种集成电路包括:具有前表面和后表面的半导体衬底;衬底沟槽,从前表面延伸到半导体衬底中,所述衬底沟槽包括下部和上部,所述上部与半导体衬底的前表面相邻;在所述衬底沟槽内的第一绝缘层;衬底沟槽中的第一导电材料,其通过所述第一绝缘层与半导体衬底绝缘;栅极沟槽,其在所述第一绝缘层中与所述衬底沟槽的上部中的侧壁相邻地延伸,所述栅极沟槽在所述衬底沟槽的上部处留下围绕所述第一导电材料的所述第一绝缘层的整体部分;以及在所述栅极沟槽中的第二导电材料,所述第二导电材料通过所述第二绝缘层与所述半导体衬底绝缘,并且通过所述第一绝缘层的所述整体部分与所述第一导电材料绝缘。

技术特征:1.一种方法,包括:

2.根据权利要求1所述的方法,进一步包括,在形成所述栅极沟槽之后并且在给所述侧壁加衬之前:

3.根据权利要求1所述的方法,进一步包括,在所述栅极沟槽中沉积所述第二导电材料之后:

4.根据权利要求3所述的方法,其中所述第三绝缘层是热氧化物。

5.根据权利要求3所述的方法,还包括在形成所述第三绝缘层之后,在所述第三绝缘层上形成氮化物层。

6.根据权利要求1所述的方法,其中所述第一导电材料和所述第二导电材料由多晶硅制成。

7.根据权利要求1所述的方法,其中所述第一绝缘层是氧化物,并且所述第二绝缘层是热氧化物。

8.根据权利要求1所述的方法,其中所述半导体衬底提供晶体管的漏极区,所述方法进一步包括:

9.根据权利要求8所述的方法,其中所述第一导电材料提供所述晶体管的场板电极,并且所述第二导电材料提供所述晶体管的栅极电极。

10.根据权利要求8所述的方法,进一步包括:

11.根据权利要求10所述的方法,其中所述第三导电材料提供用于所述晶体管的源极接触。

12.根据权利要求1所述的方法,其中形成所述栅极沟槽包括:

13.根据权利要求12所述的方法,进一步包括限定所述掩模的尺寸以提供围绕所述第一导电材料、并且具有在范围内的横向厚度的所述第一绝缘层的所覆盖的所述整体部分,并且其中所述第二绝缘层具有在范围内的厚度。

14.一种集成电路,包括:

15.根据权利要求14所述的集成电路,其中所述第一导电材料和所述第二导电材料各自由多晶硅制成。

16.根据权利要求14所述的集成电路,其中所述第一绝缘层是氧化物,并且所述第二绝缘层是热氧化物。

17.根据权利要求14所述的集成电路,其中所述半导体衬底提供晶体管的漏极区,所述集成电路进一步包括:

18.根据权利要求17所述的集成电路,其中所述第一导电材料提供所述晶体管的场板电极,并且所述第二导电材料提供所述晶体管的栅极电极。

19.根据权利要求17所述的集成电路,进一步包括:

20.根据权利要求19所述的集成电路,其中所述第三导电材料提供所述晶体管的源极接触。

21.根据权利要求15所述的集成电路,其中围绕所述第一导电材料的所述第一绝缘层的所述整体部分的横向厚度在范围内,并且其中所述第二绝缘层具有在范围内的厚度。

技术总结本公开涉及具有厚的多晶硅-多晶硅隔离的分裂栅极沟槽功率MOSFET。半导体衬底具有从前表面延伸并包括下部和上部的衬底沟槽。第一绝缘层衬在衬底沟槽上,第一导电材料通过第一绝缘层与半导体衬底绝缘以形成晶体管场板电极。第一绝缘层中的栅极沟槽限定第一绝缘层的整体部分,其围绕衬底沟槽的上部中的第一导电材料。第二绝缘层在栅极沟槽中的衬底沟槽的上部处衬在半导体衬底上。第二导电材料填充栅极。第二导电材料形成晶体管栅电极,该晶体管栅电极通过第二绝缘层与半导体衬底绝缘,并进一步通过第一绝缘层的整体部分与第一导电材料绝缘。

技术研发人员:阮文征,严俊荣,V·埃涅亚

受保护的技术使用者:意法半导体国际公司

技术研发日:技术公布日:2024/9/5