多层ITO芯片结构的制作方法

本发明涉及半导体发光器件领域,具体地说,尤其涉及一种多层ito芯片结构。

背景技术:

1、为了提高芯片的出光效率,通常采用ito作为透明导电层。ito是一种n型氧化物半导体材料,具有较高的导电率、可见光透过率、机械硬度和良好的化学稳定性,与其他透明的导电层相比,热稳定性以及化学稳定性更好,且对于衬底的附着性以及加工特性也更加适合。ito也是一种宽能带薄膜材料,在紫外光区产生的禁带的吸收阈值可到3.75ev,因此在紫外光区的ito薄膜的光穿透率极低,同时近红外区也由于载流子的等离子体共振现象而产生反射,所以近红外区ito薄膜的光穿透率也很低,导致芯片的发光性能及使用范围有待提升。因此对于芯片中ito结构的进一步优化以适配更多应用领域是十分重要的。如公告号为cn106548929b的一种近红外波段透射增强特性的ito基透明导电薄膜的制备方法,其采用ito膜上积cu膜的方式,但其结构并不适合应用于半导体发光器件领域。

技术实现思路

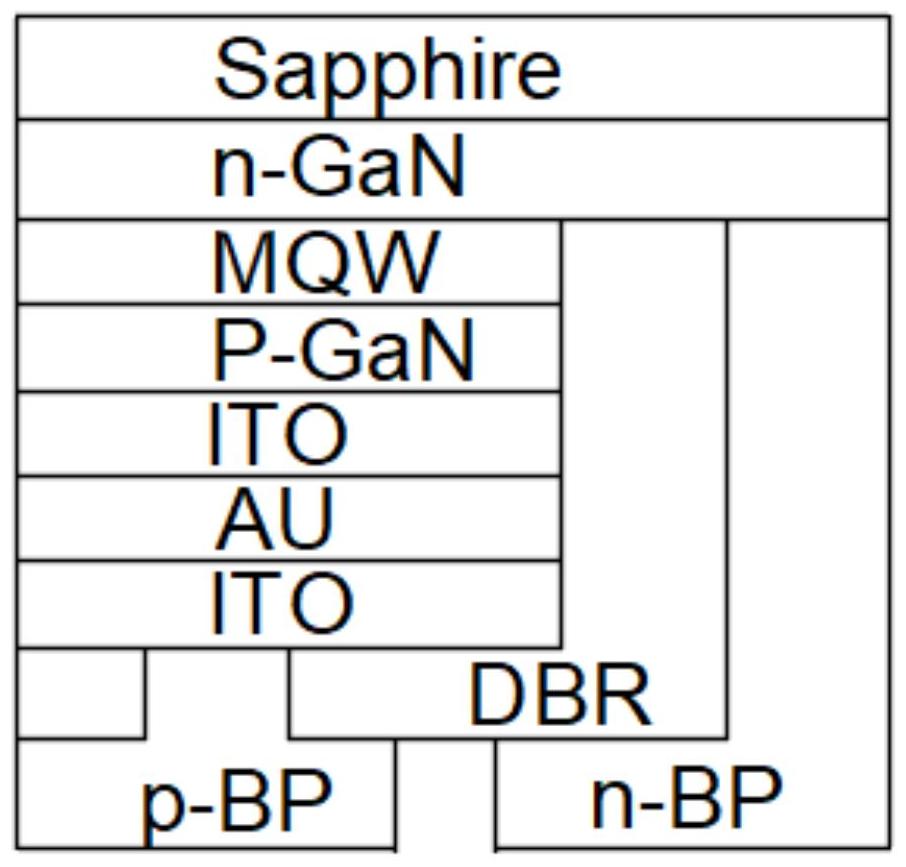

1、本发明的目的,在于提供一种多层ito芯片结构,其将原来的ito薄膜结构,转变为ito/au/ito的三层结构,采用贵金属au插层,可以改善ito的电性能和光性能,该结构可以将交叉波长从830nm提升至1490nm附近,大大提升了可应用产品领域及范围。

2、本发明是通过以下技术方案实现的:

3、一种多层ito芯片结构,包括如下步骤:

4、s1、制备外延片;

5、s2、蚀刻n型孔;

6、s3、沉积ito薄膜导电层;

7、s4、在沉积的ito薄膜导电层上进一步沉积au层;

8、s5、在沉积的au层上继续沉积ito薄膜导电层;

9、s6、制备n电极和p电极;

10、s7、沉积布拉格反射层;

11、s8、沉积金属连接层;

12、s9、芯片进行研磨、切割。

13、进一步地,外延片包括衬底、n-gan层、多量子阱及p-gan层,步骤s1中制备外延片包括如下步骤:

14、1)采用mocvd技术在2英寸的蓝宝石衬底上生长20nm-30nm的aln层,以及1μm-2μm未掺杂的gan,aln层作为缓冲层在衬底底部的生长更加剧烈,用于抑制衬底的纵向延伸,加强侧向生长,解决了gan之间因晶格失配而难以生长的问题;

15、2)在高温(1000℃-1100℃)、低压(50torr-150torr)的环境下生长si掺杂的n-gan以提供电子;生长13个周期gan/in0.05ga0.95n多量子阱结构来增加电子和空穴的空间重叠,以增加辐射复合率;

16、3)在900℃-1000℃和200torr-300torr的环境下生长一层宽带隙厚度在20nm-100nm的ebl层,ebl层作为电子阻挡层,将电子局限在量子阱区域内,以克服在大电流注入条件下电子溢出量子阱导致发光效率下降;

17、4)在900℃-1000℃和400torr-500torr的氮气环境下,生长厚度在150nm-250nm厚的mg掺杂的p-gan,形成p型半导体,为有源区提供空穴注入;

18、5)在低温(700℃-800℃)的氮气条件下生长一层薄的高浓度的p-gan层,以降低与电极间的欧姆接触,提高电流扩散。

19、进一步地,步骤s2中采用电感耦合等离子体(icp)刻蚀法,即用bcl3或cl2气体刻蚀n型孔,直到n-gan层暴露为止,由此达到去除n型电极区域的p型gan层的目的,使n型gan裸露出来。

20、进一步地,步骤s3中ito薄膜导电层采用磁控溅射的方法沉积,厚度在10nm-20nm,将衬底加热至中温(100℃-150℃)进行沉积,因为在中温下沉积的ito薄膜导电层会比在室温下的生长更好也更薄,会有更低的电阻率,从而使ito具有更好的电学性能。

21、进一步地,步骤s4中沉积au层采用磁控溅射的方法,au层纯度99.99%,厚度在1nm-5nm,在沉积过程中施加80w-100w的射频功率,来避免au材料的聚集,保证沉积超薄au层时,沉积的更加均匀。

22、进一步地,步骤s5中沉积ito薄膜导电层采用磁控溅射的方法沉积,厚度在10nm-20nm,将衬底加热至中温(100℃-150℃)进行沉积;在真空条件下旋转沉积,避免外界产生污染,保证沉积均匀且分散性好。

23、进一步地,制备n电极和p电极:通过沉积金属层作为n电极和p电极,金属层的层结构为:cr-al-ti-au-pt;对应的金属厚度为cr2.5nm、al120nm、ti35nm、au450nm、pt100nm。

24、进一步地,沉积布拉格反射层包括如下步骤:在芯片上采用离子束溅射的方法沉积10-20对sio2或tio2构成的分布式布拉格反射层,再用cf4/o2气体通过icp形成相应孔洞,去除电极表面的sio2的钝化层,为后续电极焊接留出空间。

25、进一步地,沉积金属连接层包括如下步骤:在p电极和n电极上分别沉积ti-ni金属连接层,ti厚度为30nm-50nm,ni厚度为250nm-350nm,ti层用于增加与p电极与n电极之间的粘附性;ni层用于增加与焊料之间的粘附性。

26、进一步地,芯片进行研磨、切割:对芯片研磨至晶圆厚度在50μm-150μm;芯片圆晶切割尺寸为100μm*200μm,完成芯片的制备。

27、与现有技术相比,本发明的有益效果是:

28、1.将超薄au层与ito组成多层结构,即ito/au/ito多层结构,au插层将很好的改善导电性能,同时au的插入,也会导致顶部的平均晶粒尺寸增加,而底部的ito层厚度不变,可以将交叉波长从可见范围的830nm提升至近红外的1490nm附近,大大提升了可应用产品领域及范围。

29、2.au插层改变ito结晶度,ito的透光率得到提高,同时也提高在可见光范围及近红外范围的应用,在进一步芯片的制备过程中,也将扩大芯片的应用市场。

30、综上,通过沉积超薄au层,构成ito/au/ito多层结构,利用贵金属au的高载流子密度和低电阻率相关优势,提升ito的洁晶度的同时提高ito的透光度以及其光电性能;同时贵金属在近红外部分有较强的等离子体共振效应,也可以进一步提升芯片在可见光以及近红外的应用范围,也可以提升芯片的应用市场。

技术特征:

1.一种多层ito芯片结构,其特征在于:包括如下步骤:

2.根据权利要求1所述的多层ito芯片结构,其特征在于:外延片包括衬底、n-gan层、多量子阱及p-gan层,步骤s1中制备外延片包括如下步骤:

3.根据权利要求1所述的多层ito芯片结构,其特征在于:步骤s2中用bcl3或cl2气体刻蚀n型孔,直到n-gan层暴露为止。

4.根据权利要求1所述的多层ito芯片结构,其特征在于:步骤s3中ito薄膜导电层采用磁控溅射的方法沉积,厚度在10nm-20nm,将衬底加热至100℃-150℃进行沉积。

5.根据权利要求1所述的多层ito芯片结构,其特征在于:步骤s4中沉积au层采用磁控溅射的方法,au层纯度99.99%,厚度在1nm-5nm,在沉积过程中施加80w-100w的射频功率,来避免au材料的聚集,保证沉积au层时,沉积的更加均匀。

6.根据权利要求1所述的多层ito芯片结构,其特征在于:步骤s5中沉积ito薄膜导电层采用磁控溅射的方法沉积,厚度在10nm-20nm,将衬底加热至100℃-150℃进行沉积;在真空条件下旋转沉积,避免外界产生污染,保证沉积均匀且分散性好。

7.根据权利要求1所述的多层ito芯片结构,其特征在于:制备n电极和p电极:通过沉积金属层作为n电极和p电极,金属层的层结构为:cr-al-ti-au-pt;对应的金属厚度为cr2.5nm、al120nm、ti35nm、au450nm、pt100nm。

8.根据权利要求1所述的多层ito芯片结构,其特征在于:沉积布拉格反射层包括如下步骤:在芯片上采用离子束溅射的方法沉积10-20对sio2或tio2构成的分布式布拉格反射层,再用cf4/o2气体通过icp形成相应孔洞,去除电极表面的sio2的钝化层,为后续电极焊接留出空间。

9.根据权利要求7所述的多层ito芯片结构,其特征在于:沉积金属连接层包括如下步骤:在p电极和n电极上分别沉积ti-ni金属连接层,ti厚度为30nm-50nm,ni厚度为250nm-350nm,ti层用于增加与p电极与n电极之间的粘附性;ni层用于增加与焊料之间的粘附性。

10.根据权利要求1所述的多层ito芯片结构,其特征在于:芯片进行研磨、切割:对芯片研磨至晶圆厚度在50μm-150μm;芯片圆晶切割尺寸为100μm*200μm,完成芯片的制备。

技术总结

本发明公开了一种多层ITO芯片结构,它属于半导体发光器件领域,其将原来的ITO薄膜结构,转变为ITO/Au/ITO的三层结构,采用贵金属Au插层,可以改善ITO的电性能和光性能,该结构可以将交叉波长从830nm提升至1490nm附近,大大提升了可应用产品领域及范围。它主要包括如下步骤:制备外延片;蚀刻n型孔;沉积ITO薄膜导电层;在沉积的ITO薄膜导电层上进一步沉积Au层;在沉积的Au层上继续沉积ITO薄膜导电层;制备n电极和p电极;沉积布拉格反射层;沉积金属连接层;芯片进行研磨、切割。本发明主要用于提高芯片的出光效率。

技术研发人员:朱帅,袁琳

受保护的技术使用者:湖南蓝芯微电子科技有限公司

技术研发日:

技术公布日:2024/5/29

- 还没有人留言评论。精彩留言会获得点赞!