沟槽终端结构的小型化高压平面VDMOS及其制造方法与流程

本发明涉及半导体,具体涉及一种沟槽终端结构的小型化高压平面vdmos及其制造方法。

背景技术:

1、现有mosfet、igbt等功率器件,高电场的强度往往会集中在器件的终端层域,这可能会导致器件的局部过热,绝缘层击穿以及电荷集中等问题,功率器件终端是衡量器件反向耐压能力和可靠性的关键结构。

2、目前现有的功率vdmos结终端保护技术主要有场板(fp)、场限环(flr)、结终端扩展(jte)以及横向变掺杂(vld)等。多数公司常使用fp和flr组合的方案去改善器件表面击穿特性;场板可以有效地抑制表面电荷引起的低击穿,场限环则可以减缓平面结曲率效应造成的pn结击穿。p+分压环、多晶场板和金属场板相结合的复合终端结构是现有vdmos终端设计较为成熟的方案。

3、现有vdmos终端结构是场板-场限环复合结构;每个场限环上的场板几乎都覆盖了整个环之间的空间,这样的好处是减小了场板边缘上的电场峰值,但对于结深较小的vdmos而言,各环之间的距离较近场板覆盖区域过大会增加光刻难度,同时硅片有效面积利用率降低,进而导致芯片面积增大,成本提高,且提升了工艺控制难度。

技术实现思路

1、本发明的目的是针对现有技术存在的不足,提供一种沟槽终端结构的小型化高压平面vdmos及其制造方法。

2、为实现上述目的,在第一方面,本发明提供了一种沟槽终端结构的小型化高压平面vdmos的制造方法,包括:

3、提供第一导电类型的衬底,并在所述衬底的上侧制作外延层;

4、在终端区的外延层上刻蚀形成两个以上的沟槽,所述沟槽的宽由内向外依次减小;

5、在所述沟槽下侧的外延层内注入第二导电类型的元素,然后进行退火操作,以形成环区,所有沟槽下侧的环区连接为一个整体;

6、在所述沟槽内侧及外延层的上侧生长氧化层;

7、在所述沟槽内及其上端外侧的外延层上制作形成介电层;

8、将有源区的氧化层刻蚀掉,然后对有源区的外延层进行jfet注入和jfet退火操作,以形成第一导电类型的jfet区;

9、在有源区的外延层和介电层上侧生长栅氧化层,并在所述栅氧化层的上侧沉积多晶硅,然后依次对所述多晶硅进行注入和刻蚀操作,以形成第二导电类型的有源区多晶硅和截止环多晶硅;

10、在所述有源区多晶硅四周的外延层内和截止环多晶硅外侧的外延层内制作第二导电类型的第一掺杂区,并在所述第一掺杂区内制作第一导电类型的第二掺杂区;

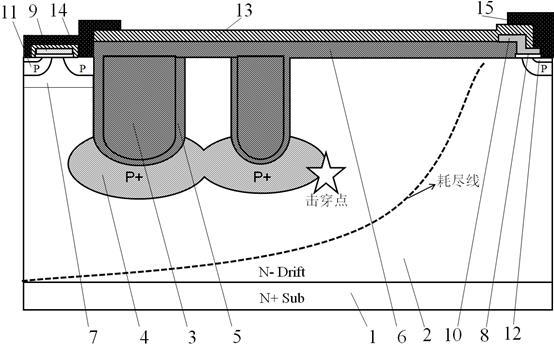

11、沉积形成介质层,并在所述介质层上刻蚀出连接孔;

12、在所述介质层的上侧及连接孔内溅射形成金属层,所述金属层经刻蚀形成源极金属、栅极金属和截止环金属。

13、进一步的,所述沟槽的深度为10μm,位于最内侧的沟槽的宽度为6-12μm,非最内侧的沟槽的宽度为其内侧沟槽宽度的三分之二,相邻的两个沟槽的间距为4-8μm。

14、进一步的,所述第一导电类型为n型,所述第二导电类型为p型。

15、进一步的,所述环区通过注入硼元素形成,注入的剂量为2e12-1e13 atom/cm3,注入的能量为40-80kev,退火温度为1150℃,时间为150-300min。

16、进一步的,所述介电层经旋涂工艺填充,并经425℃、2-3小时的硬化处理,然后通过回刻工艺形成。

17、在第二方面,本发明提供了一种沟槽终端结构的小型化高压平面vdmos,包括第一导电类型的衬底,所述衬底的上侧设有外延层,在终端区的外延层上设有两个以上的沟槽,所述沟槽的宽由内向外依次减小,在所述沟槽下侧的外延层内设有第二导电类型的环区,所有沟槽下侧的环区连接为一个整体,在所述沟槽内侧设有氧化层,在所述沟槽内及其上端外侧的外延层上设有介电层,在有源区的外延层内经jfet注入和jfet退火操作形成第一导电类型的jfet区,在有源区的外延层和介电层上侧设有栅氧化层,所述栅氧化层的上侧设有第二导电类型的有源区多晶硅和截止环多晶硅,在所述有源区多晶硅四周的外延层内和截止环多晶硅外侧的外延层内设有第二导电类型的第一掺杂区,在所述第一掺杂区内设有第一导电类型的第二掺杂区,还包括介质层,所述介质层上设有连接孔,所述介质层的上侧及连接孔内设有金属层,所述金属层经刻蚀形成源极金属、栅极金属和截止环金属。

18、进一步的,所述沟槽的深度为10μm,位于最内侧的沟槽的宽度为6-12μm,非最内侧的沟槽的宽度为其内侧沟槽宽度的三分之二,相邻的两个沟槽的间距为4-8μm。

19、进一步的,所述第一导电类型为n型,所述第二导电类型为p型。

20、进一步的,所述环区通过注入硼元素形成,注入的剂量为2e12-1e13 atom/cm3,注入的能量为40-80kev,退火温度为1150℃,时间为150-300min。

21、进一步的,所述介电层经旋涂工艺填充,并经425℃、2-3小时的硬化处理,然后通过回刻工艺形成。

22、有益效果:本发明通过在终端区域刻蚀沟槽,并进行注入和填充,形成沟槽和环区结构,使用氧化层结构承担横向电压,并且使终端区的纵向耗尽更加充分,从而提高终端耐压效率;在相同耐压的情况下,可有效减少终端宽度,缩小管芯尺寸;与常规vdmos工艺流程兼容,用沟槽刻蚀替代ring注入,不增加光刻层数,工艺具有可行性。

技术特征:

1.沟槽终端结构的小型化高压平面vdmos的制造方法,其特征在于,包括:

2.根据权利要求1所述的沟槽终端结构的小型化高压平面vdmos的制造方法,其特征在于,所述沟槽的深度为10μm,位于最内侧的沟槽的宽度为6-12μm,非最内侧的沟槽的宽度为其内侧沟槽宽度的三分之二,相邻的两个沟槽的间距为4-8μm。

3.根据权利要求1所述的沟槽终端结构的小型化高压平面vdmos的制造方法,其特征在于,所述第一导电类型为n型,所述第二导电类型为p型。

4.根据权利要求3所述的沟槽终端结构的小型化高压平面vdmos的制造方法,其特征在于,所述环区通过注入硼元素形成,注入的剂量为2e12-1e13 atom/cm3,注入的能量为40-80kev,退火温度为1150℃,时间为150-300min。

5.根据权利要求1所述的沟槽终端结构的小型化高压平面vdmos的制造方法,其特征在于,所述介电层经旋涂工艺填充,并经425℃、2-3小时的硬化处理,然后通过回刻工艺形成。

6.沟槽终端结构的小型化高压平面vdmos,其特征在于,包括第一导电类型的衬底,所述衬底的上侧设有外延层,在终端区的外延层上设有两个以上的沟槽,所述沟槽的宽由内向外依次减小,在所述沟槽下侧的外延层内设有第二导电类型的环区,所有沟槽下侧的环区连接为一个整体,在所述沟槽内侧设有氧化层,在所述沟槽内及其上端外侧的外延层上设有介电层,在有源区的外延层内经jfet注入和jfet退火操作形成第一导电类型的jfet区,在有源区的外延层和介电层上侧设有栅氧化层,所述栅氧化层的上侧设有第二导电类型的有源区多晶硅、栅区多晶硅和截止环多晶硅,在所述有源区多晶硅四周的外延层内和截止环多晶硅外侧的外延层内设有第二导电类型的第一掺杂区,在所述第一掺杂区内设有第一导电类型的第二掺杂区,还包括介质层,所述介质层上设有连接孔,所述介质层的上侧及连接孔内设有金属层,所述金属层经刻蚀形成源极金属、栅极金属和截止环金属。

7.根据权利要求6所述的沟槽终端结构的小型化高压平面vdmos,其特征在于,所述沟槽的深度为10μm,位于最内侧的沟槽的宽度为6-12μm,非最内侧的沟槽的宽度为其内侧沟槽宽度的三分之二,相邻的两个沟槽的间距为4-8μm。

8.根据权利要求6所述的沟槽终端结构的小型化高压平面vdmos,其特征在于,所述第一导电类型为n型,所述第二导电类型为p型。

9.根据权利要求8所述的一种沟槽终端结构的小型化高压平面vdmos,其特征在于,所述环区通过注入硼元素形成,注入的剂量为2e12-1e13 atom/cm3,注入的能量为40-80kev,退火温度为1150℃,时间为150-300min。

10.根据权利要求6所述的一种沟槽终端结构的小型化高压平面vdmos,其特征在于,所述介电层经旋涂工艺填充,并经425℃、2-3小时的硬化处理,然后通过回刻工艺形成。

技术总结

本发明公开了一种沟槽终端结构的小型化高压平面VDMOS及其制造方法。该方法包括提供第一导电类型的衬底,并在衬底的上侧制作外延层;在终端区的外延层上刻蚀形成两个以上的沟槽,沟槽的宽由内向外依次减小;在沟槽下侧的外延层内注入第二导电类型的元素,然后进行退火操作,以形成环区,所有沟槽下侧的环区连接为一个整体。本发明通过在终端区域刻蚀沟槽,并进行注入和填充,形成沟槽和环区结构,使用氧化层结构承担横向电压,并且使终端区的纵向耗尽更加充分,从而提高终端耐压效率;在相同耐压的情况下,可有效减少终端宽度,缩小管芯尺寸;与常规VDMOS工艺流程兼容,用沟槽刻蚀替代Ring注入,不增加光刻层数,工艺具有可行性。

技术研发人员:李加洋,王晨晖,胡兴正,薛璐

受保护的技术使用者:南京华瑞微集成电路有限公司

技术研发日:

技术公布日:2024/6/2

- 还没有人留言评论。精彩留言会获得点赞!