半导体器件及其制备方法与流程

本发明涉及半导体,尤其涉及一种半导体器件及其制备方法。

背景技术:

1、半导体器件在现代电子技术领域有着重要的应用,相应的对半导体器件的性能以及成本要求也越来越高。

2、然而,现有的半导体器件的击穿电压较低,限制了半导体器件的进一步应用。

技术实现思路

1、本发明提供了一种半导体器件及其制备方法,以提高半导体器件的击穿电压。

2、根据本发明的一方面,提供了一种半导体器件,所述半导体器件包括:

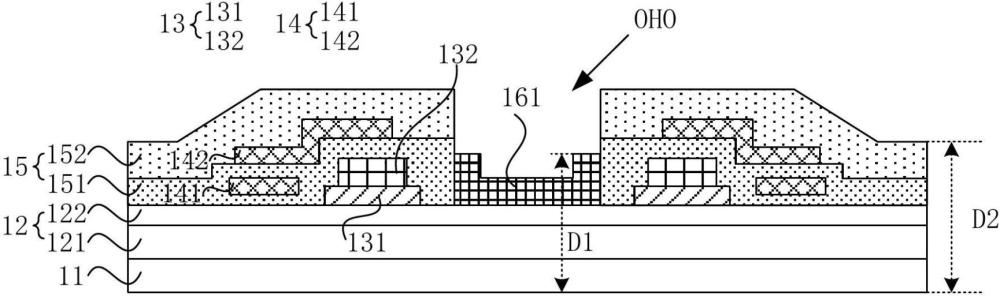

3、衬底、外延结构、栅极结构、介质层及欧姆接触结构;

4、所述外延结构设置于所述衬底上,所述栅极结构设置于所述外延结构远离所述衬底的一面;所述介质层覆盖所述栅极结构;

5、所述介质层形成有开孔,所述开孔暴露所述外延结构;所述欧姆接触结构设置于所述开孔内且沿所述开孔的内壁延伸。

6、可选地,沿所述半导体器件的厚度方向,所述欧姆接触结构远离所述衬底的一面与所述衬底的最大距离,小于或等于所述介质层远离所述衬底的一面与所述衬底的最小距离。

7、可选地,所述外延结构包括依次层叠于所述衬底上的第一氮化物半导体层和第二氮化物半导体层;所述第一氮化物半导体层与所述第二氮化物半导体层具有不同的带隙。

8、可选地,所述半导体器件还包括栅极场板,所述栅极场板设置于所述介质层中。

9、根据本发明的另一方面,提供了一种半导体器件的制备方法,用于制备如上所述的半导体器件,所述半导体器件的制备方法包括:

10、于衬底上形成外延结构;

11、于所述外延结构上形成栅极结构、介质层以及暴露所述外延结构的开孔;

12、形成覆盖所述介质层及所述开孔的内壁的欧姆层;

13、形成覆盖所述欧姆层并填充所述开孔的刻蚀阻挡层;

14、利用减薄工艺减薄所述刻蚀阻挡层,其中,减薄后的所述刻蚀阻挡层位于所述开孔内且暴露所述开孔外的欧姆层;

15、以减薄后的所述刻蚀阻挡层为掩膜,图形化所述欧姆层形成欧姆接触结构。

16、可选地,所述减薄工艺包括asher工艺。

17、可选地,所述利用减薄工艺减薄所述刻蚀阻挡层包括:

18、控制所述减薄工艺的预设参数,以使减薄后的所述刻蚀阻挡层远离所述衬底的一面与所述衬底的距离,小于或等于所述欧姆层远离所述衬底的一面与所述衬底的最小距离。

19、可选地,所述利用减薄工艺减薄所述刻蚀阻挡层还包括:

20、定时监控减薄后的所述刻蚀阻挡层的厚度。

21、可选地,所述于所述外延结构上形成栅极结构、介质层以及暴露所述外延结构的开孔包括:

22、于所述外延结构上形成至少两个栅极结构;

23、形成覆盖所述栅极结构的介质层;

24、形成贯穿所述介质层并暴露所述外延结构的所述开孔。

25、可选地,所述图形化所述欧姆层形成欧姆接触结构之后还包括:

26、去除残留的所述刻蚀阻挡层;

27、于所述开孔内形成电极。

28、可选地,所述形成覆盖所述欧姆层并填充所述开孔的刻蚀阻挡层包括:

29、涂布光刻胶以形成所述刻蚀阻挡层。

30、本发明实施例的技术方案,采用的半导体器件包括衬底、外延结构、栅极结构、介质层及欧姆接触结构;外延结构设置于衬底上,栅极结构设置于外延结构远离衬底的一面;介质层覆盖栅极结构;介质层形成有开孔,开孔暴露外延结构;欧姆接触结构设置于开孔内且沿开孔的内壁延伸。将欧姆接触层仅限定在开孔内,使得介质层对应开孔边缘的部分没有残留的欧姆耳朵结构,从而不会产生欧姆耳朵结构与其他金属结构之间的寄生电容,因而不会扰乱半导体器件内的电场分布,可以使得半导体器件的击穿电压较高。

31、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种半导体器件,其特征在于,所述半导体器件包括:

2.根据权利要求1所述的半导体器件,其特征在于,沿所述半导体器件的厚度方向,所述欧姆接触结构远离所述衬底的一面与所述衬底的最大距离,小于或等于所述介质层远离所述衬底的一面与所述衬底的最小距离。

3.根据权利要求1所述的半导体器件,其特征在于,所述外延结构包括依次层叠于所述衬底上的第一氮化物半导体层和第二氮化物半导体层;所述第一氮化物半导体层与所述第二氮化物半导体层具有不同的带隙。

4.根据权利要求1所述的半导体器件,其特征在于,所述半导体器件还包括栅极场板,所述栅极场板设置于所述介质层中。

5.一种半导体器件的制备方法,用于制备权利要求1-4任一项所述的半导体器件,其特征在于,所述半导体器件的制备方法包括:

6.根据权利要求5所述的半导体器件的制备方法,其特征在于,所述减薄工艺包括asher工艺。

7.根据权利要求5所述的半导体器件的制备方法,其特征在于,所述利用减薄工艺减薄所述刻蚀阻挡层包括:

8.根据权利要求7所述的半导体器件的制备方法,其特征在于,所述利用减薄工艺减薄所述刻蚀阻挡层还包括:

9.根据权利要求5所述的半导体器件的制备方法,其特征在于,所述于所述外延结构上形成栅极结构、介质层以及暴露所述外延结构的开孔包括:

10.根据权利要求5所述的半导体器件的制备方法,其特征在于,所述图形化所述欧姆层形成欧姆接触结构之后还包括:

11.根据权利要求5所述的半导体器件的制备方法,其特征在于,所述形成覆盖所述欧姆层并填充所述开孔的刻蚀阻挡层包括:

技术总结

本发明公开了一种半导体器件及其制备方法。所述半导体器件包括:衬底、外延结构、栅极结构、介质层及欧姆接触结构;所述外延结构设置于所述衬底上,所述栅极结构设置于所述外延结构远离所述衬底的一面;所述介质层覆盖所述栅极结构;所述介质层形成有开孔,所述开孔暴露所述外延结构;所述欧姆接触结构设置于所述开孔内且沿所述开孔的内壁延伸。本发明的半导体器件具有较高的击穿电压。

技术研发人员:韩晨彬,倪景华,余仁旭,周绍珂,徐磊

受保护的技术使用者:英诺赛科(苏州)半导体有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!